'gen_amba' is a set of programs that generate AMBA bus Verilog-HDL, which include AMBA AXI, AMBA AHB, and AMBA APB.

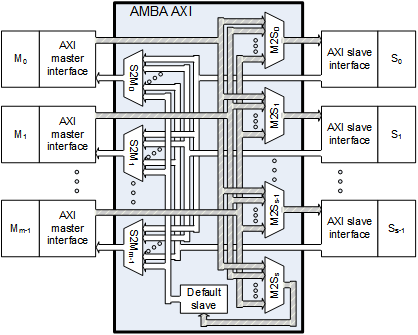

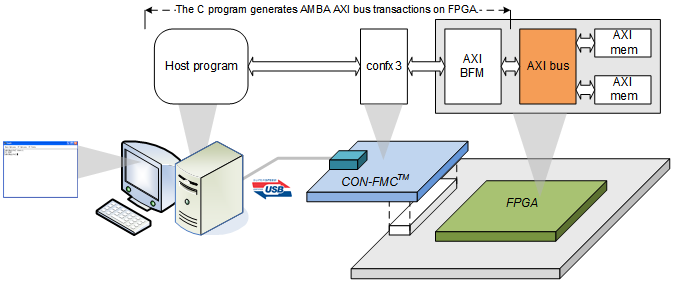

- gen_amba_axi: AMBA AXI bus generator for multi-master and multi-slave

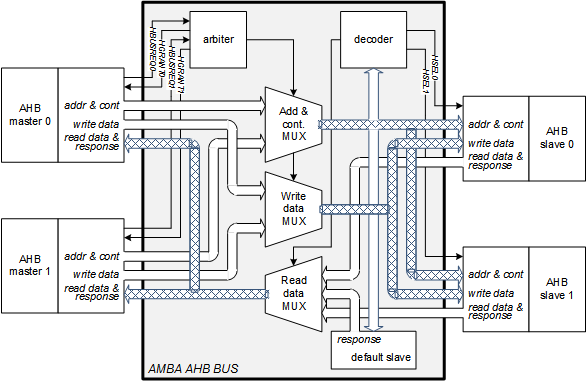

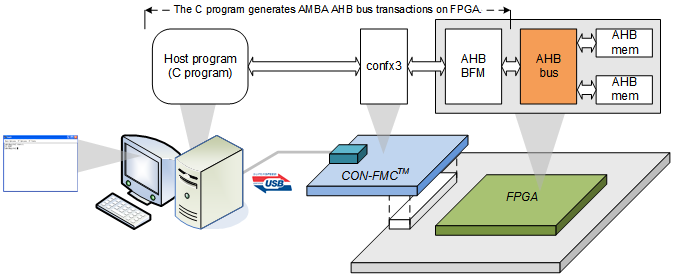

- gen_amba_ahb: AMBA AHB bus generator for multi-master and multi-slave

- gen_amba_apb: AMBA APB bus-bridge generator for AMBA AXI or AHB

Note that there is a new version of this project that is 'gen_amba_2021' (https://github.com/adki/gen_amba_2021).

This is licensed with the 2-clause BSD license to make the program and library useful in open and closed source products independent of their licensing scheme.

This program requires followings.

- Shell: Bash

- GNU GCC: C compiler

- HDL simulator: Mentor Graphics ModelSim or icarus Verilog

- RTL simulation

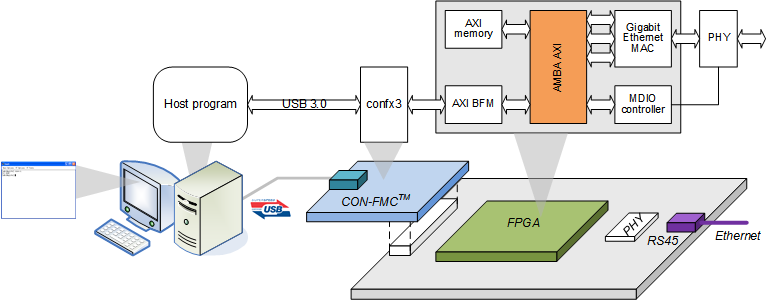

- FPGA proven (refer to CON-FMC)

- ASIC partially proven, but not whole yet

- go to 'gen_amba_axi' directory

$ cd gen_amba_axi - run Makefile

$ make cleanup

$ make

. It should generate 'gen_amba_axi'. - have a look the help message

$ ./gen_amba_axi -h - generate AMBA AXI

$ ./gen_amba_axi --mst=2 --slv=3 --out=amba_axi_m2s3.v

. It generates an AXI bus ("amba_axi_m2s3.v") with 2 master-ports and 3 slave-ports.

- go to 'gen_amba_axi/verification/sim/modelsim' directory

$ cd gen_amba_axi/verification/sim/modelsim

. Use 'iverilog' for Icarus Verilog. - run Makefile

$ make cleanup

$ make MST=2 SLV=3

. It should generate necessary bus and top model and then invoke ModelSim simulator.

. It uses top-level generator. - have a look the result VCD wave

$ gtkwave wave.vcd

- go to 'gen_amba_ahb' directory

$ cd gen_amba_ahb - run Makefile

$ make cleanup

$ make

. It should generate 'gen_amba_ahb'. - have a look the help message

$ ./gen_amba_ahb -h - generate AMBA AHB

$ ./gen_amba_ahb --mst=2 --slv=3 --out=amba_ahb_m2s3.v

. It generates an AHB bus ("amba_ahb_m2s3.v") with 2 master-ports and 3 slave-ports.

- go to 'gen_amba_ahb/verification/sim/modelsim' directory

$ cd gen_amba_ahb/verification/sim/modelsim

. Use 'iverilog' for Icarus Verilog. - run Makefile

$ make cleanup

$ make MST=2 SLV=3

. It should generate necessary bus and top model and then invoke ModelSim simulator.

. It uses top-level generator. - have a look the result VCD wave

$ gtkwave wave.vcd

There is AMBA bus generator for each bus.

It generates AMBA AXI switch.

Click to expand

$ ./gen_amba_axi -h

[Usage] ./gen_amba_axi [options]

-m,--mst=num num of masters (default: 2)

-s,--slv=num num of slaves (default: 2)

-d,--mod=str module name (default: "amba_axi_mXsY")

-p,--pre=str prefix of module (default: none)

-o,--out=file output file name (stdout if not given)

-v,--ver=num verbose level (default: 0)

-l,--lic print license message

-h print help message

It generates AMBA AHB bus.

Click to expand

$ ./gen_amba_ahb -h

[Usage] ./gen_amba_ahb [options]

-t,--lite AMBA AHB-lite

-m,--mst=num num of masters (default: 2)

-s,--slv=num num of slaves (default: 2)

-d,--mod=str module name (default: "amba_ahb_mXsY")

-p,--pre=str prefix of module

-o,--out=file output file name (stdout if not given)

-v,--ver=num verbose level (default: 0)

-l,--lic print license message

-h print help message

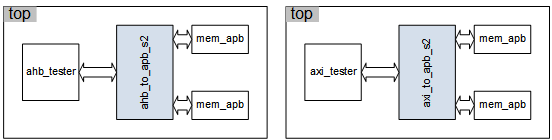

It generates AMBA APB bus bridge for AHB or AXI.

Click to expand

$ ./gen_amba_apb -h

[Usage] ./gen_amba_apb [options]

--axi|ahb make "axi_to_apb" or "ahb_to_apb" (apb if not given)

-s,--slv=num num of APB ports (default: 2)

-d,--mod=str module name (default: "axi_to_apb_sX" or "ahb_to_apb_sX")

-p,--pre=str prefix of sub-module name (none if not given)

-o,--out=file output file name (stdout if not given)

-v,--ver=num verbose level (default: 0)

-l,--lic print license message

-h print help message

There is top-level generator for each bus in 'verification' directory.

- go to 'gen_amba_axi/verification'

$ cd gen_amba_axi/verification - have a look the help message

$ ./gen_axi_top.sh -h - generate a top-level

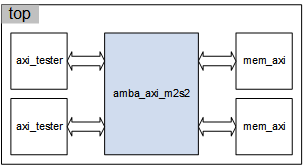

$ ./gen_axi_top.sh -mst 2 -slv 2 -siz 1024 -out top.v

. It generates a top-level verilog ("top.v") supporting two AXI masters and two AXI memories.

. Each memory takes care of 1Kbyte range of memory; i.e., memory0 covers 0-1023 and memory1 covers 1024-2047.

Click to expand

$ ./gen_axi_top.sh -h

Usage : ./gen_axi_top.sh [options]

-mst num :num of masters, 2

-slv num :num of slaves, i.e., memories, 2

-siz bytes :size of each slave in bytes, 1024

-bus module :name of bus,

-out file_name :output file name, top.v

-h/-? :printf help

- go to 'gen_amba_hb/verification'

$ cd gen_amba_ahb/verification - have a look the help message

$ ./gen_ahb_top.sh -h - generate a top-level

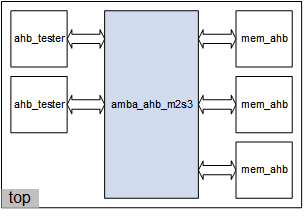

$ ./gen_ahb_top.sh -mst 2 -slv 2 -siz 1024 -out top.v

. It generates a top-level verilog ("top.v") supporting two AXI masters and two AXI memories.

. Each memory takes care of 1Kbyte range of memory; i.e., memory0 covers 0-1023 and memory1 covers 1024-2047.

Click to expand

$ ./gen_ahb_top.sh -h

Usage : ./gen_ahb_top.sh [options]

-mst num :num of masters, 2

-slv num :num of slaves, i.e., memories, 2

-siz bytes :size of each slave in bytes, 1024

-bus module :name of bus,

-out file_name :output file name, top.v

-h/-? :printf help

- go to 'gen_amba_apb/verification'

$ cd gen_amba_apb/verification - have a look the help message

$ ./gen_apb_top.sh -h - generate a top-level

$ ./gen_apb_top.sh -ahb -slv 2 -siz 1024 -out top.v

. It generates a top-level verilog ("top.v") supporting AHB masters and two APB memories.

. Each memory takes care of 1Kbyte range of memory; i.e., memory0 covers 0-1023 and memory1 covers 1024-2047.

Click to expand

$ ./gen_apb_top.sh -h

Usage : ./gen_apb_top.sh [options]

-ahb|axi :AHB or AXI master: ahb

-slv num :num of slaves, i.e., memories, 2

-siz bytes :size of each slave in bytes, 1024

-bus module :name of bus,

-out file_name :output file name, top.v

-h/-? :printf help

The author has been giving open lecture on AMBA bus at following two institutes.

- IDEC (IC Design Education Center) at KAIST: https://www.idec.or.kr

- SW-SoC Academy at ETRI: https://www.asic.net

6.1 Future Design Systems CON-FMCTM project

- Ando Ki - Initial work - Future Design Systems