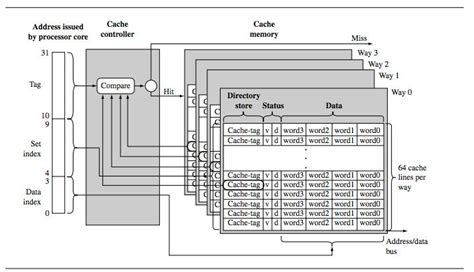

A modular and customizable set associative cache.

Developed to be implemented into my 32 bit risc v core. This implementation of set associative will use a simple relative LRU algorithm. Metadata is kept simple, with single bits: VALID, DIRTY, LRU (excluding tag). Cache parameters can be manimpulated for custom caches. Write back, write-allocate:

• On read and write misses, the line is brought into the cache

• On writes, you only update the cache and set the dirty bit to 1

This project was started to add a more practical cache implementation to my risc v pipeline. The intended use for the cache is a 4 way set association, 256 cache lines, 18 tag bits, 64 byte cache lines, and 32 bit addresses and data. This implementation allows for writing to memory, but could also be used as a read only/ instruction cache.

In the set-associative cache, the memory address consists of three parts: the tag, index, and offset. These components help determine the location of the data within the cache. When there is a cache miss and the cache needs to fetch data from main memory, the cache address is used to construct the main memory address.

Here's a breakdown of the components in a memory address for a set-associative cache:

Tag:

The tag bits uniquely identify a particular block of data within a set.

The tag bits are used to check if the requested data is present in the cache.

Index:

The index bits determine which set within the cache the data belongs to.

It helps in selecting the set where the data should be stored or retrieved.

Offset:

The offset bits specify the position of the data within the cache block.

It indicates the location of the data within the selected cache line.

When there's a cache miss, the cache controller extracts the tag, index, and offset from the cache address. The index is used to identify the set in the cache, and the tag is compared with the tags in that set to check if the required data is present. If it's a miss, the cache controller constructs the main memory address using the tag, index, and offset bits.

The main memory address construction is done as follows:

Combine Tag and Index:

Concatenate the tag and index bits to form the main memory address.

This address is used to access the set in main memory where the required data is stored.

Add Offset:

Add the offset to the constructed main memory address to specify

the exact location within the block in main memory where the data is stored.

This main memory address is then used to initiate a request to the main memory subsystem to fetch the required data. Once the data is fetched, it is brought into the cache, and subsequent accesses to the same address can be served from the cache until the data is evicted or invalidated.

What things you need to install the software and how to install them.

Give examples

A step by step series of examples that tell you how to get a development env running.

Say what the step will be

Give the example

And repeat

until finished

End with an example of getting some data out of the system or using it for a little demo.

Explain how to run the automated tests for this system.

Explain what these tests test and why

Give an example

Explain what these tests test and why

Give an example

Add notes about how to use the system.

Verify iverilog and gtkwave are installed and run the following commands from root:

cd run

source run_cache.csh

- Verilog 2012 - Language

- Icarus Verilog - Compiler

- GTKWave - Waveform Simulator

- YoSys - Synthesis Suite

- @sprsr - Design and Verification

- Open Source EDA Tools

- Risc V Org

- Onur Mutlu (Computer Architecture lectures on Youtube)