To design and implement half adder and full adder circuit using Verilog HDL and verify its truth table.

- Laptop with Quartus software and modelsim software.

Adders are digital circuits that carry out addition of numbers.

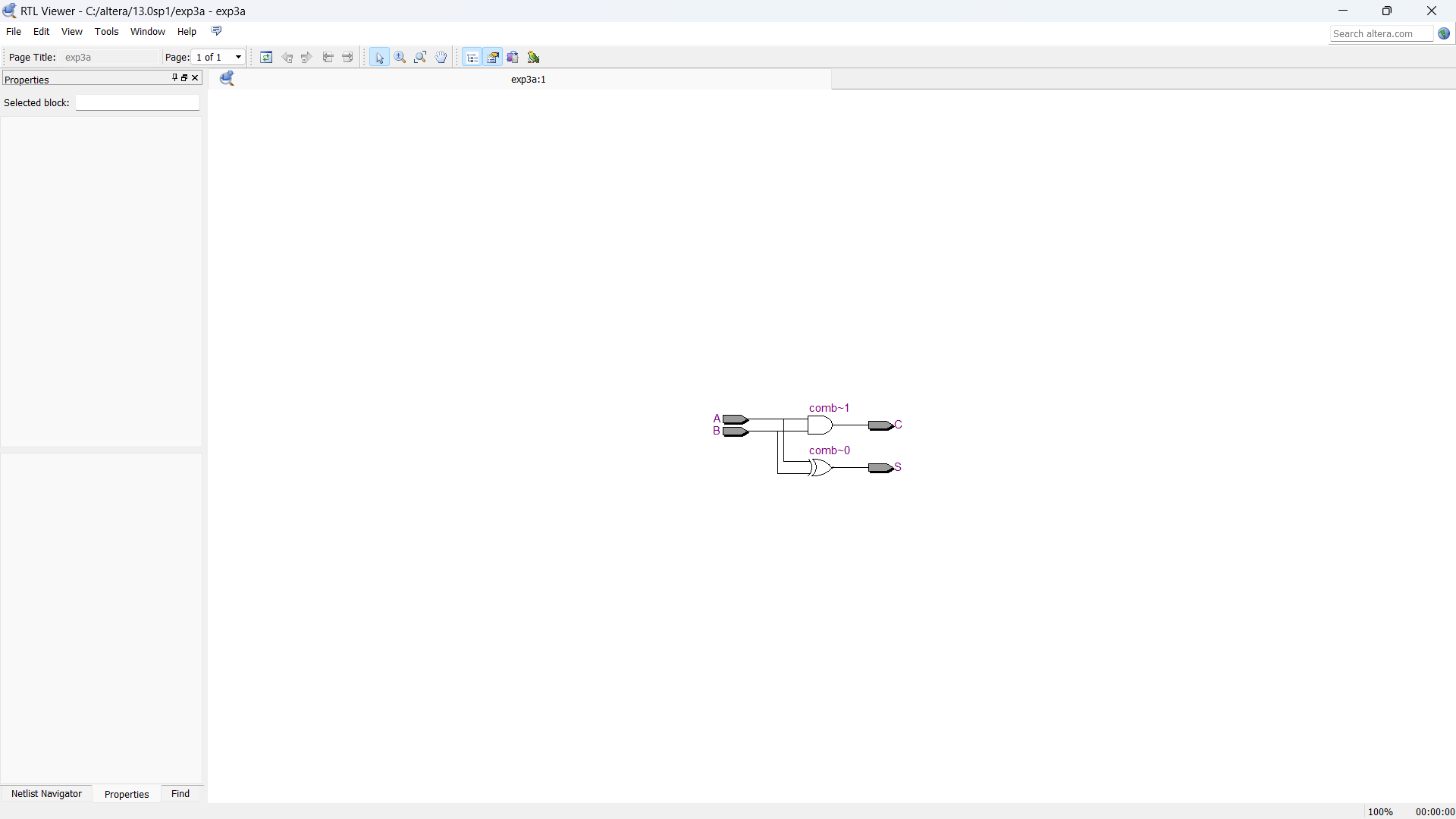

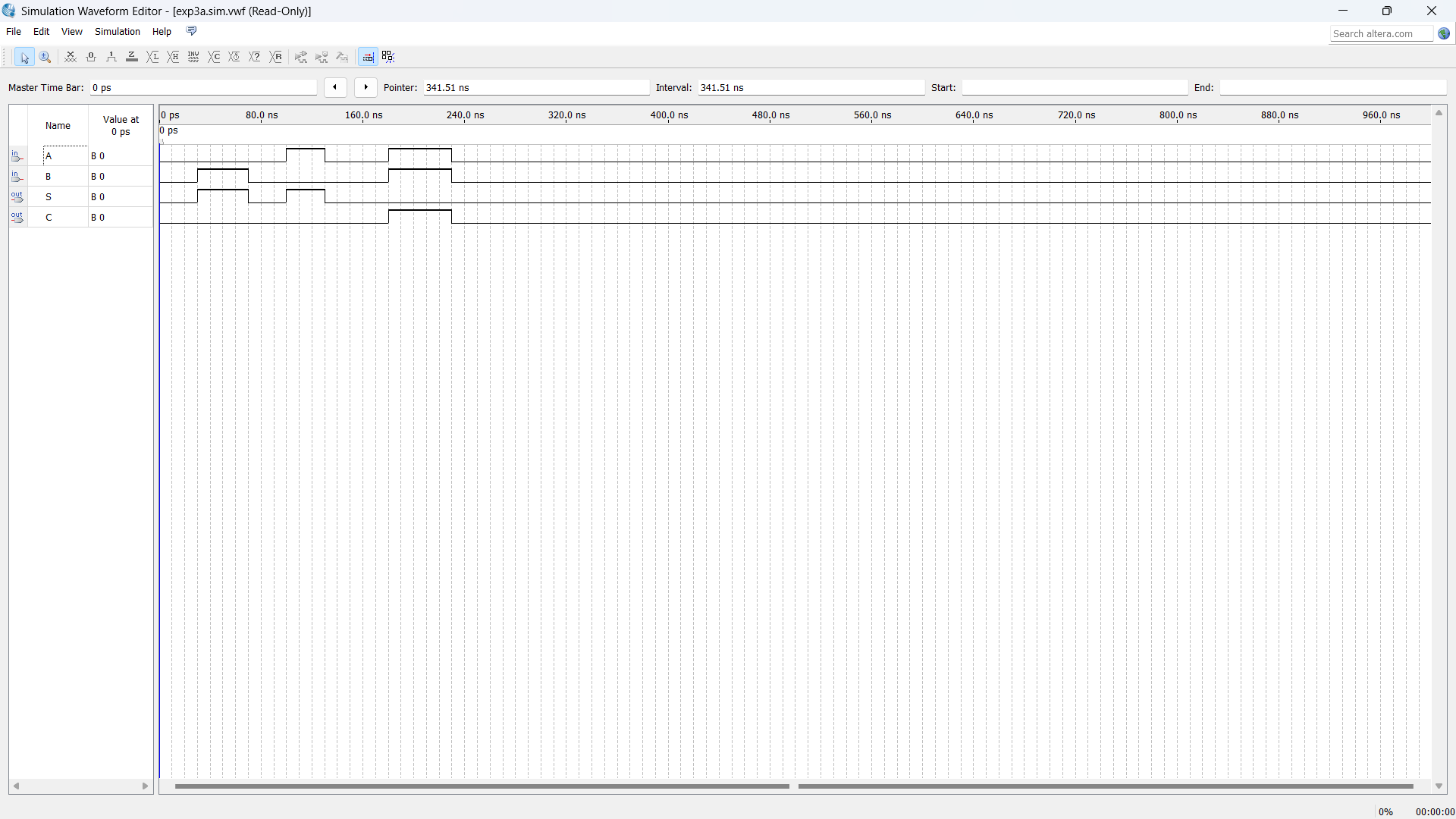

Half adder is a combinational circuit that performs simple addition of two binary numbers. The input variables designate the augend and addend bits; the output variables produce the sum and carry. It is necessary to specify two output variables because the result may consist of two binary digits.

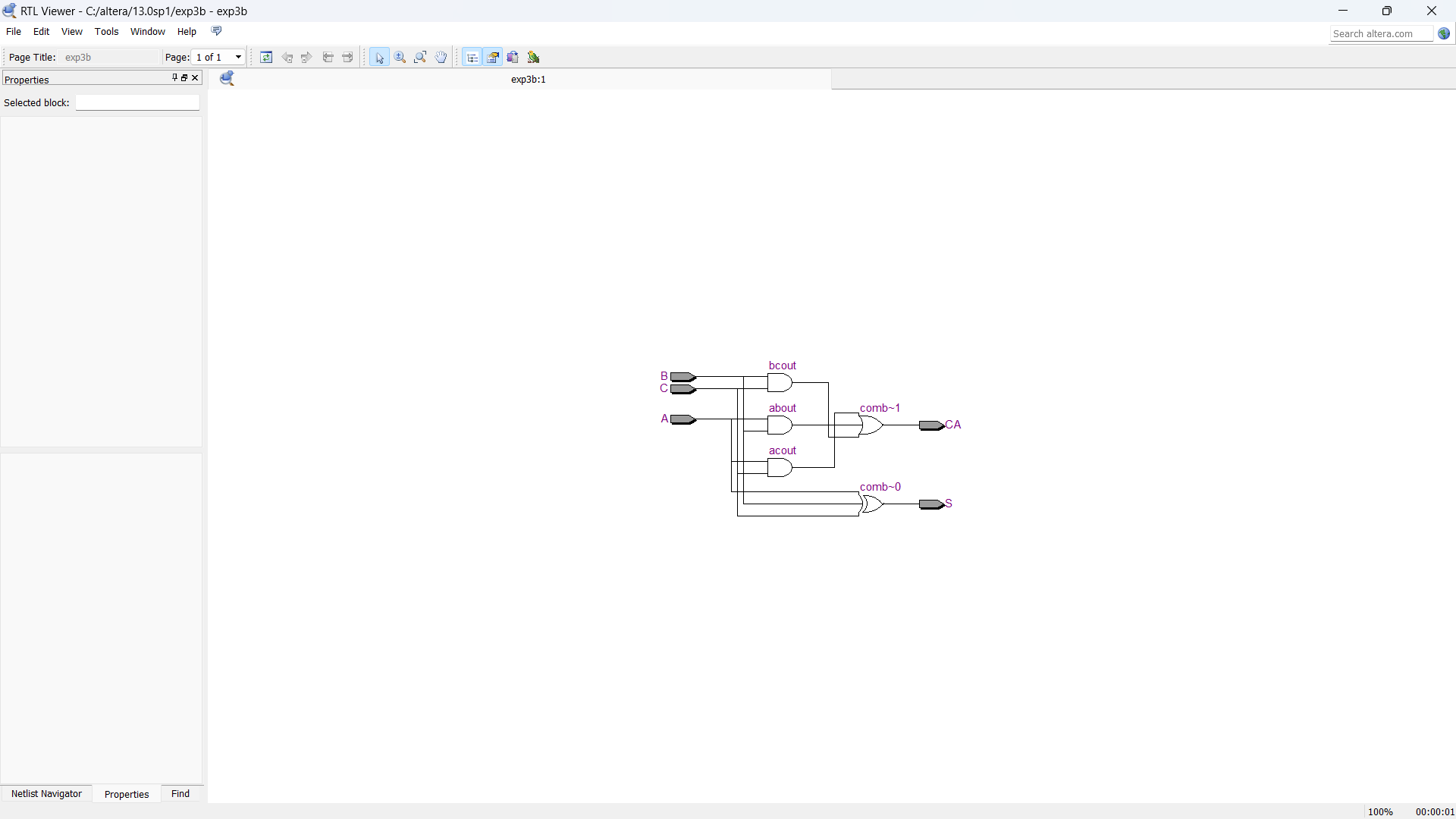

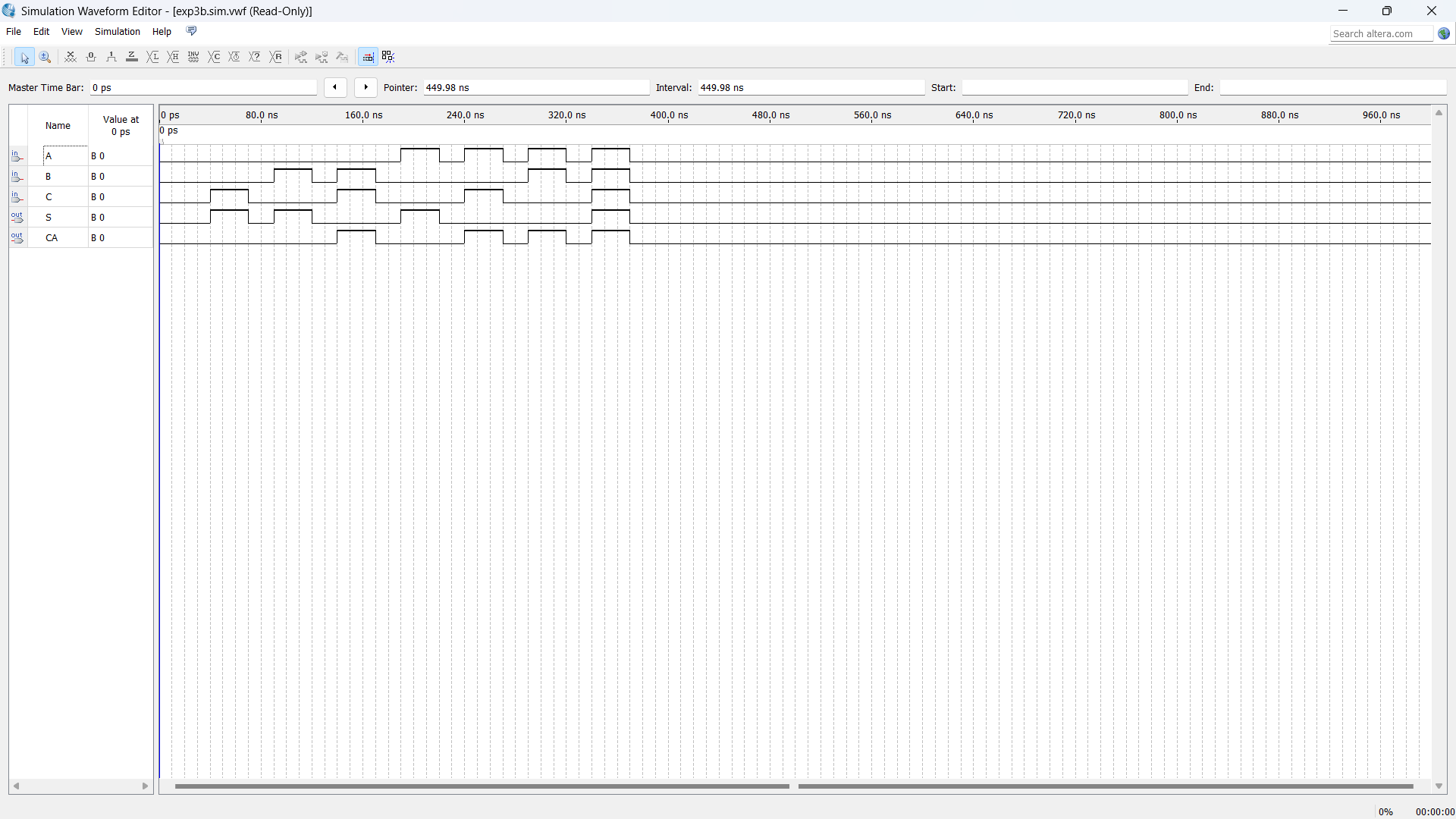

Full adder is a digital circuit used to calculate the sum of three binary bits. It consists of three inputs and two outputs. Two of the input variables, denoted by A and B, represent the two significant bits to be added. The third input, Cin, represents the carry from the previous lower significant position. Two outputs are necessary because the arithmetic sum of three binary digits ranges in value from 0 to 3, and binary 2 or 3 needs two digits. The two outputs are sum and carry.

Sum =A’B’Cin+A’BCin’+ABCin+AB’Cin’=A  B

B  Cin

Carry = AB + ACin+BCin

Cin

Carry = AB + ACin+BCin

- Type the program in Quartus software.

- Compile and run the program.

- Generate the RTL schematic and save the logic diagram.

- Create nodes for inputs and outputs to generate the timing diagram.

- For different input combinations, generate the timing diagram.

module exp3a(A,B,S,C);

input A,B;

output S,C;

xor(S,A,B);

and(C,A,B);

endmodule

module exp3b(A,B,C,S,CA);

input A,B,C;

output S,CA;

wire bc,acout,bcout,about,baout;

xor(bc,B,C);

xor(S,A,bc);

and(acout,A,C);

and(about,A,B);

and(bcout,B,C);

or(baout,bcout,about);

or(CA,acout,baout);

endmodule

Thus the half adder and full adder circuits are designed and implemented and the truth tables are verified.