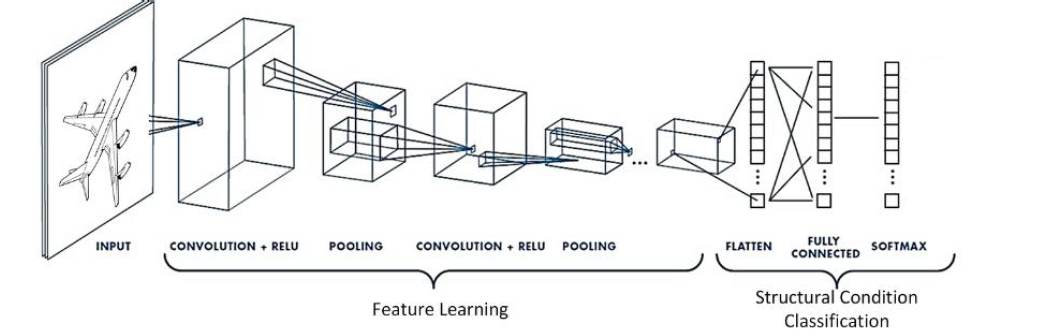

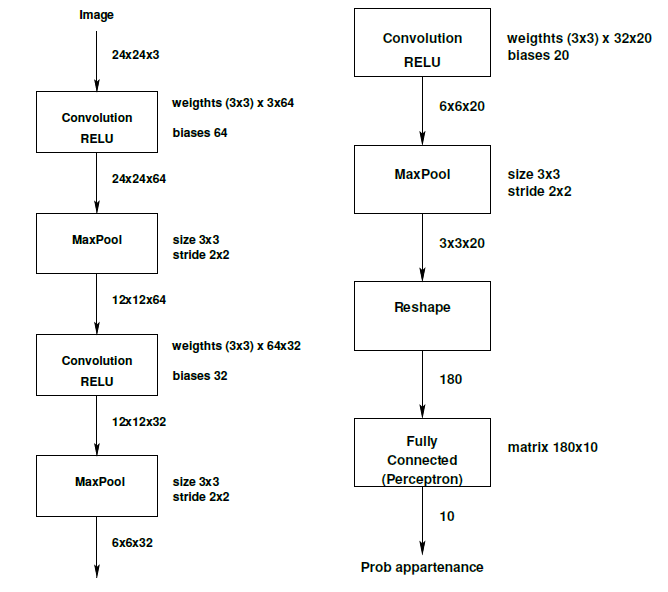

This project concerns the implementation of a neural network (CIFAR-10 dataset) on an FPGA. It is divided into three (03) parts:

- Part 1: Implementation of the network in Python to establish a baseline.

- Part 2: Floating-point (double) implementation in C++.

- Part 3: C++ fixed-point implementation (ac_fixed).

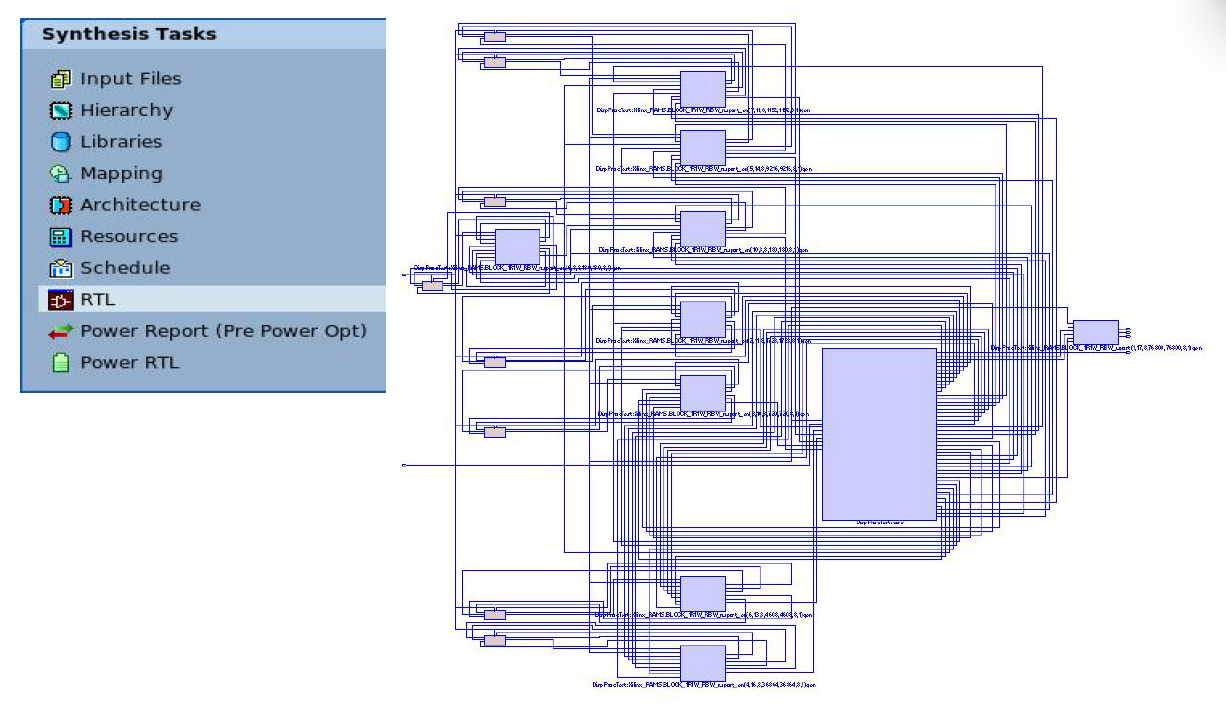

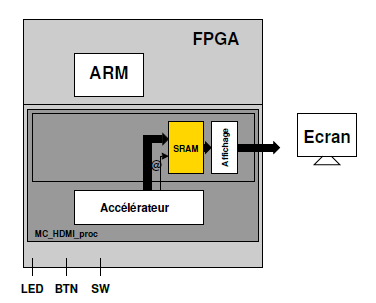

We use High Level Synthesis with Mentor Graphics CatapultC to perform the high-level synthesis of our code to generate the RTL code. Once the RTL code has been generated, we use the Precision tool to perform formal hardware verification. This tool is used to check the conformity of a hardware design with certain specifications or to detect potential errors in the design.

The outpput of Precision is used by Vivado to generate the bitstream to be loaded onto the FPGA board. We use a prototyping platform based on the following scheme:

-

Python

python top.py

-

Cpp_reference

make all ./top_cnn_reference

-

Cpp_hardware

make all ./top_cnn_hardware