This free mini-workshop, offered by by Steve Hoover of Redwood EDA, LLC, Linux Foundation, and RISC-V International is a crash course in digital logic design and basic CPU microarchitecture. Using the Makerchip online integrated development environment (IDE), you’ll implement everything from logic gates to a simple, but complete, RISC-V CPU core. You’ll be amazed by what you can do using freely-available online tools for open-source development. You’ll walk away with fundamental skills for a career in logic design, and you’ll position yourself on the forefront by learning to use the emerging Transaction-Level Verilog language extension (even if you don’t already know Verilog).

This course is available in this repository as well as via the EdX platform (with a certification option). Thousands have registered and/or completed this course, including Claude (Anthropic's AI chatbot):

If I were an actual student, I would give you glowing ratings as an instructor!

--Claude

Do a git clone of this repo and then run these commands to install and use local makerchip:

pipx install makerchip-app

pipx inject makerchip-app setuptools

makerchip <file>

Congratulations for taking this step to expand your knowledge of computer hardware.

At this time, there are no course corrections or platform issues to report. Please do let us know within the EdX platform if anything gets in your way. There's a great deal of infrastructure to maintain for the course, and we aim to keep it all running smoothly. Now, please head back to EdX or the Markdown version of this course and continue.

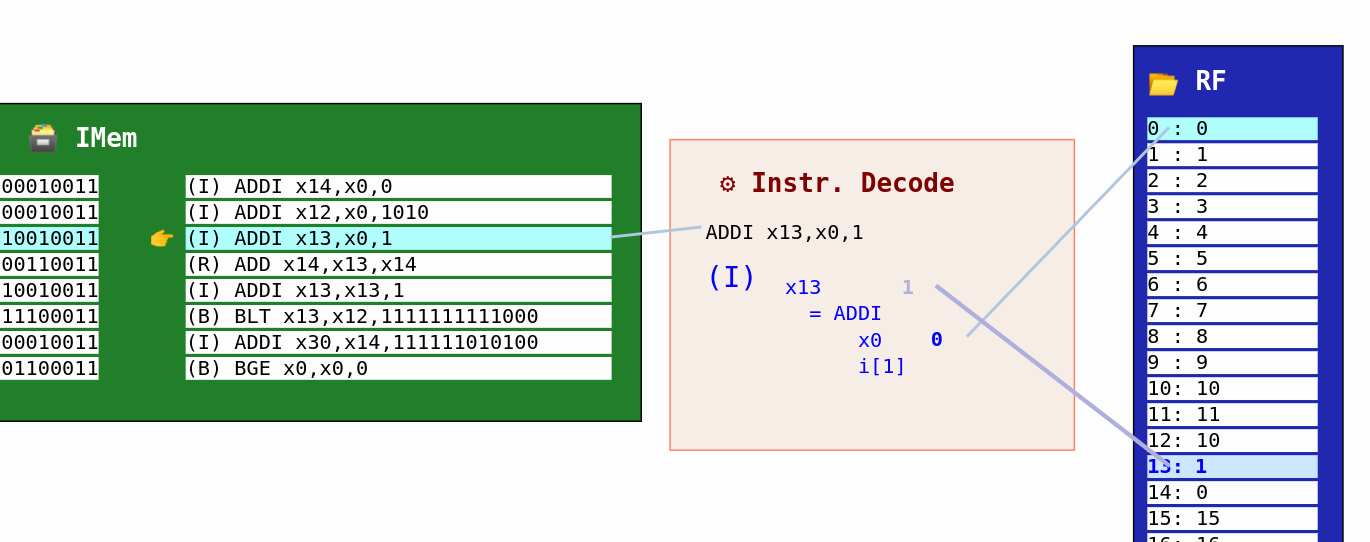

To begin the first RISC-V lab, when instructed to do so, Ctrl-click this link to open starting-point code in makerchip.

In case you get stuck, we've got your back! These reference solutions (Ctrl-click) will help with syntax, etc. without handing you the answers.

Here's a pre-built logic diagram of the final CPU. Ctrl-click here to explore in its own tab.

Congratulations!!!

After completing this course, we hope you are inspired to continue your journey. These ideas might help:

- Try the tutorials in Makerchip.

- Learn more about TL-Verilog.

- Explore the RISC-V ecosystem.

- Take other courses from Linux Foundation

- Discover other training from Redwood EDA, LLC

- Get your core running on real hardware using FPGAs in the cloud or on your desktop.

- Install TL-Verilog tools.

- Learn about the WARP-V TL-Verilog CPU core generator.