Copyright(c) 2022-

Author: Chaitanya Tejaswi (github.com/CRTejaswi) License: GPL v3.0+

FPGA: Floating Pt Square-Root

32bit integer square-root (restoring divison) & 32bit floating-pt square-root (newton-raphson) implementations on FPGA.

Implementations

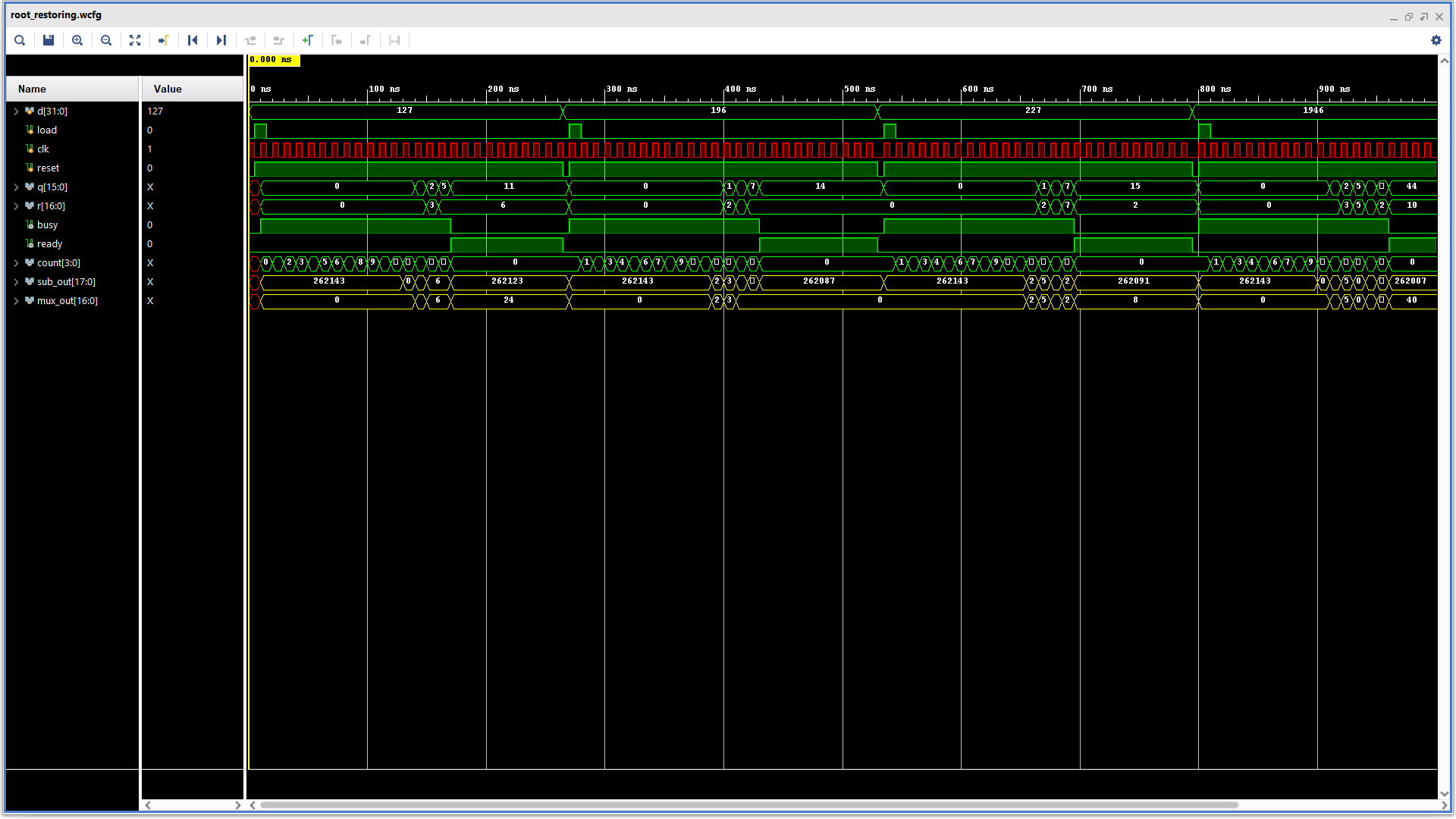

v1: 32bit integer sqrt:

Documentation: 📄

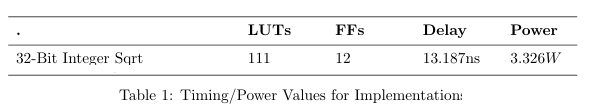

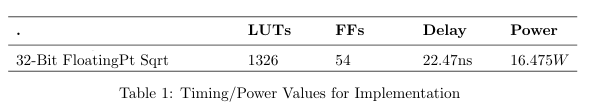

Reports: timing, power

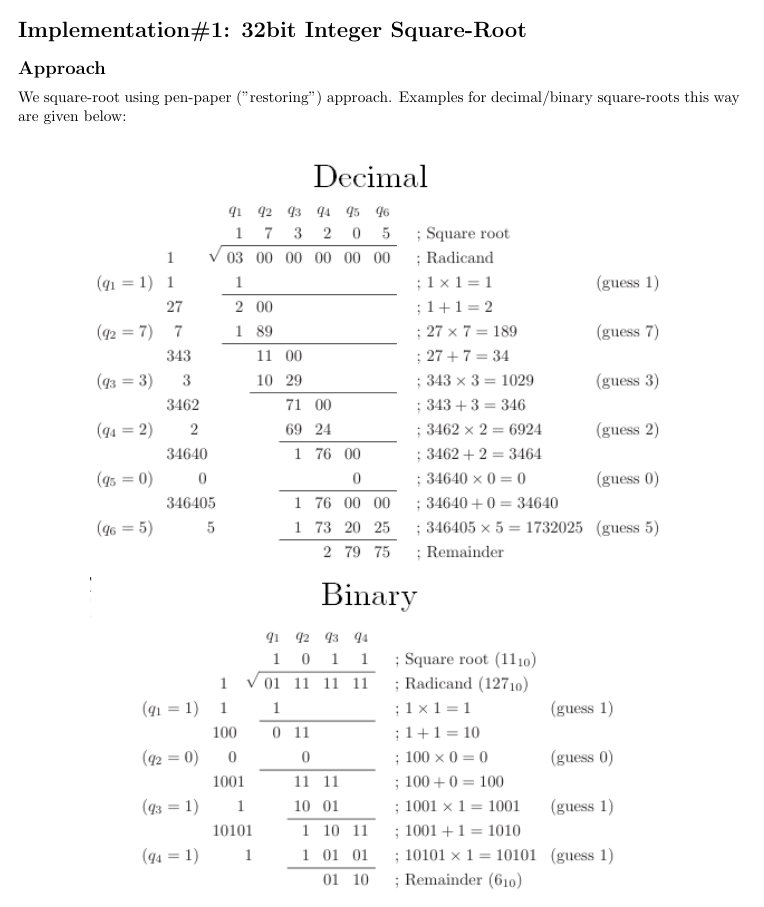

Approach:

Results

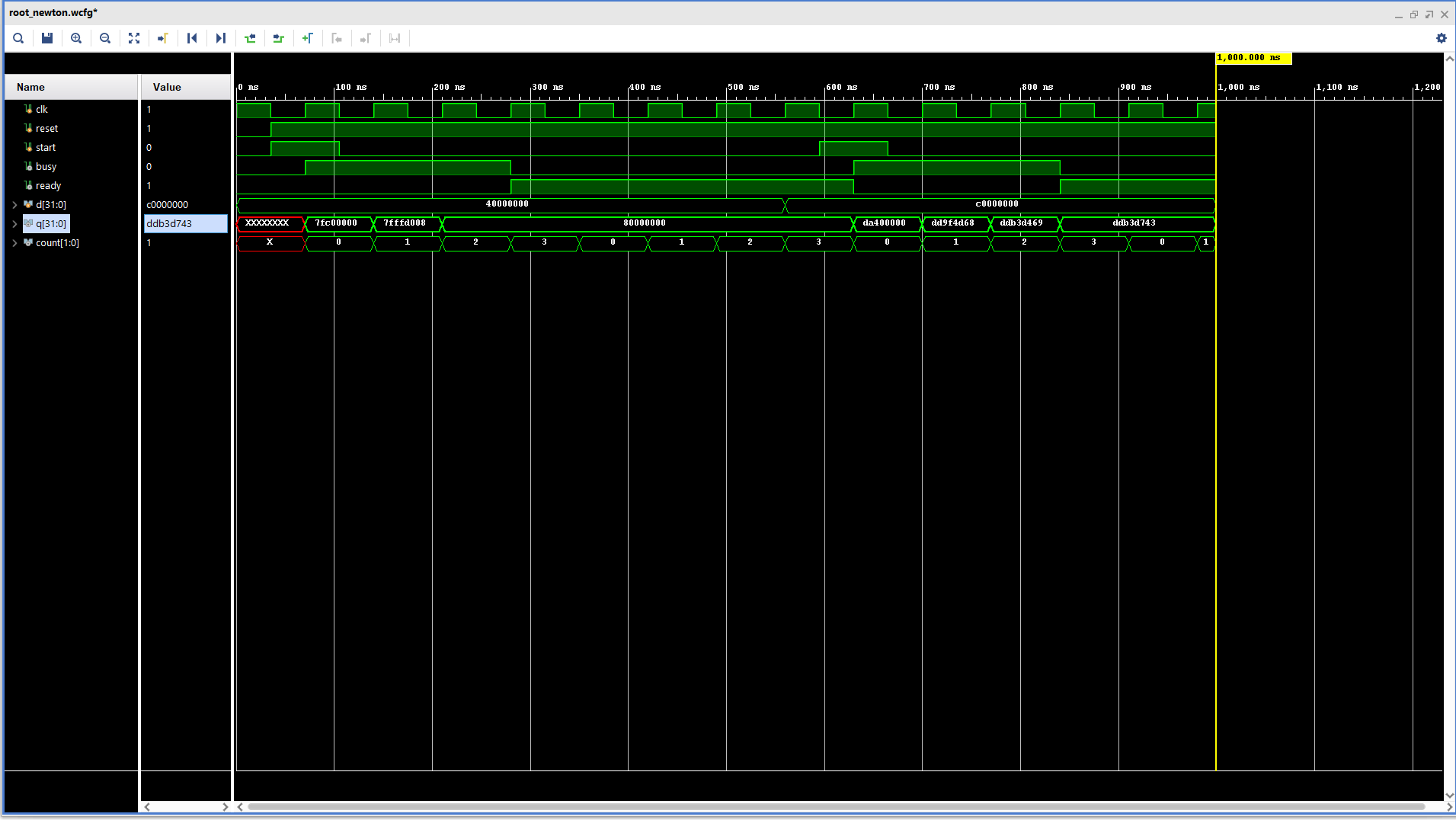

v2: 32bit floating-pt: :

Documentation: 📄

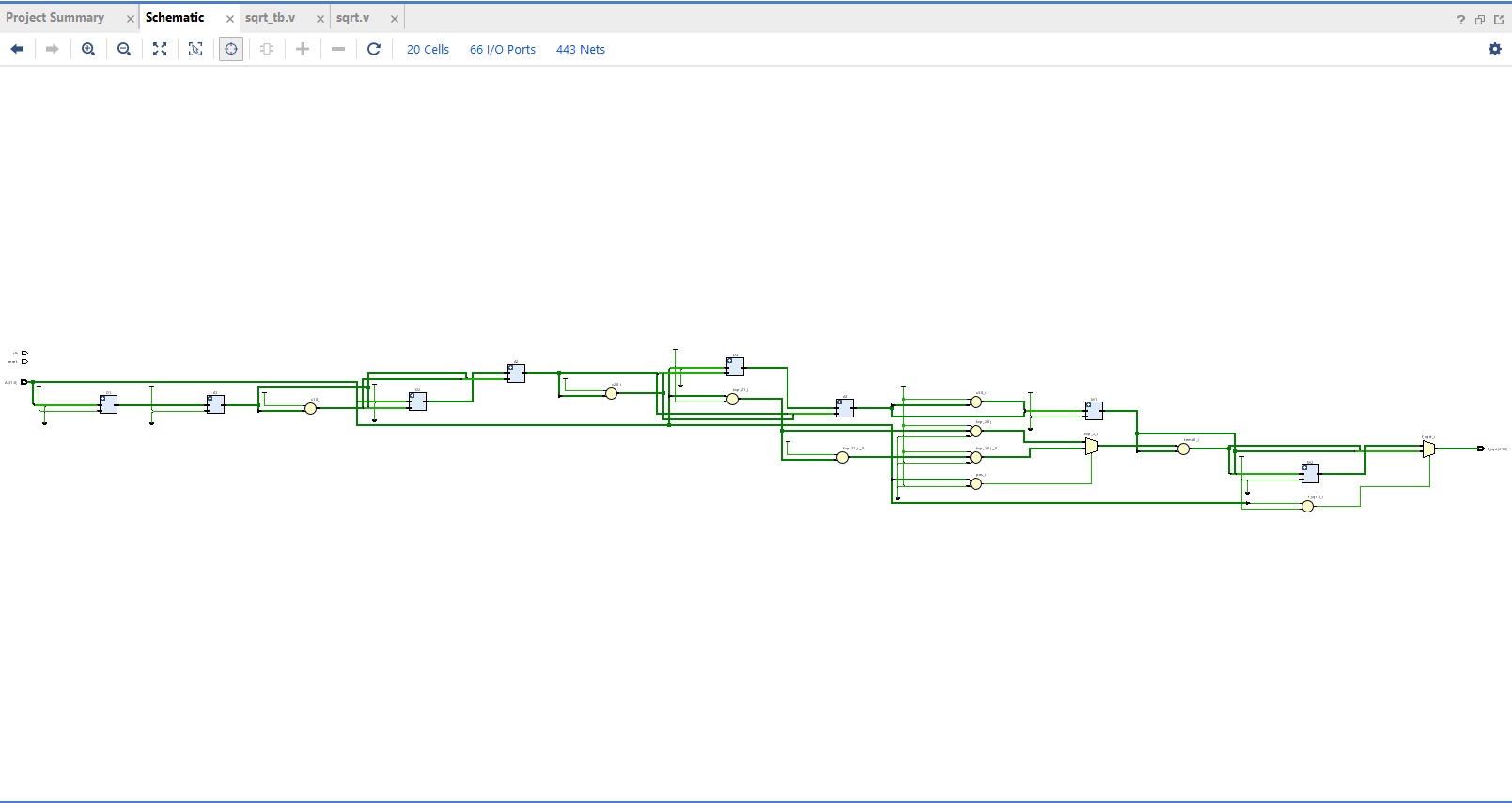

Reports: timing, power

Approach:

Result is accumulated using X[i+1] = Xi * (3 - Xi * Xi * d) / 2.

1/√N is obtained from a pre-calculated LUT.

This approach is the fastest; consumes lesser area too.

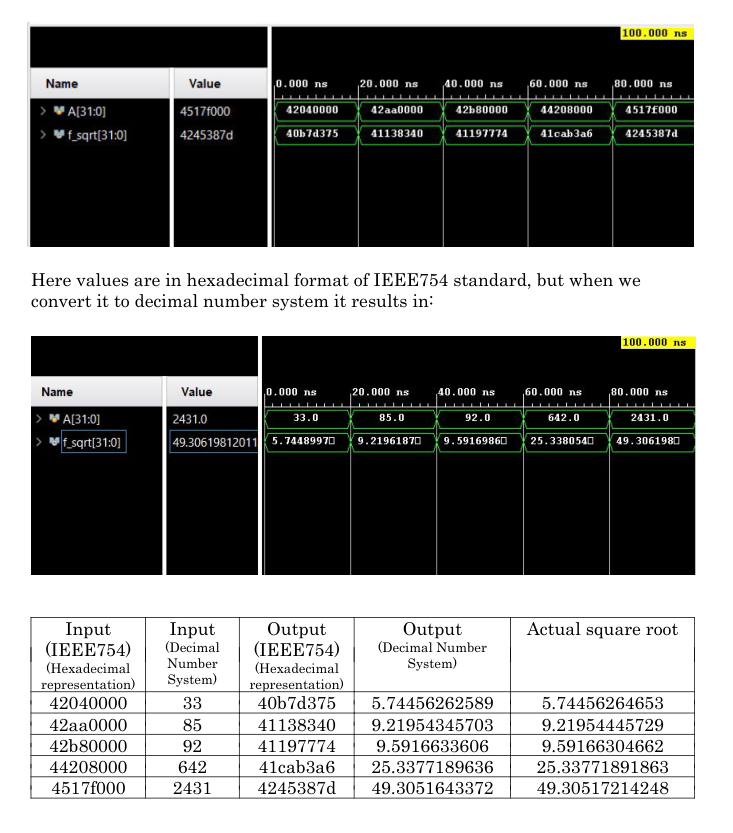

Results

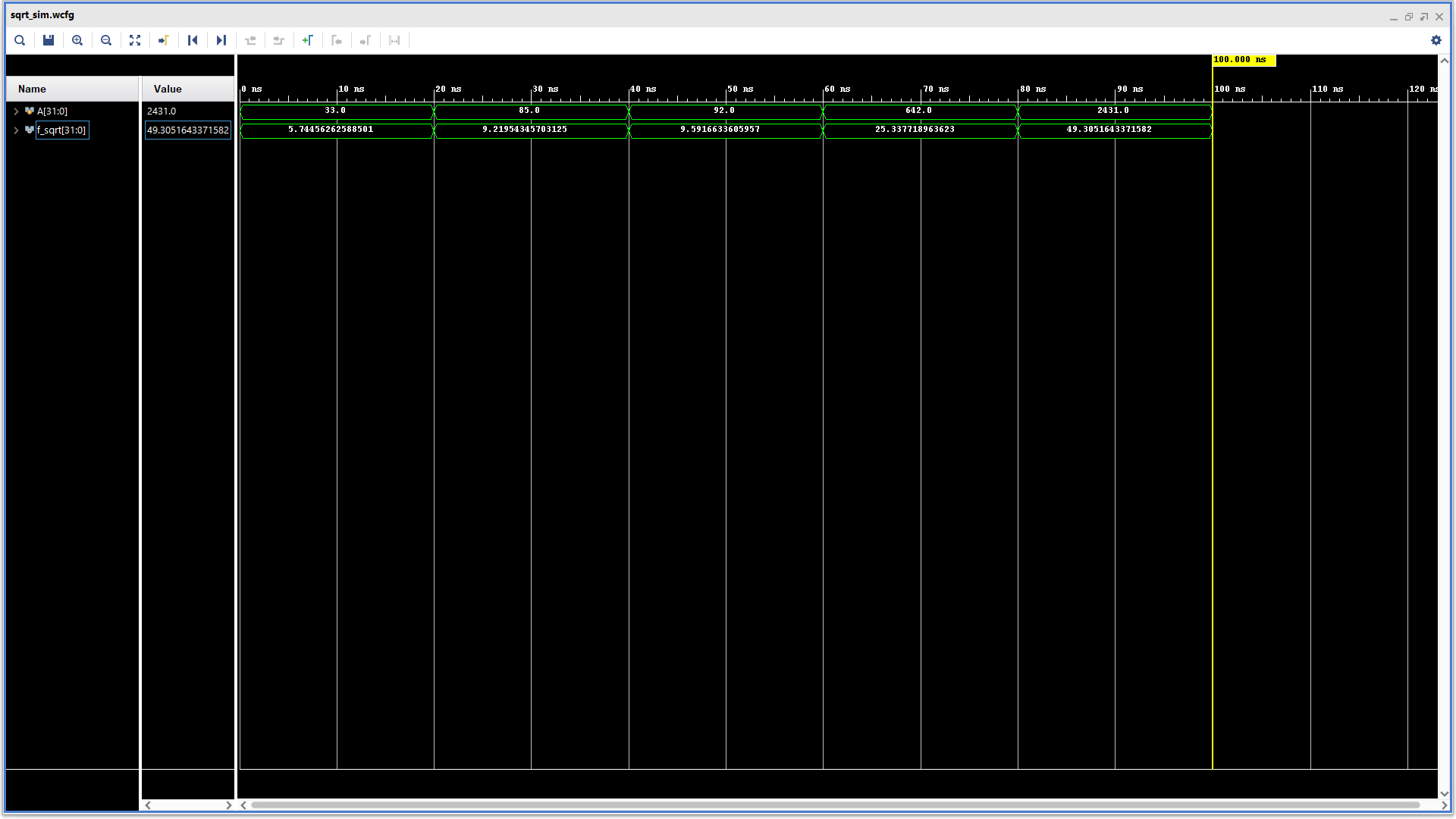

v3: 32bit floating-pt: :

Documentation: 📄

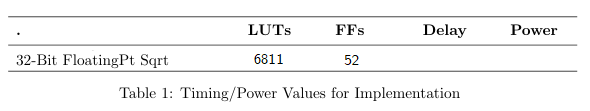

Reports: timing, power

Approach:

(alternative approach) Result is accumulated using 4 stages - 3 iterations for partial sums, 1 for normalizing values to fit IEEE754 format (ie, multiply by √2 if E is odd ). The approach/partial sums are listed below:

Results