简体中文 | English

YatCPU(Yet another toy CPU) is a simple three-stage pipeline RISC-V implementation written in Chisel 3 HDL with support for AXI4-Lite, featuring its painless hands-on experience and VGA output for fun.

You can play Tetris on your own CPU!

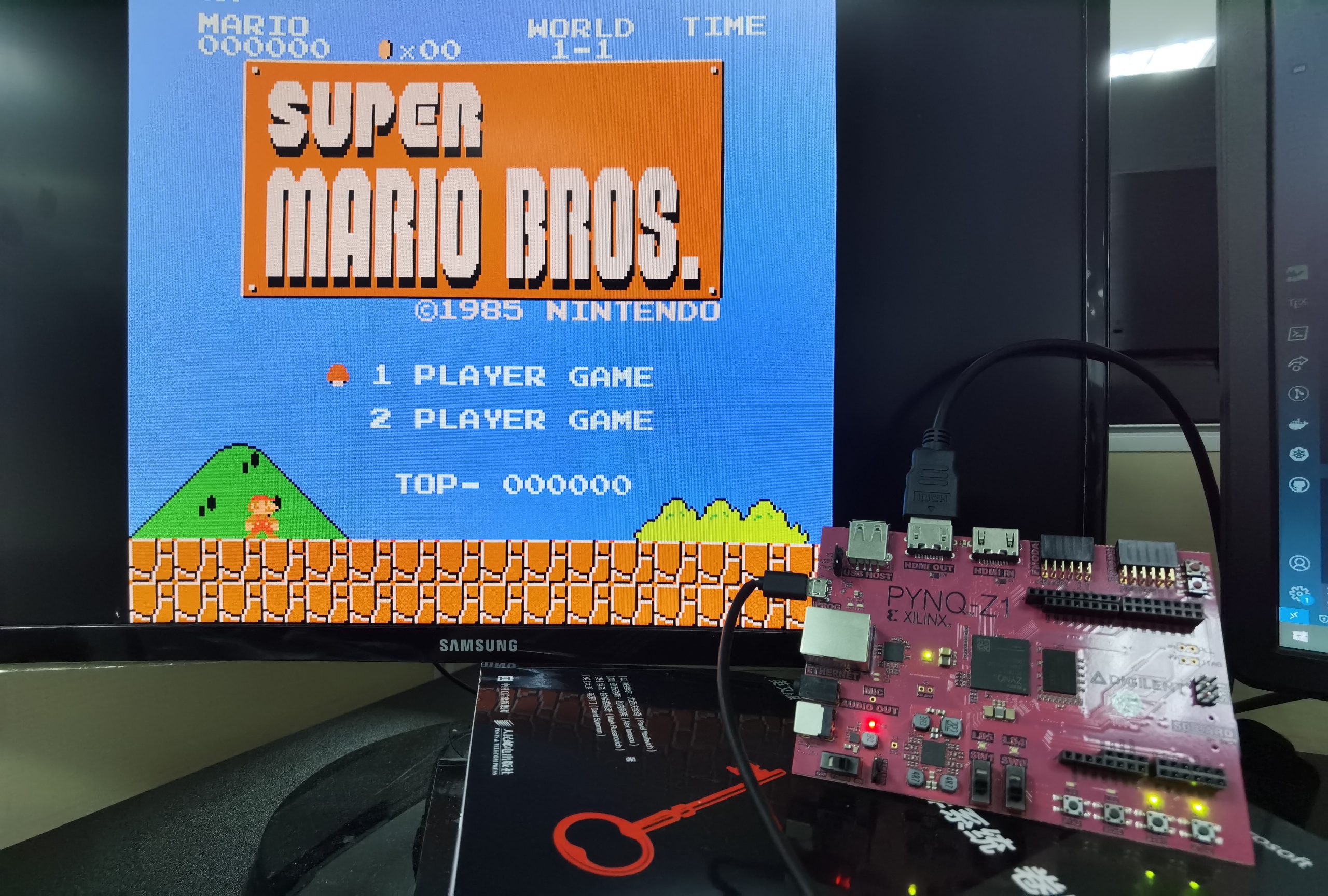

You can also run an NES emulator!

Heavily inspired by tinyriscv, this project is still in its very early stage and under active development. We are looking forward to your feedback and contributions!

- L1 I-cache and D-cache

- Branch predictor

- Run Yat-sen OS RISC-V

- RV32M

- Pass RISC-V compliance test

- Run CoreMark benchmarks

- Basic knowledge of digital logic and design principles

- Basic knowledge of C/C++

- (Optional) A FPGA development board

- Windows 10 or higher / Linux (Debian, Ubuntu, WSL1/2 or other distros) / macOS

- We have tested on Windows 10 and WSL Debian 11

- macOS is able to run the software simulation, but unable to write FPGA boards

- Java 8 or higher

- Scala 2.13.8 (not 3)

- sbt

- (Optional) Latest Verilator

- (Optional) Vivado 2020.1 or higher

Please refer to YatCPU Docs for more documentation.