RISC-V Pipelined Processor RV32I core with CSR

This is a 3-Stage Pipelined Processor with CSR support running the RV32I implementation, hence a 32-bit CPU, written in SystemVerilog. It was made for learning purposes, it's not intended for production under the supervision of our respected Mentor @hamza-akhtar-dev . Developed and Tested on ModelSim.

RISC-V reference

I recommend 100% to read the RISC-V Reference Manual, maybe not complete but those sections mentioning the RV32I implementation.

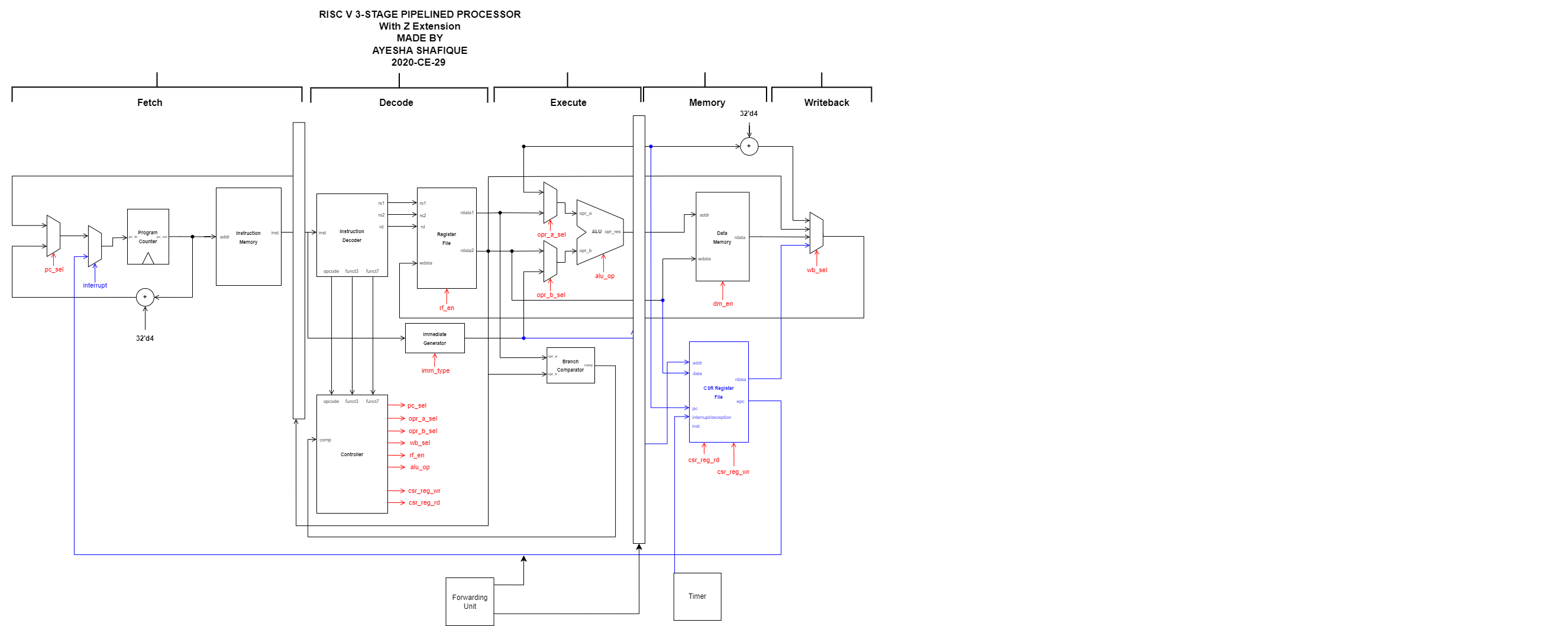

Architecture

The architecture was heavily inspired by the 32-bit Single Cycle MIPS processor explained in Digital Design and Computer Architecture book. Note that instruction and data are stored in separate memories.

Documentation

The documentation consists of three documents:

- User-Level ISA Specification

There is the user-level ISA specification. The most important thing is that it discusses the basic instructions and core elements. Here are highlighted instructions for RV32I, RV32E, RV64I and RV128I. What ISA means is in Terms needing explanation. Link v2.2 [13.12.2020]: https://riscv.org/wp-content/uploads/2017/05/riscv-spec-v2.2.pdf - Privileged ISA specification

It describes the elements of the processor, which are related to the management of priority levels. It's used to how to start the operating system. Also are defined here as interrupt handling or physical memory management. Link v1.10 [13.12.2020]: https://riscv.org/wp-content/uploads/2017/05/riscv-privileged-v1.10.pdf - Debug specification

Describes a standard, that enables debugging. Link 0.13.2 [13.12.2020]: https://riscv.org/wp-content/uploads/2019/03/riscv-debug-release.pdf

How to work

Add Risc V assembly code in

sim/asm_code.s

Remember to update path of bin folder of modelsim in Makefile

conv_to_machine: #converts assembly code to machine code

#this make does not call this makefile but in that folder

cd docs/assembly_to_machine/ && $(MAKE)

compile:

/yourpath/modelsim_ase/bin/vlog *.sv

simulate:

/yourpath/modelsim_ase/bin/vsim -c tb_processor -do "run -all"

run: conv_to_machine compile simulate

For linux Users

RTL can be compiled and simulated with the command:

sudo make run

Viewing the VCD Waveform File

To view the waveform of the design run the command:

sudo make wave

This opens a waveform window. Pull the required signals in the waveform and verify the behaviour of the design. If it won't work in IDE terminal open linux system terminal and re-run the command. Gtkwave has some issue in IDE say VS code, etc.

For Windows Users

Compilation

RTL can be compiled with the command:

vlog names_of_all_system_verilog_files

or simply:

vlog *.sv

Compilation creates a work folder in your current working directory in which all the files generated after compilation are stored.

Simulation

The compiled RTL can be simulated with command:

vsim -c name_of_toplevel_module -do "run -all"

Simulation creates a .vcd file. This files contains all the simulation behaviour of design.

Viewing the VCD Waveform File

To view the waveform of the design run the command:

gtkwave dumfile_name.vcd

This opens a waveform window. Pull the required signals in the waveform and verify the behaviour of the design.