El cronómetro opera sobre una FPGA Cyclone IV. Con el fin de poder visualizar el mismo en acción se empleo un monitor con conexión VGA. Para poder mostrar los digitos en pantalla se realizo una interfaz opera mediante el protocolo VGA y una serie de modulos especialmente diseñados para mostrar dibujar los digitos sobre la pantalla.

Aquí debajo podran encontrar el esquema del programa.

Recuerden que aquí se esta empleando un lenguaje funcional y su naturaleza implica que la ejecución de sus diferente modulos

se realizan en simultaneo.

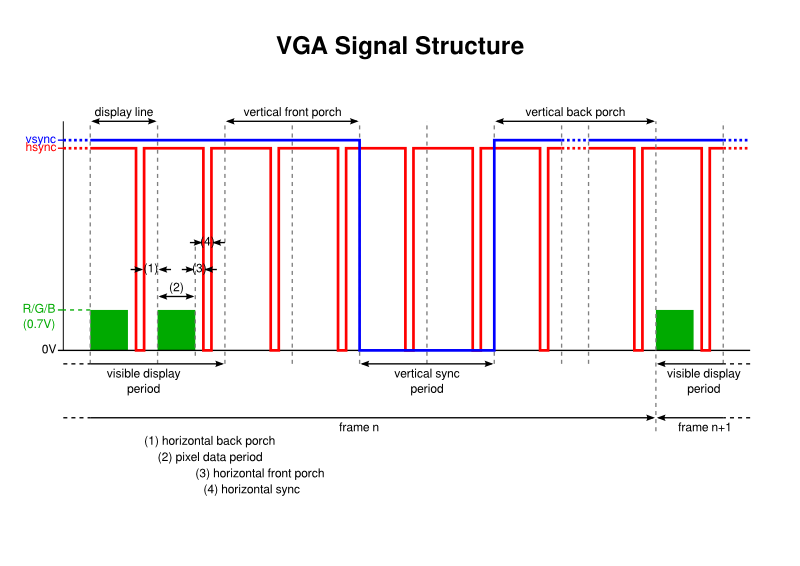

Para poder comunicarle al monitor cual sera la resolución de trabajo debemos respetar un cierto protocolo que involucra dos señales de sincronismo.

Aquí debajo se pueden apreciar ambas señales al mismo tiempo. Notese que la zona verde indica la zona visible. Dadas las señales de sincronización, el monitor comenzara su barrido a través de la pantalla. Para esto, el modulo VGA nos provee de la coordenadas actuales sobre las que esta el cursor del monitor. Es decir, al avanzar dos señales indicaran en que posición relativa al extremo superior izquierdo esta actualmente el cursor.

Una vez obtenido dicho dato, se debe poder discernir qué graficar (qué número) y dondé.

Para poder seleccionar el número adecuado a graficar debemos poder leer la data enviada por el modulo separador de digito. Este actualizara su información una vez por barrido completo de la pantalla. De esta forma evitamos imprevistos durante el proceso de dibujo. Por ejemplo, el digito de los segundo podría cambiar durante el barrido causando que la imagen no se vea correctamente.

Para poder graficar se diseño a cada número como un conjunto de cuadrados que ilustran el digito.Ahora, con el fin de poder mostrar el número en pantalla se diseñaron modulos que permiten graficar los digitos individualmente. Cada uno de esos modulos tiene toda la información necesaria como para poder saber su ubicación relativa en la pantalla.

Al poder leer los pares x,y es posible determinar si deben emitir un pulso de dibujo o no deben hacerlo.

Pueden verlo en acción haciendo click aquí.- Tutorial Quartus by Sebas

- Introducción a VGA con verilog en https://timetoexplore.net