A simple implementation of FPGA PUF with AXI bus.

This work can generate 96 bit puf with a Xilinx Alveo u200 card, which can be used in private key, etc.

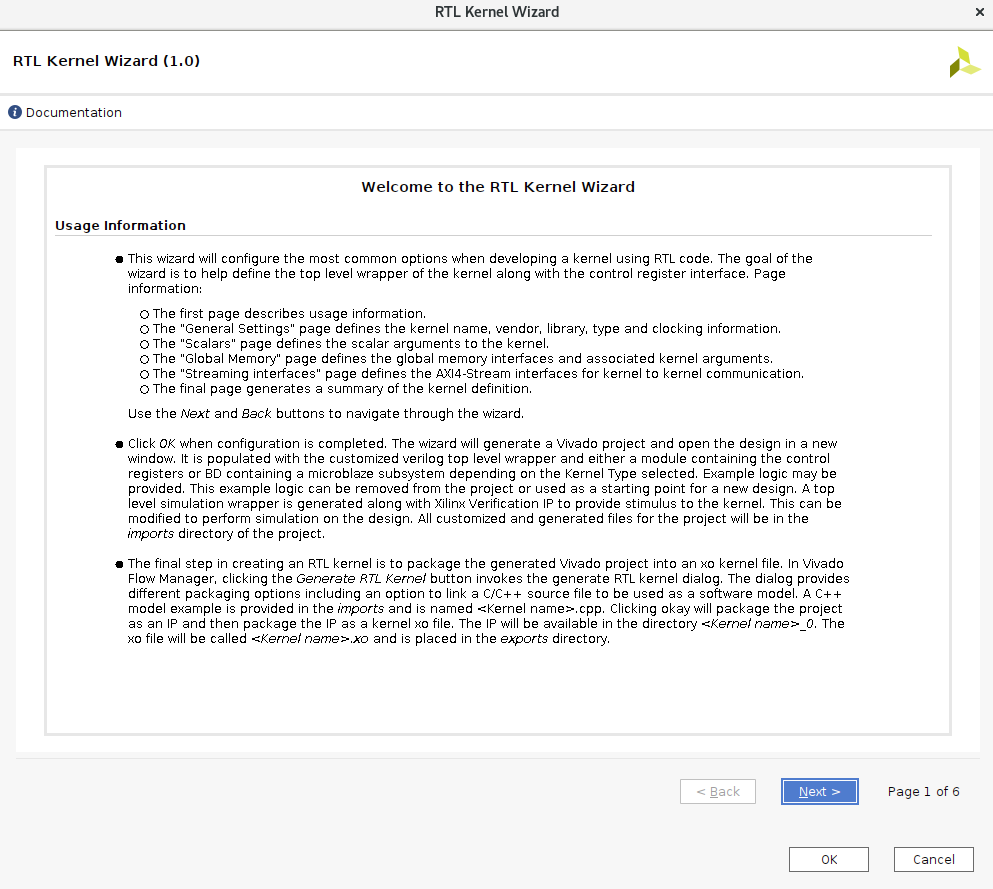

- Open the

Xilinx/Launch RTL wizard kernel.

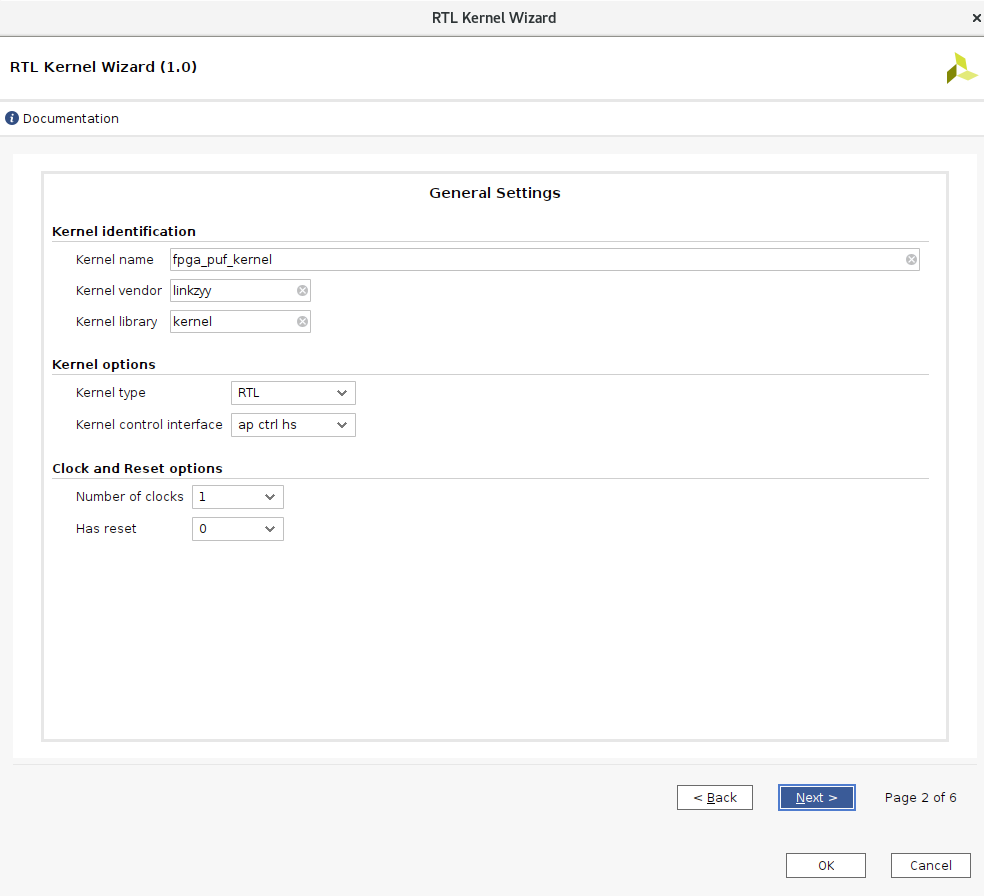

- Create a kernel, and set the kernel name.

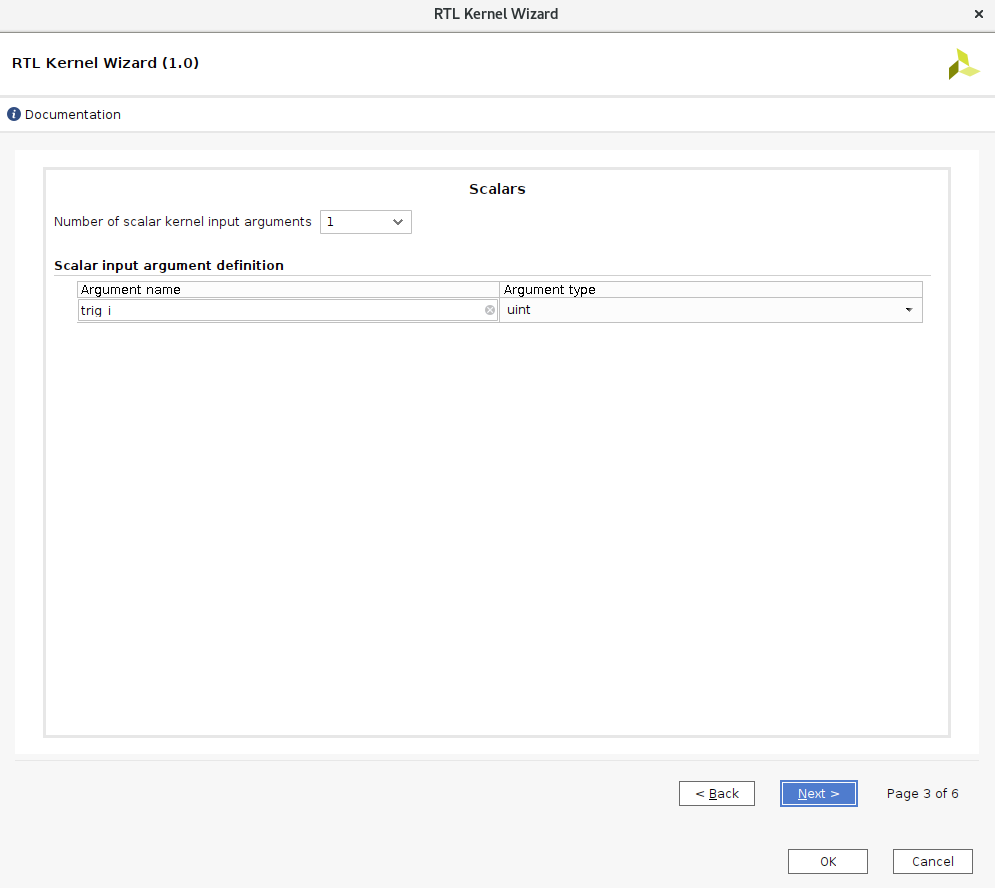

- Set the scalar arguments.

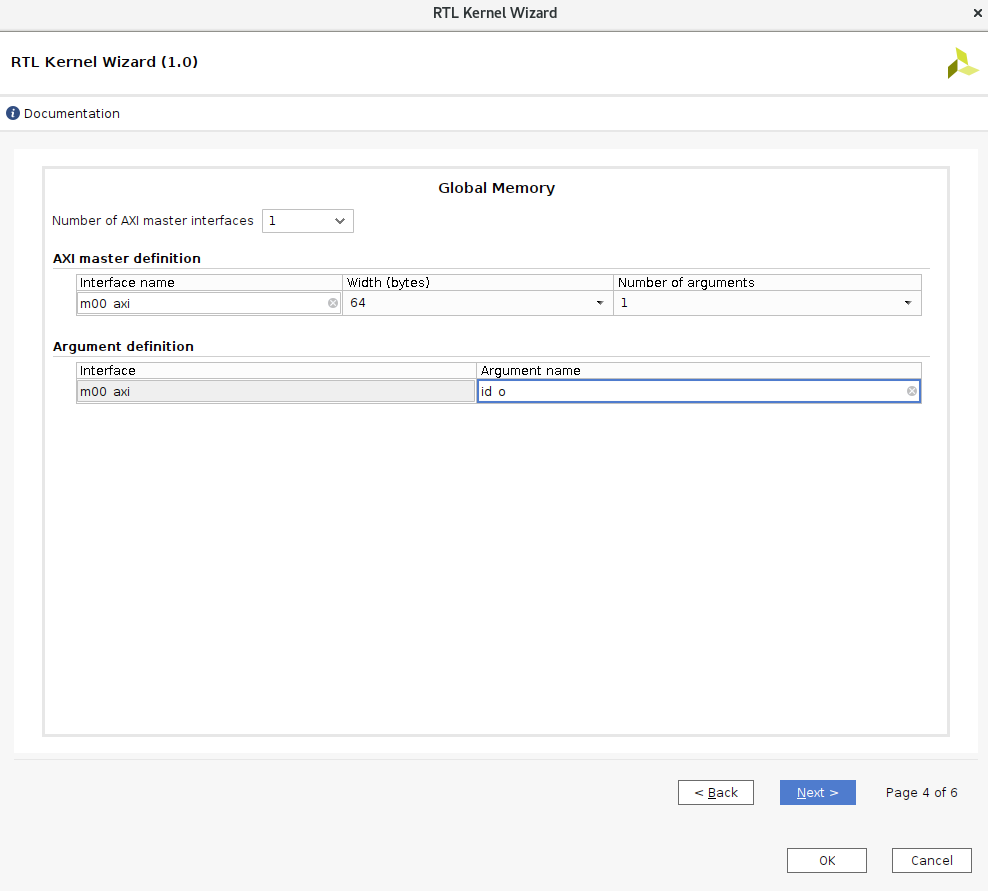

- Set the AXI arguments.

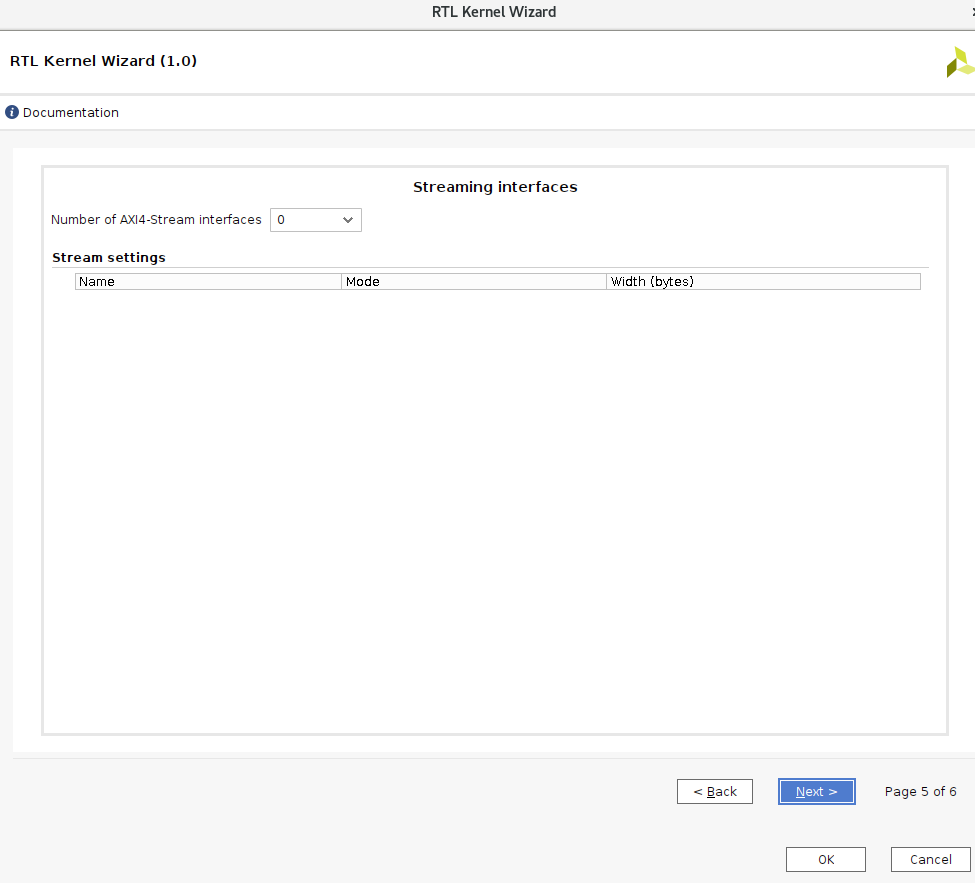

- Do nothing.

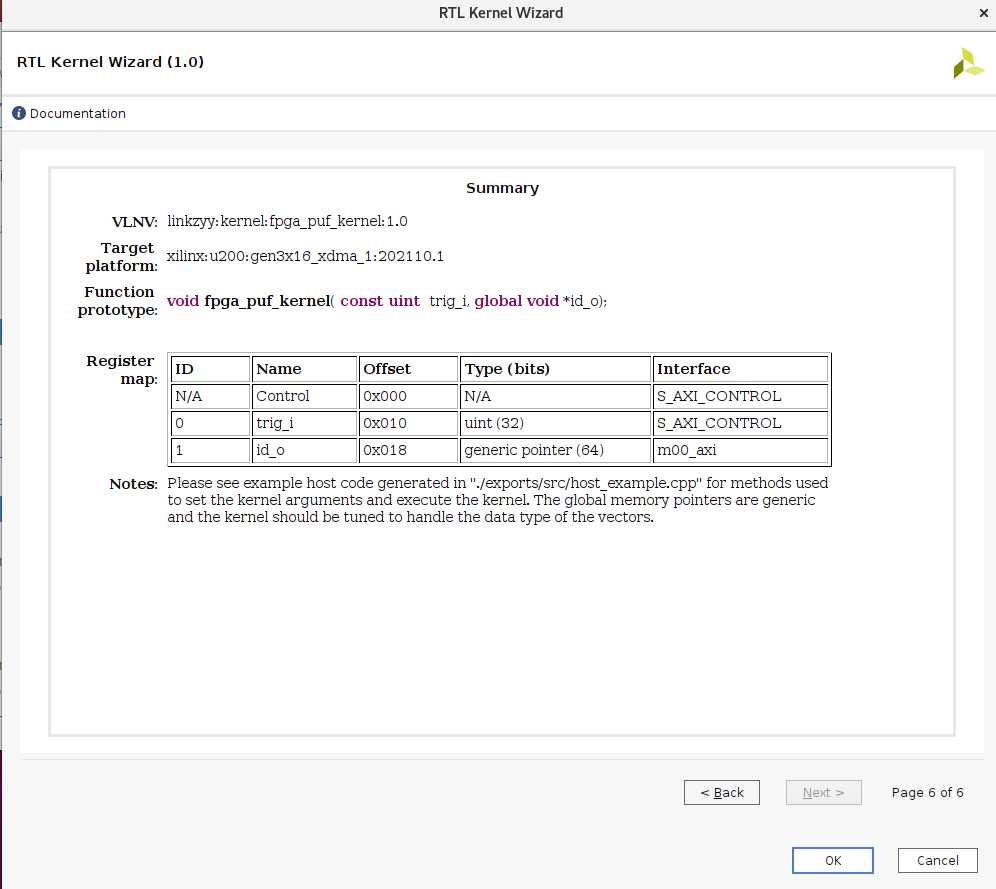

- Check the opencl kernel prototype.

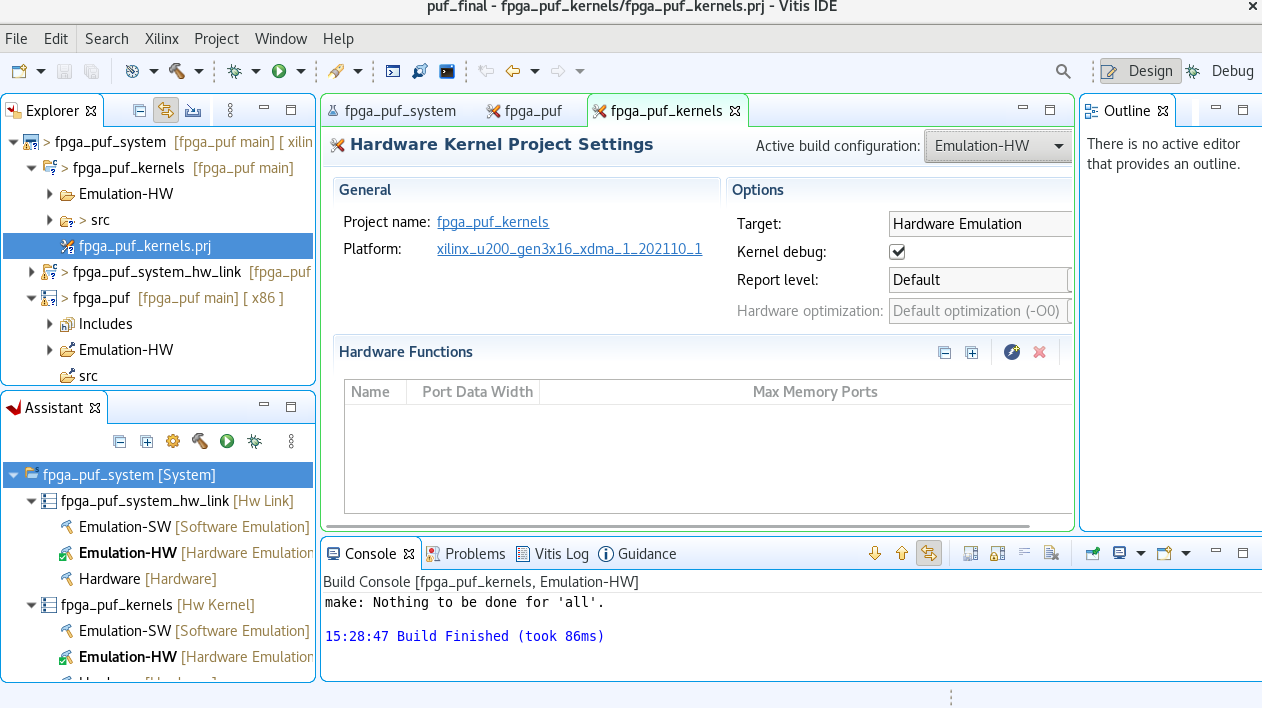

- Load the rtl sources and it will automatically create

fpga_puf_kernels.prj.

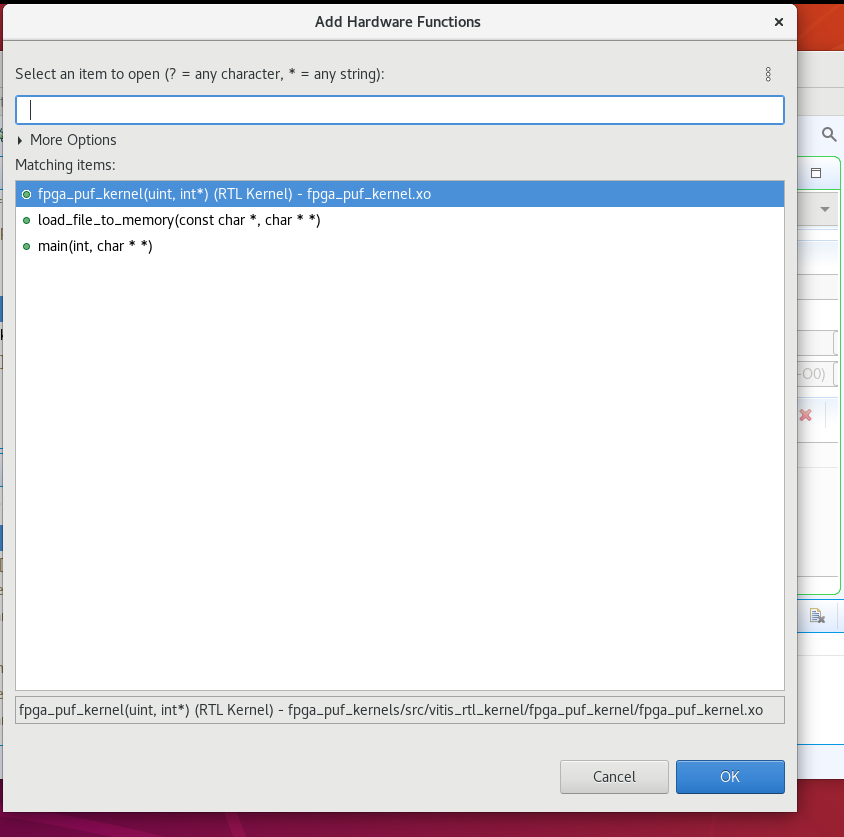

- Add hardware functions

- build

g++ -I$XILINX_XRT/include/ -I$XILINX_VIVADO/include/ -Wall -O0 -g -std=c++11 host.cpp -o 'host' -L$XILINX_XRT/lib/ -lOpenCL -lpthread -lrt -lstdc++$ ./host binary_container_1.xclbin xilinx_u200_gen3x16_xdma_base_1