Table of Contents

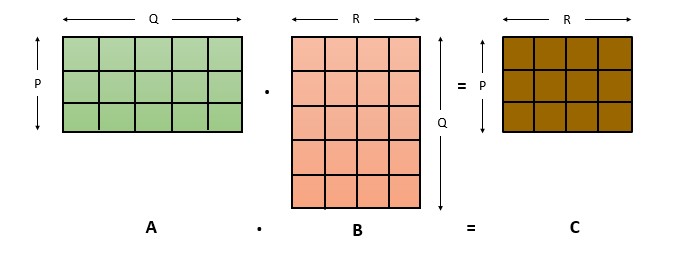

This is an implementation of a matrix multiplication module intended to compute the product of two P × Q and Q × R matrix instances, resulting in a new P × R matrix (where P, Q and R are greater than or equal to 2).

The resulting module includes an Overflow signal to indicate overflow conditions. Additionally, the output is transmitted to the DataOUT port over several cycles. Once the output is ready, the Done signal is issued, indicating that the valid output is available on the DataOut port.

The programming language, frameworks, and technologies used in the project are listed here:

- Verilog

- Xilinx ISE

- ModelSim

Here is a list of some useful links and tutorials relevant to this project:

Mehrdad Nourbakhsh - mehrdad.nb4@gmail.com