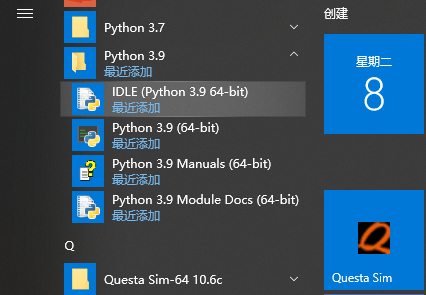

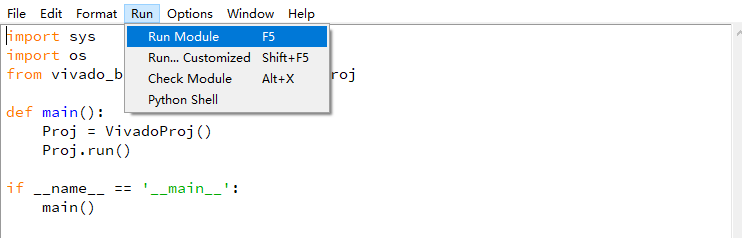

- 本目录下的脚本请勿使用pycharm运行,用pycharm运行时可能无法打开仿真软件GUI界面,用python3运行即可

- 脚本支持在Windows或Linux系统下运行,其中Windows下运行效果较好,Linux系统下不建议使用本脚本的仿真相关功能,可以自行设置shell和Makefile脚本

- 脚本支持2017.2、2018.2和2019.2的vivado工程,其他版本未测试,其中对2017.2版本支持最好

首次运行前需要:

-

保证vivado工程已经添加好代码文件和IP核,并设置好第三方联调仿真库和仿真软件

-

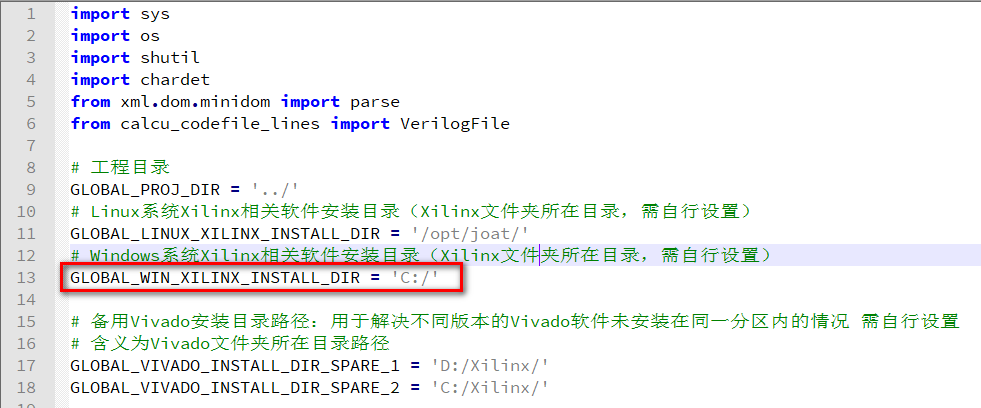

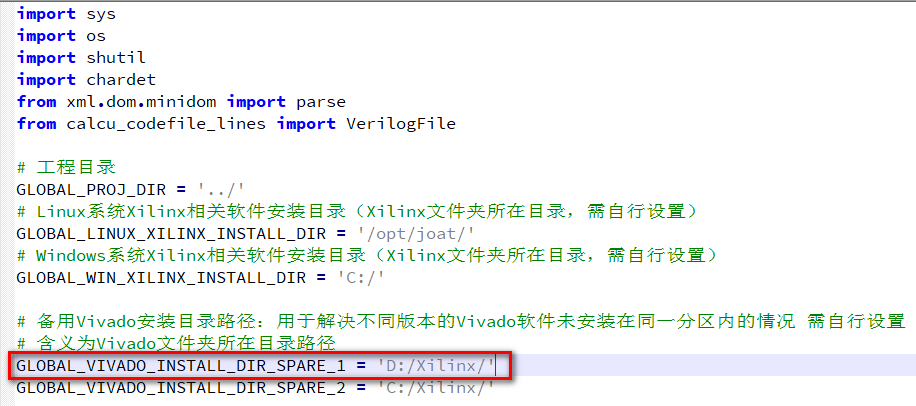

使用文本编辑器修改代码文件

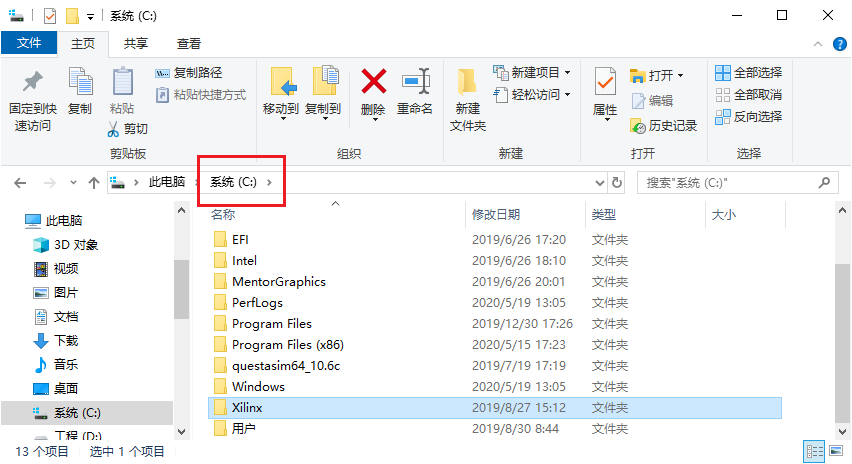

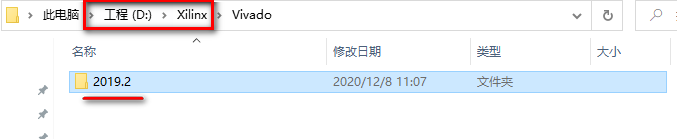

vivado_batch_sim.py中第11~18行的Xilinx或Vivado软件安装目录常量,各常量具体含义如下:GLOBAL_LINUX_XILINX_INSTALL_DIR:Linux系统下Xilinx文件夹所在目录路径GLOBAL_WIN_XILINX_INSTALL_DIR:Windows系统下Xilinx文件夹所在目录路径GLOBAL_VIVADO_INSTALL_DIR_SPARE_1:备用路径1,对应版本Vivado软件Vivado文件夹所在目录路径,当脚本在前面路径中无法找到对应版本的Vivado时,会在备用路径中查找GLOBAL_VIVADO_INSTALL_DIR_SPARE_2:备用路径2

代码位置如下所示:

import sys

import os

import shutil

import chardet

from xml.dom.minidom import parse

from calcu_codefile_lines import VerilogFile

# 工程目录

GLOBAL_PROJ_DIR = '../'

# Linux系统Xilinx相关软件安装目录(Xilinx文件夹所在目录,需自行设置)

GLOBAL_LINUX_XILINX_INSTALL_DIR = '/opt/joat/'

# Windows系统Xilinx相关软件安装目录(Xilinx文件夹所在目录,需自行设置)

GLOBAL_WIN_XILINX_INSTALL_DIR = 'D:/'

# 备用Vivado安装目录路径:用于解决不同版本的Vivado软件未安装在同一分区内的情况 需自行设置

# 含义为Vivado文件夹所在目录路径

GLOBAL_VIVADO_INSTALL_DIR_SPARE_1 = 'D:/Xilinx/'

GLOBAL_VIVADO_INSTALL_DIR_SPARE_2 = 'C:/Xilinx/'根据自己当前系统类型(Windows或Linux)修改对应的常量为当前系统中Xilinx文件夹的所在位置,或者根据需要设置备用路径。

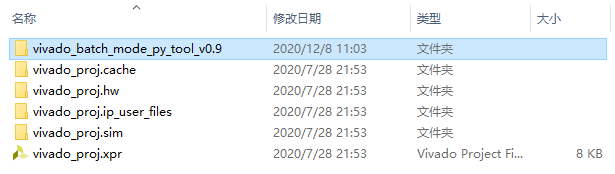

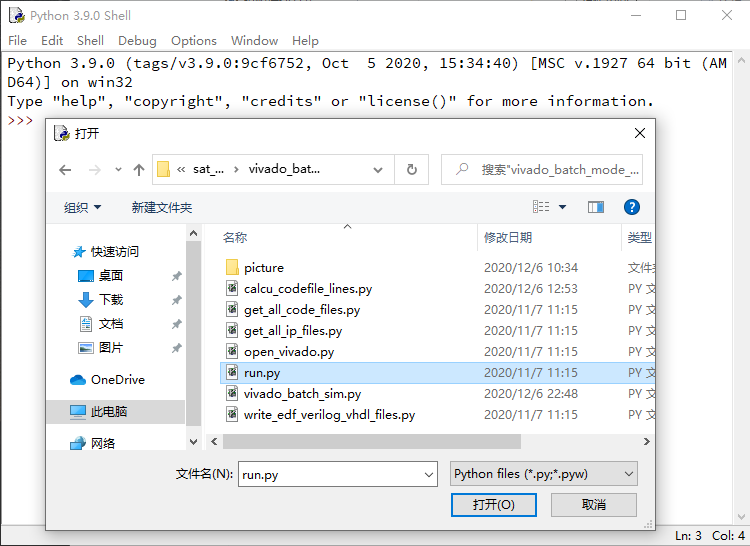

- 将该文件夹放置于工程目录下(即

.xpr文件所在目录下),使用python3运行run.py即可

- 该脚本可以对

.xpr工程文件进行xml解析并存储相关结果 - 该脚本可以调用对应版本的

vivado软件生成当前工程的仿真相关脚本 - 该脚本可以对

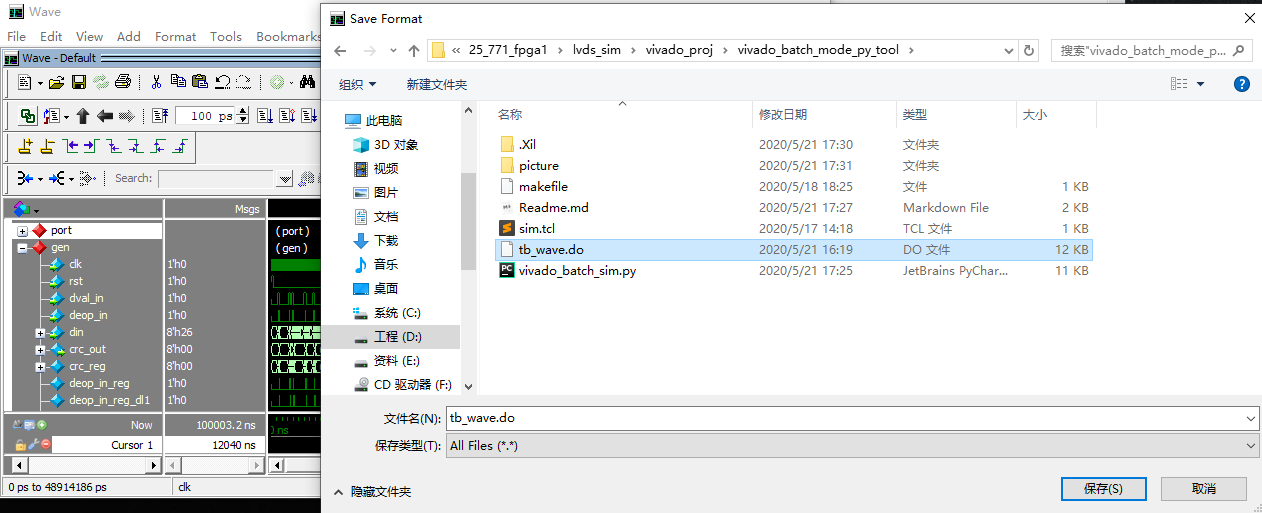

vivado软件生成的脚本文件中反人类的代码进行删改和添加**(Windows系统,log -r ./*等)** - 该脚本可以将所在目录下名为

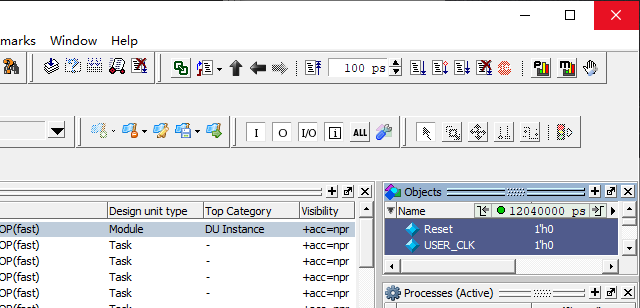

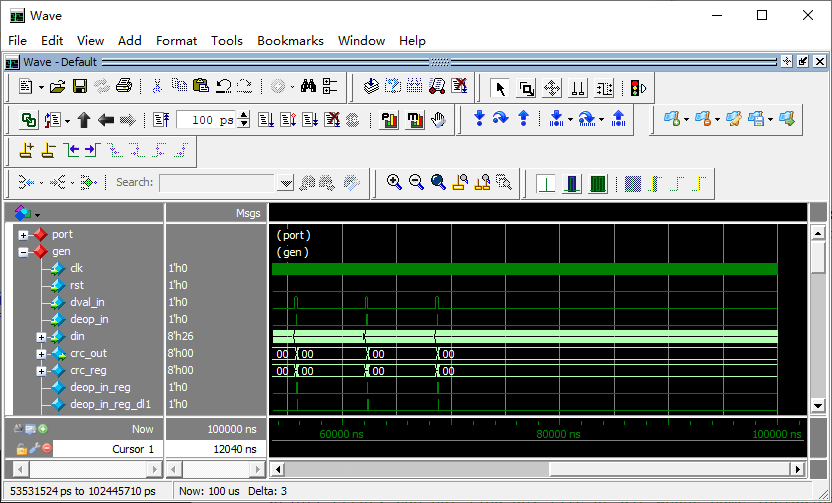

tb_wave.do的波形脚本文件内容替换进vivado生成的波形脚本中 - 该脚本可以对删改后的脚本进行执行,调出仿真软件GUI运行仿真

- 该脚本可以对已经添加到工程中的代码和约束文件进行提取,拷贝到脚本所在目录下的

copy_code_files文件夹下,保持原有代码文件的目录结构的同时,将文件编码统一转换为utf-8。 - 该脚本可以对已经添加到工程中的IP核的

xci文件进行提取,以每个xci文件一个独立同名文件夹的形式拷贝到脚本所在目录下的copy_ip_files文件夹下,方便移植建立新的工程 - 该脚本可以调用

vivado软件的batch mode分别对工程进行综合synthesis和实现implement - 该脚本可以将当前可综合的工程生成EDF网表文件和对应的Verilog、VHDL源文件(相当于生成固核)

- 该脚本可以对添加到工程中的

Verilog和VHDL代码文件进行行数统计,将详细结果写入到文本文件中

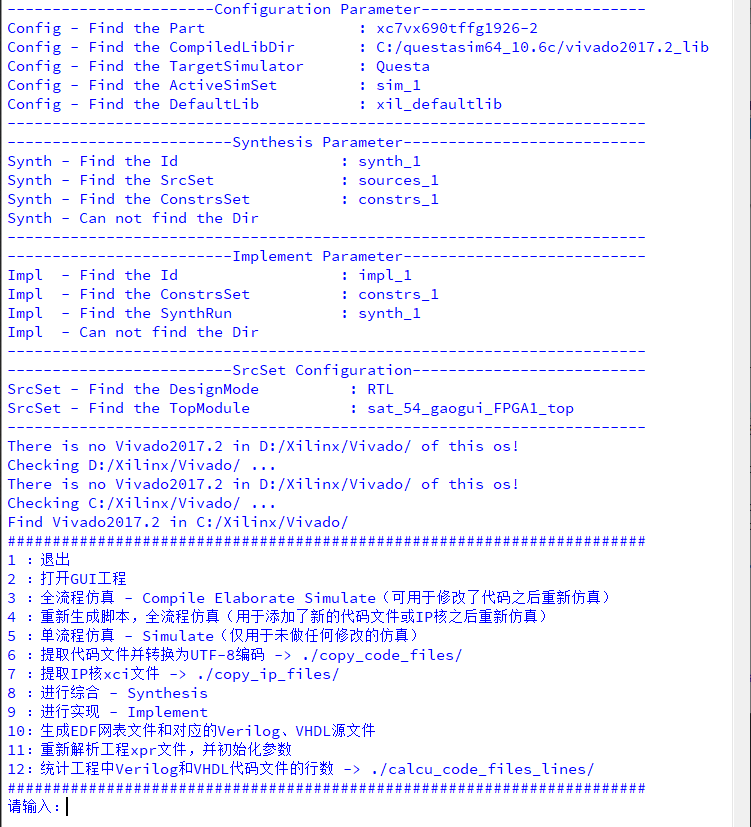

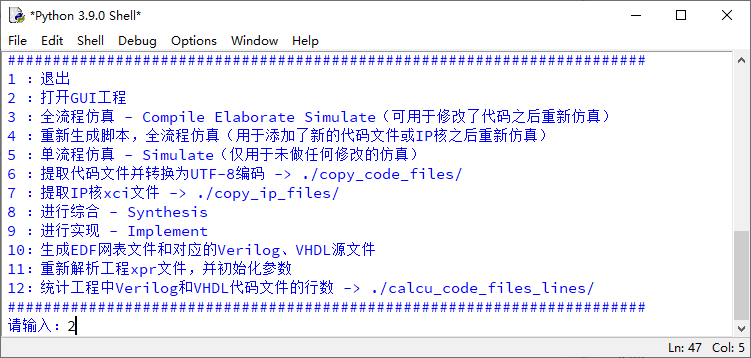

1 :退出 2 :打开GUI工程 3 :全流程仿真 - Compile Elaborate Simulate(可用于修改了代码之后重新仿真) 4 :重新生成脚本,全流程仿真(用于添加了新的代码文件或IP核之后重新仿真) 5 :单流程仿真 - Simulate(仅用于未做任何修改的仿真) 6 :提取代码文件并转换为UTF-8编码 -> ./copy_code_files/ 7 :提取IP核xci文件 -> ./copy_ip_files/ 8 :进行综合 - Synthesis 9 :进行实现 - Implement 10:生成EDF网表文件和对应的Verilog、VHDL源文件 11:重新解析工程xpr文件,并初始化参数 12:统计工程中Verilog和VHDL代码文件的行数 -> ./calcu_code_files_lines/