This is a RISC-like implementation for a 5-stages pipelined processor implemented with Verilog which follows Harvard architecture with 2 separated memories one for the data and the other for the instructions with full forwarding to solve data hazards, a hazard detection unit to solve control hazards, and a compiler script with Python to compile assembly instructions into machine code instructions.

This is an list of needed steps to set up your project locally, to get a local copy up and running follow these steps.

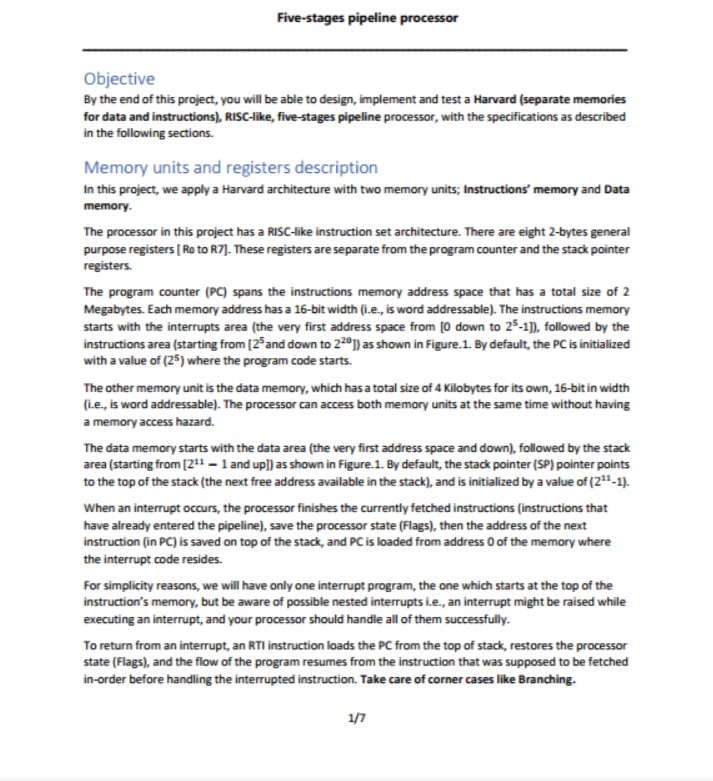

- Clone the repository

$ git clone https://github.com/MoazHassan2022/MZNM-Processor.git -

Navigate to repository directory

$ cd MZNM-Processor - Install ModelSim

- Run ModelSim

- Running simulation in ModelSim terminal, this will compile and run assembly instructions written in

./instructions.asm$ do simulation.do

MZNM-Processor

├── design

├── processorDesign.drawio

├── processorDesign.pdf

├── processorDesign.jpg

├── requirements

├── 1.jpg

├── 2.jpg

├── 3.jpg

├── 4.jpg

├── 5.jpg

├── 6.jpg

├── 7.jpg

├── ALU.v

├── controller.v

├── controllerTB.v

├── controlUnit.v

├── dataMemory.txt

├── dataMemory.v

├── DEBuffer.v

├── defines.v

├── EMBuffer.v

├── FDBuffer.v

├── forwarding-unit.v

├── hazardDetectionUnit.v

├── inst.py

├── instructionMemory.txt

├── instructionMemory.v

├── instructions.asm

├── pc.v

├── processor.v

├── regfile.v

├── simulation.do

├── stackPointer.v

├── writeBack.v

├── README.md

Here is our design in an image

You can also view the design details with drawio website in

./design/processorDesign.drawio

You can also view the design details in

./design/processorDesign.pdf