Index

- Introduction

- Thanks

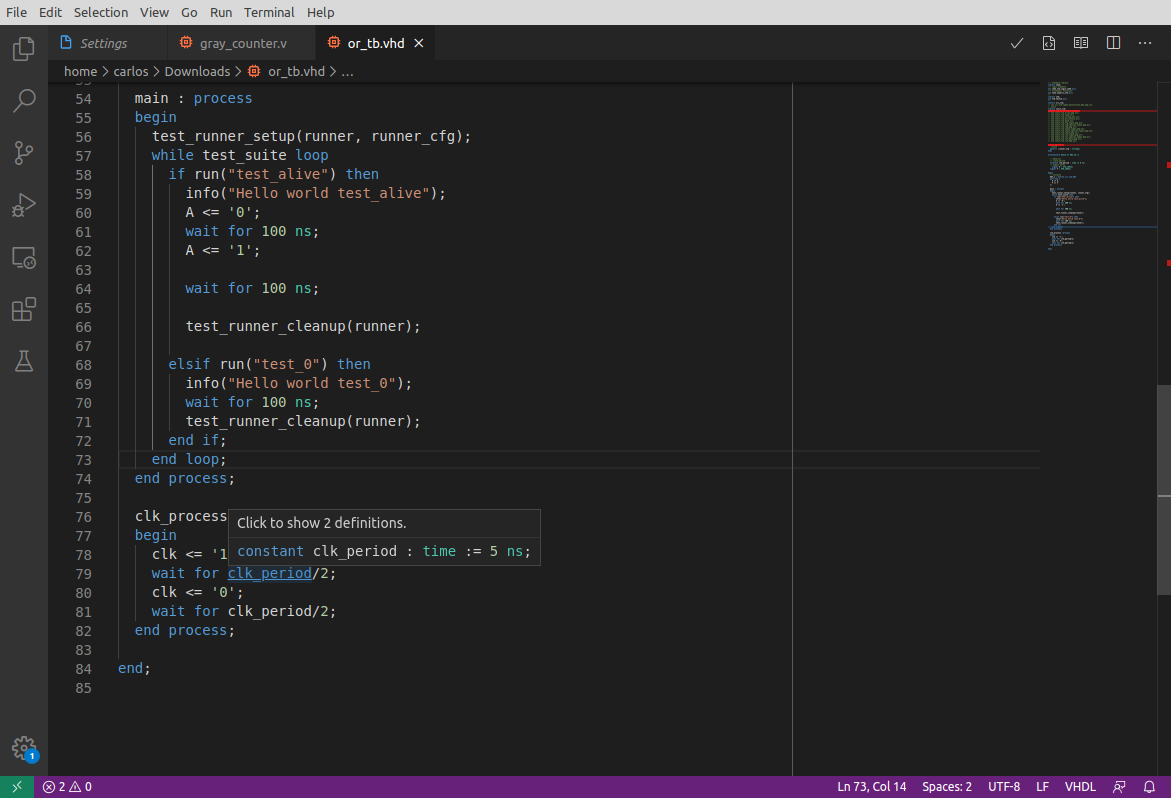

- Go to definition

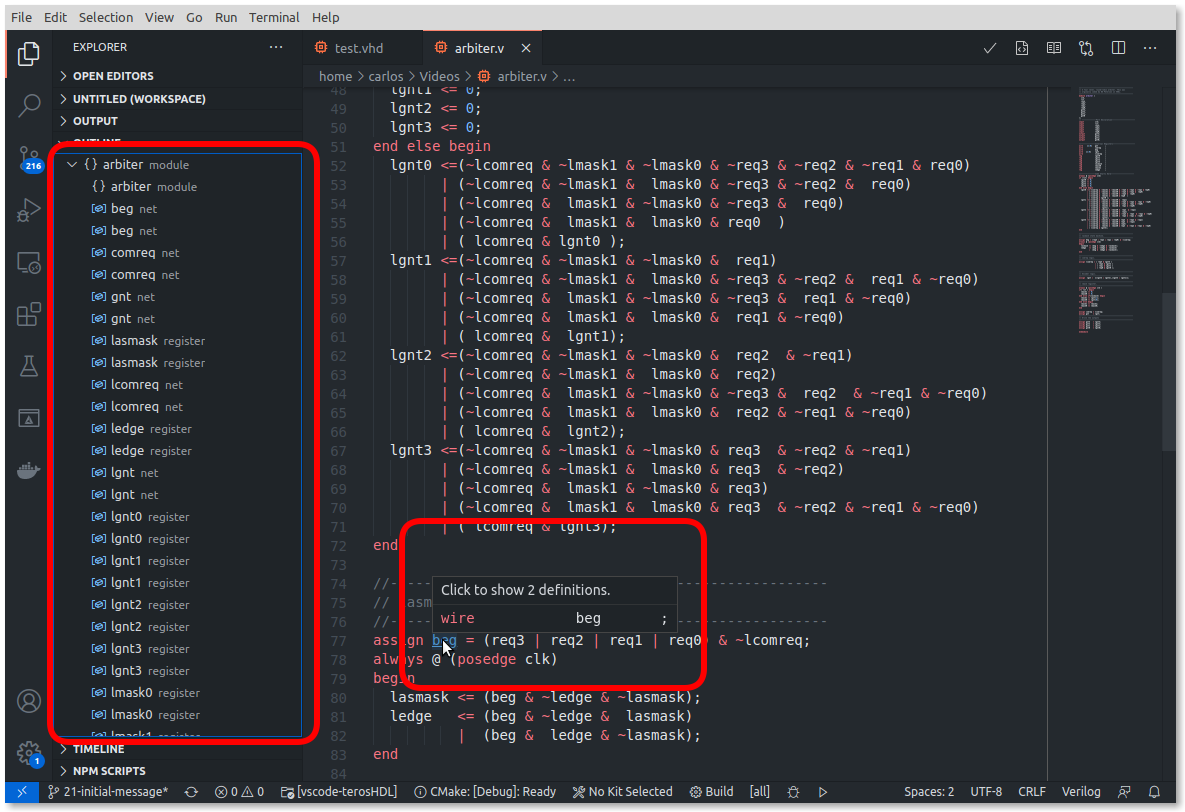

- Hover and structure

- Template generator

- Documenter

- Errors checking

- Style checking

- Formatting

- State machine viewer

- State machine designer

- Dependencies viewer

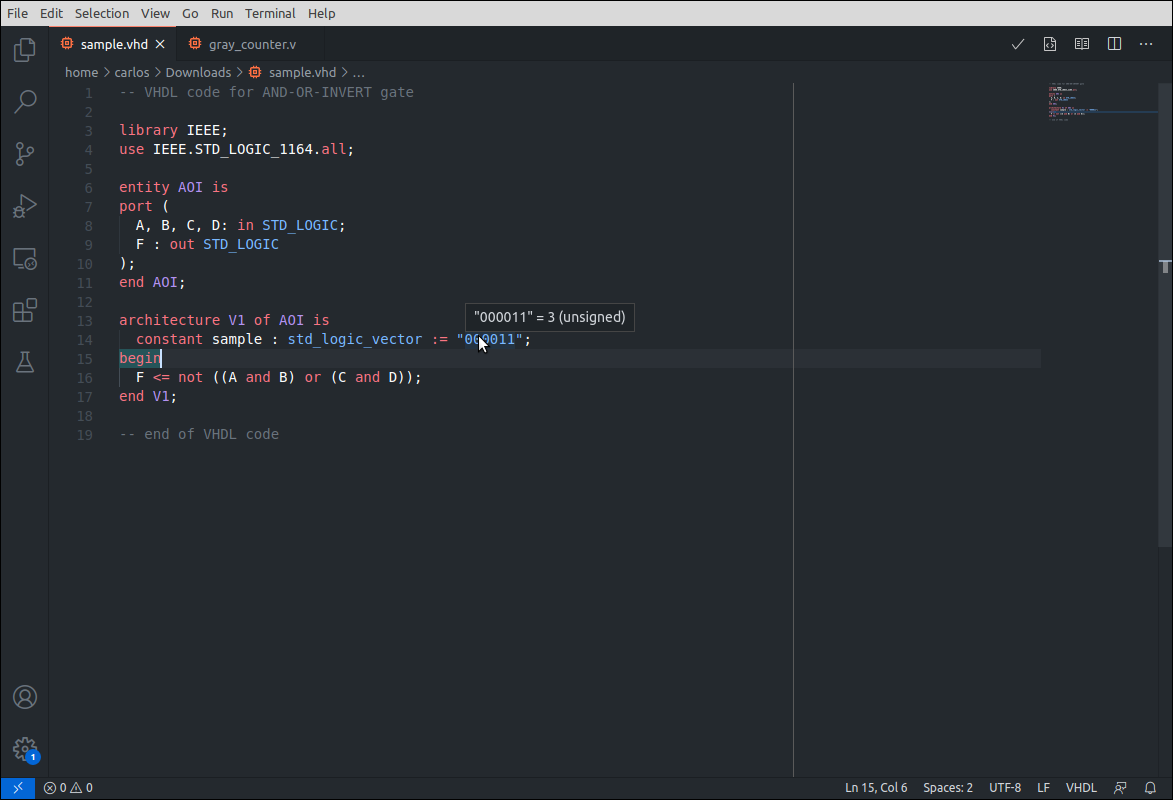

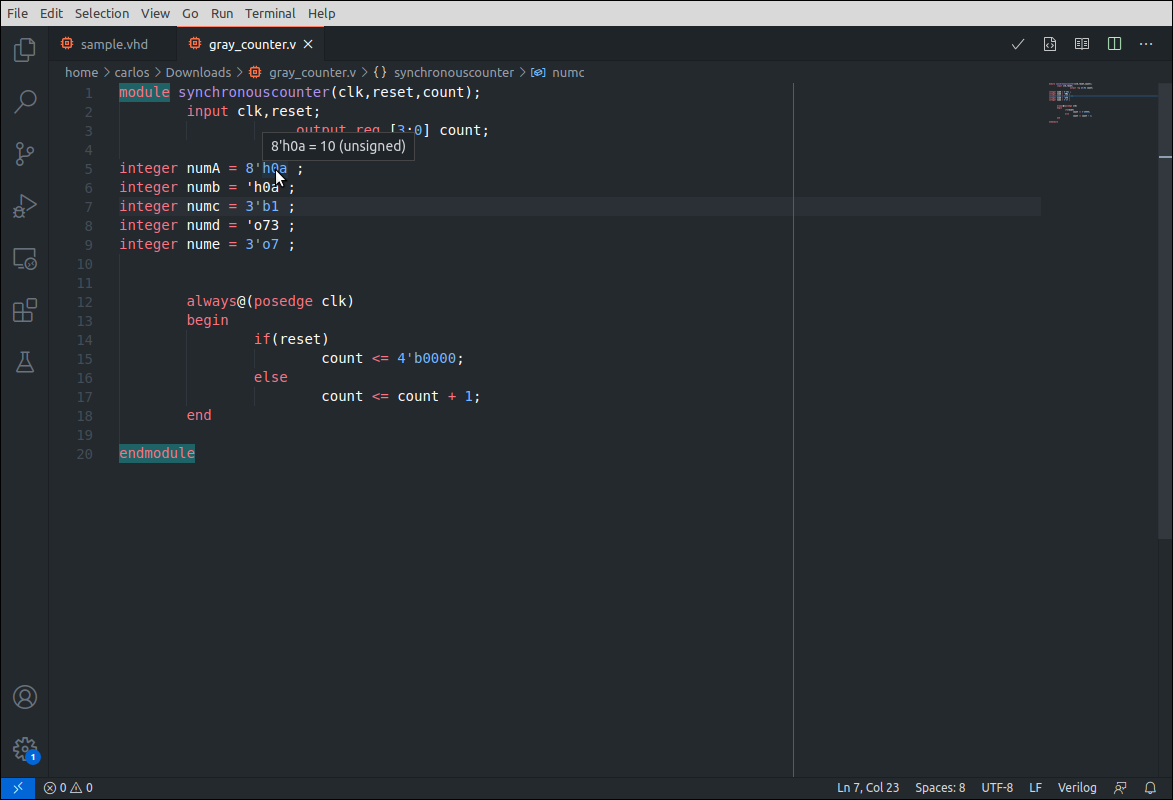

- Hover to evaluate binary, hexadecimal and octal values

- Code snippets and grammar

- Beta Verilog/SV schematic viewer

- Project manager (currently only VUnit supported

- Future work

- Similar projects

Our philosophy is: think in hardware, develop hardware, take advantage of software tools.

The goal of TerosHDL is make the FPGA development easier and reliable. It is a powerful open source IDE.

Please, visit the documentation web for a full IDE description: (https://terostechnology.github.io/terosHDLdoc/)

- Verilog HDL/SystemVerilog (https://marketplace.visualstudio.com/items?itemName=mshr-h.VerilogHDL)

- VUnit (https://vunit.github.io/)

- VSG (https://github.com/jeremiah-c-leary/vhdl-style-guide)

- Wavedrom (https://github.com/wavedrom/wavedrom)

- VHDL formatter (https://github.com/g2384/VHDLFormatter)

- Yosys (http://www.clifford.at/yosys/)

You can jump to the definition with Ctrl+Click.

If you hover over a symbol, a preview of the declaration will appear.

| Verilog | VHDL |

|---|---|

| Testbench | Testbench |

| cocotb | cocotb |

| VUnit | VUnit |

| Signals | Signals |

| Component | Component |

| Instance | Instance |

| Verilator |

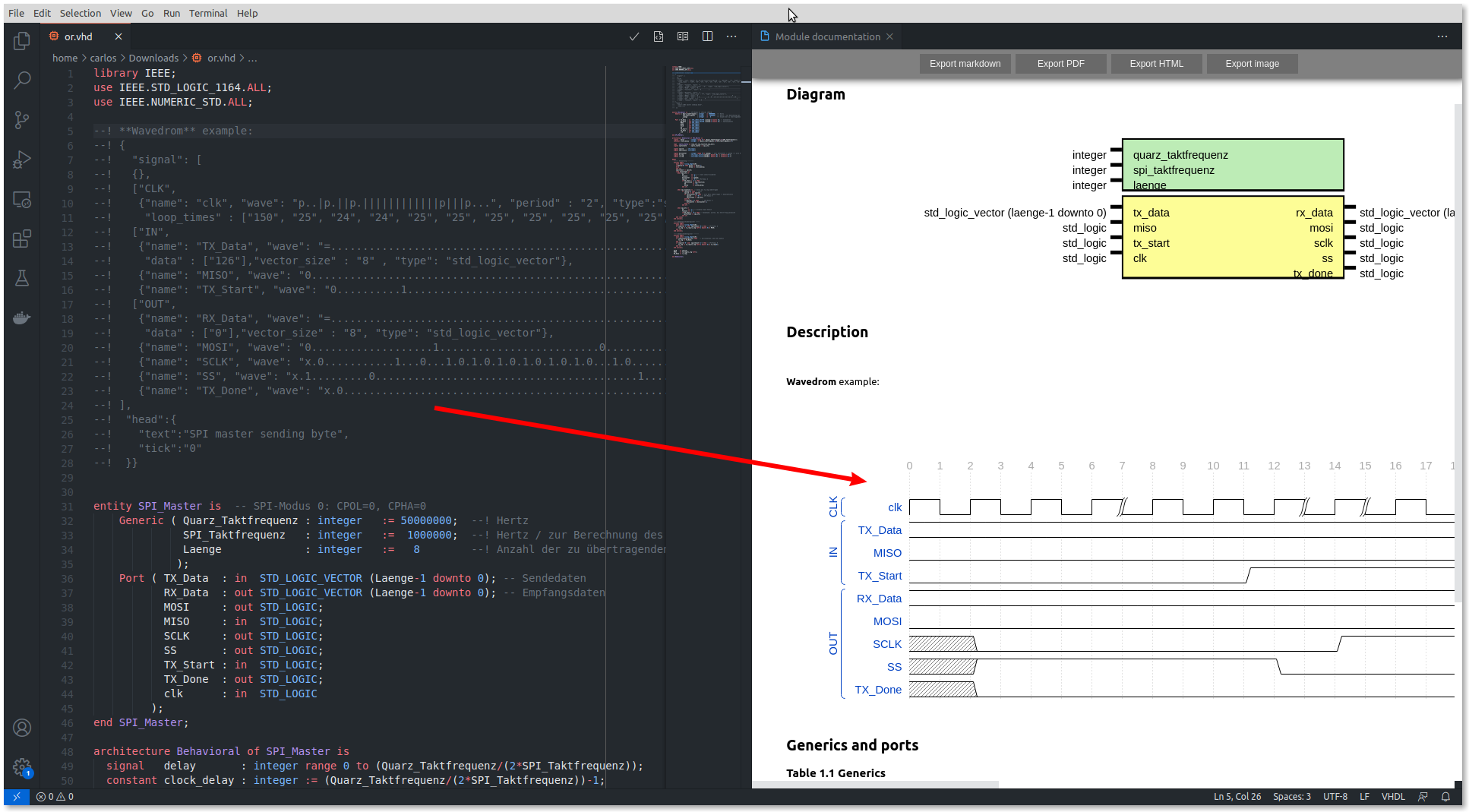

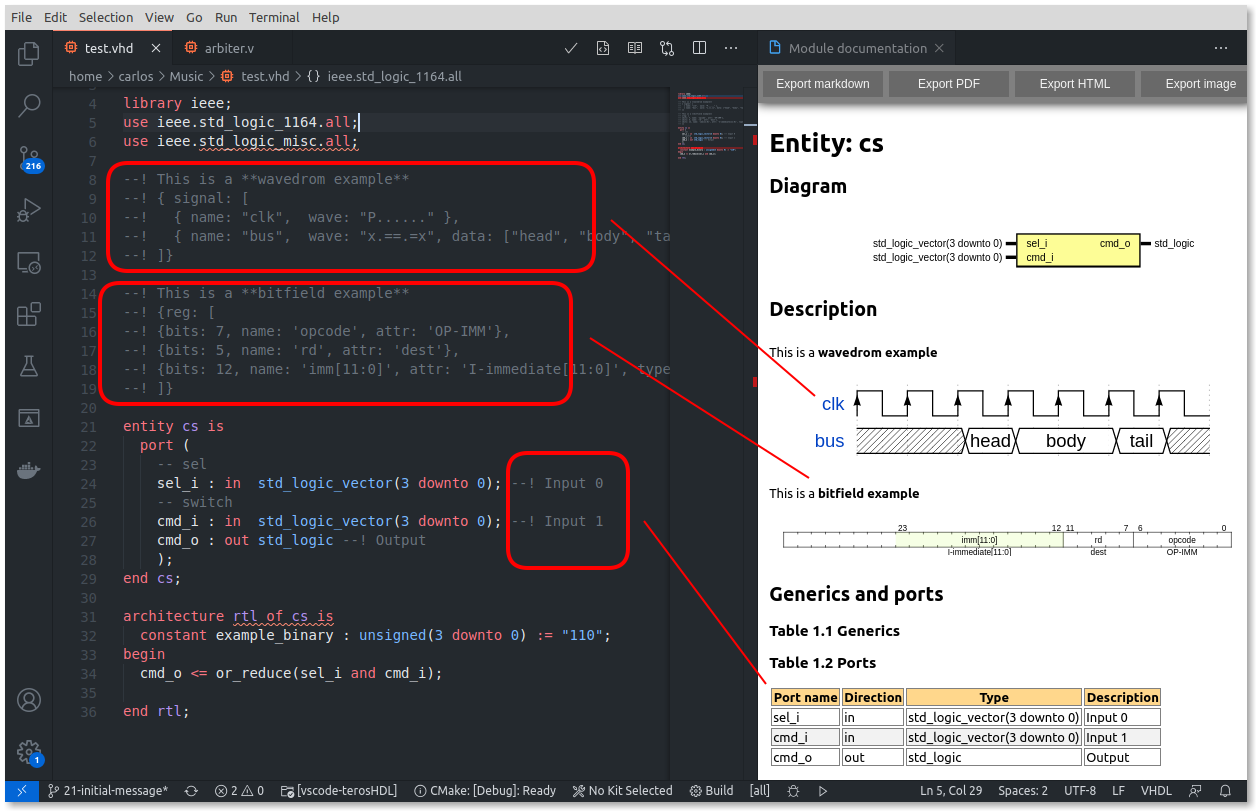

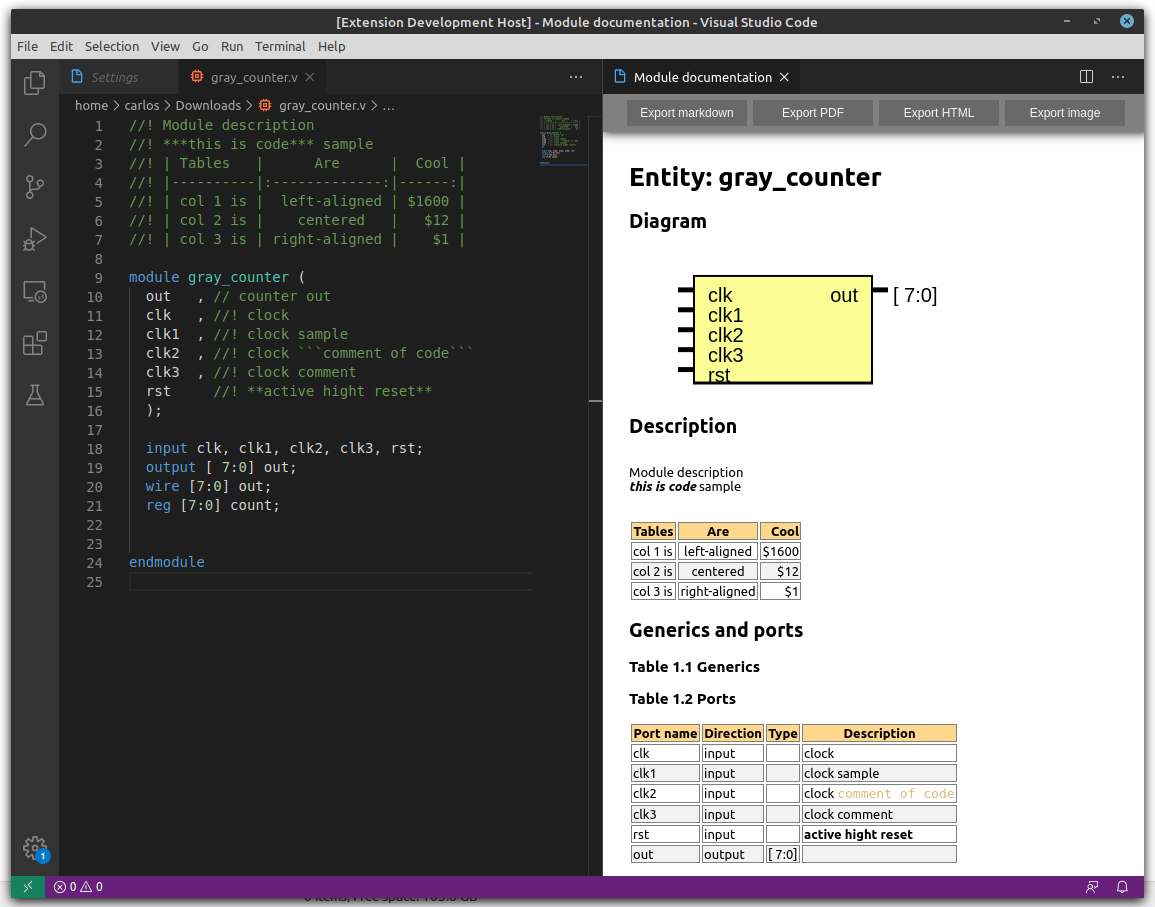

You can configure what symbol will be used to extract the comments in the HDL file. It supports MarkDown style. In the following example is used the symbol "!":

--! This is a description

--! of the entity.

entity counter is

port (

clk: in std_logic; --! Clock comment

out_data: out std_logic --! Description **port comment**

);

end counter;

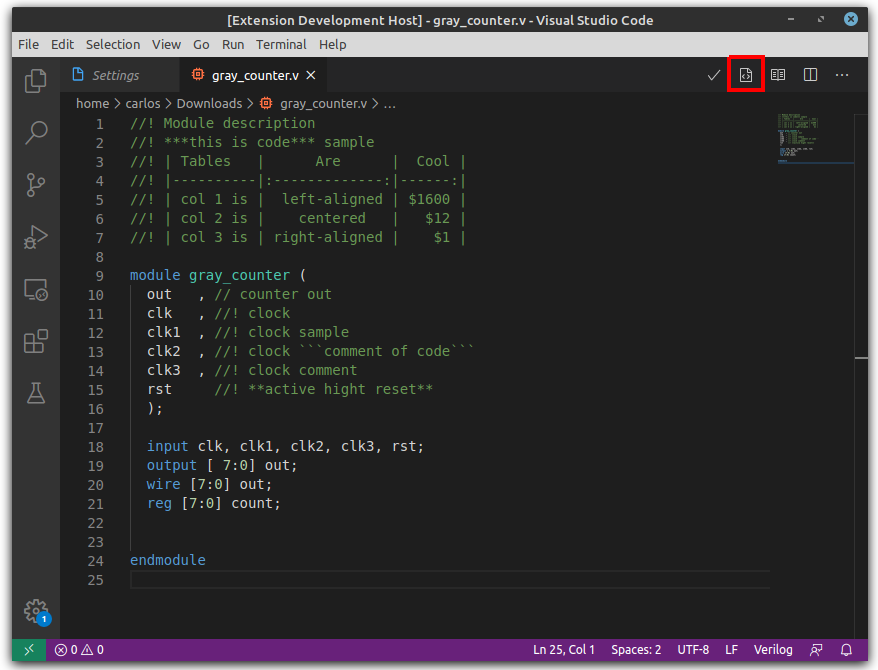

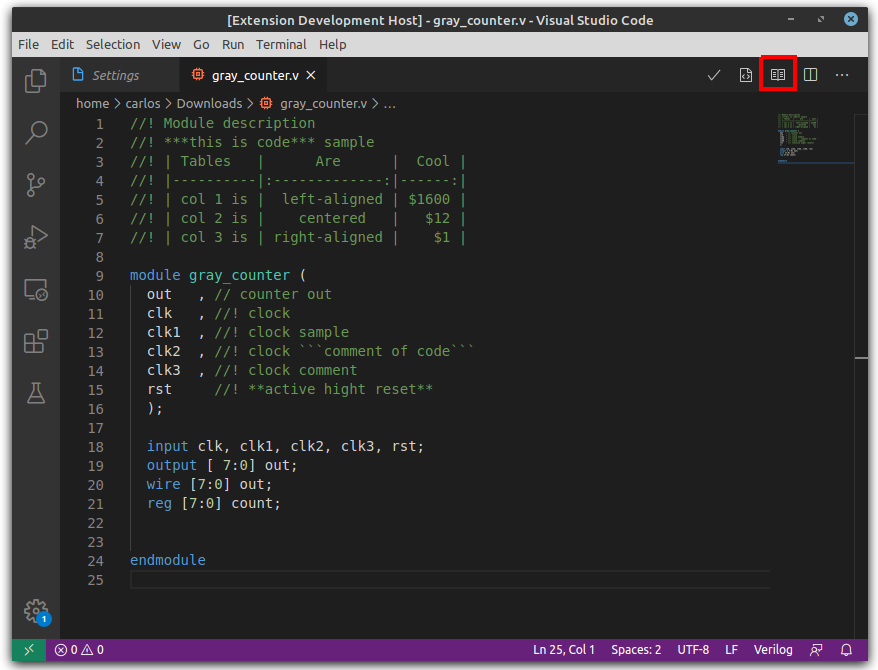

- Open a VHDL/Verilog file.

- Select the documenter icon.

- TerosHDL will show the generated documentation.

- Export your documentation to PDF, Markdown, HTML or SVG diagram.

- Edit your VHDL/Verilog file and save it. The preview will show automatically.

TerosHDL supports WaveJSON format in the module description, a format that describes Digital Timing Diagrams:

https://wavedrom.com/tutorial.html

https://observablehq.com/collection/@drom/bitfield

You need to install manually the simulators.

| Verilog | VHDL |

|---|---|

| ModelSim | ModelSim |

| Vivado | Vivado |

| Icarus | GHDL |

| Verilator |

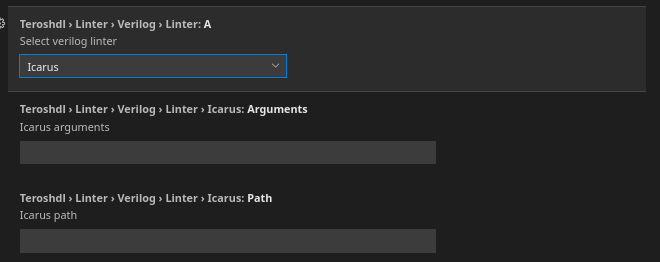

One of the above tools has to be installed to enable linter functionalities in a language. If the tool can not be find in the system path it has to be configured in the plugin config:

Configuration example for verilog:

This is an experimental feature. You need to install Verible (https://github.com/google/verible)

| Verilog | VHDL |

|---|---|

| Verible | -- |

| Verilog | VHDL |

|---|---|

| iStyle | Standalone |

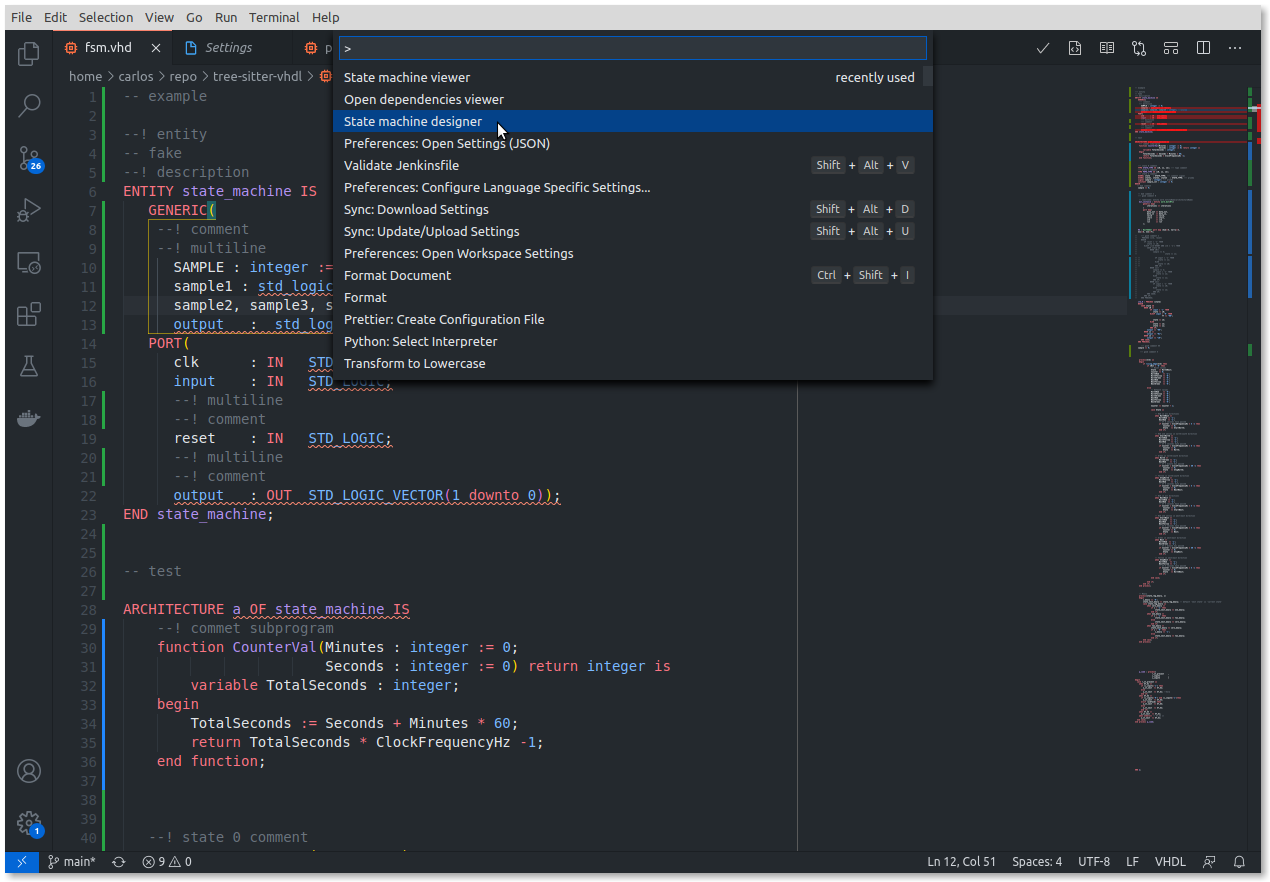

- Open the command palette:

Ctrl+Shift+Pand select State machine designer

- Follow the instructions and design your state machine!

- Install Python3.

- Go go TerosHDL configuration and add the Python3 binary path.

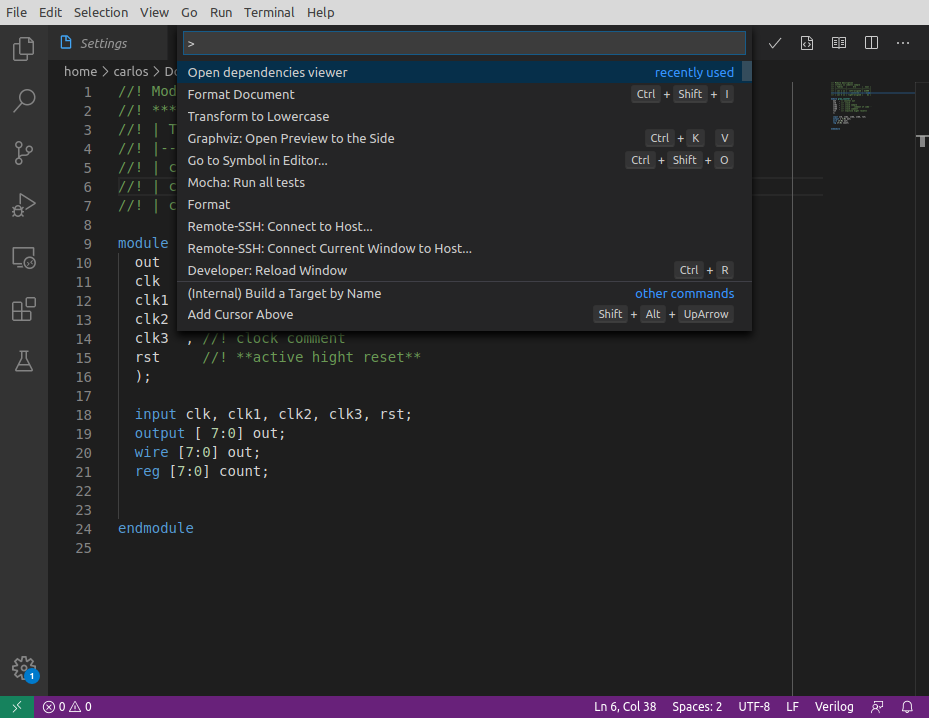

- Open the command palette:

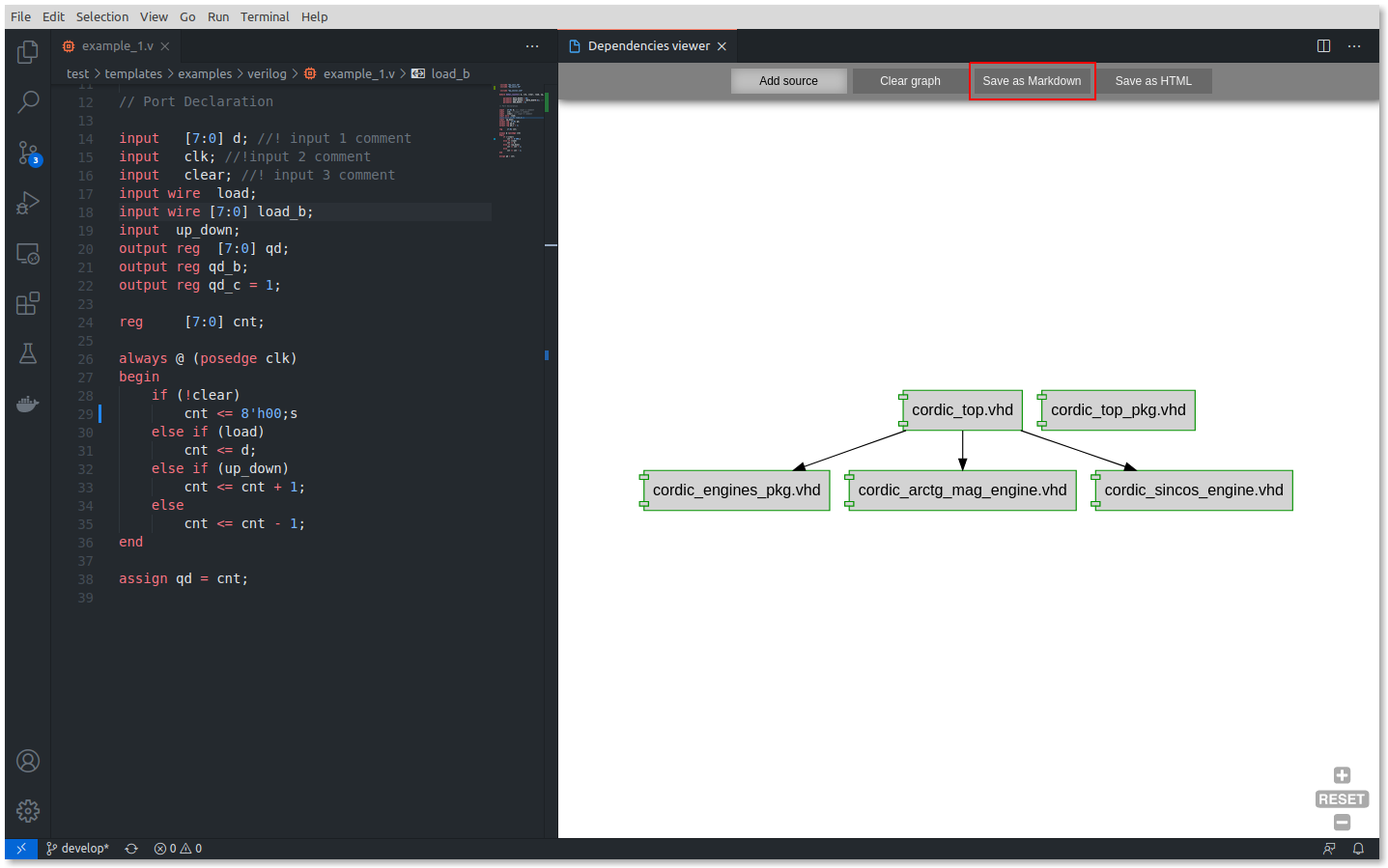

Ctrl+Shift+Pand select Open dependencies viewer

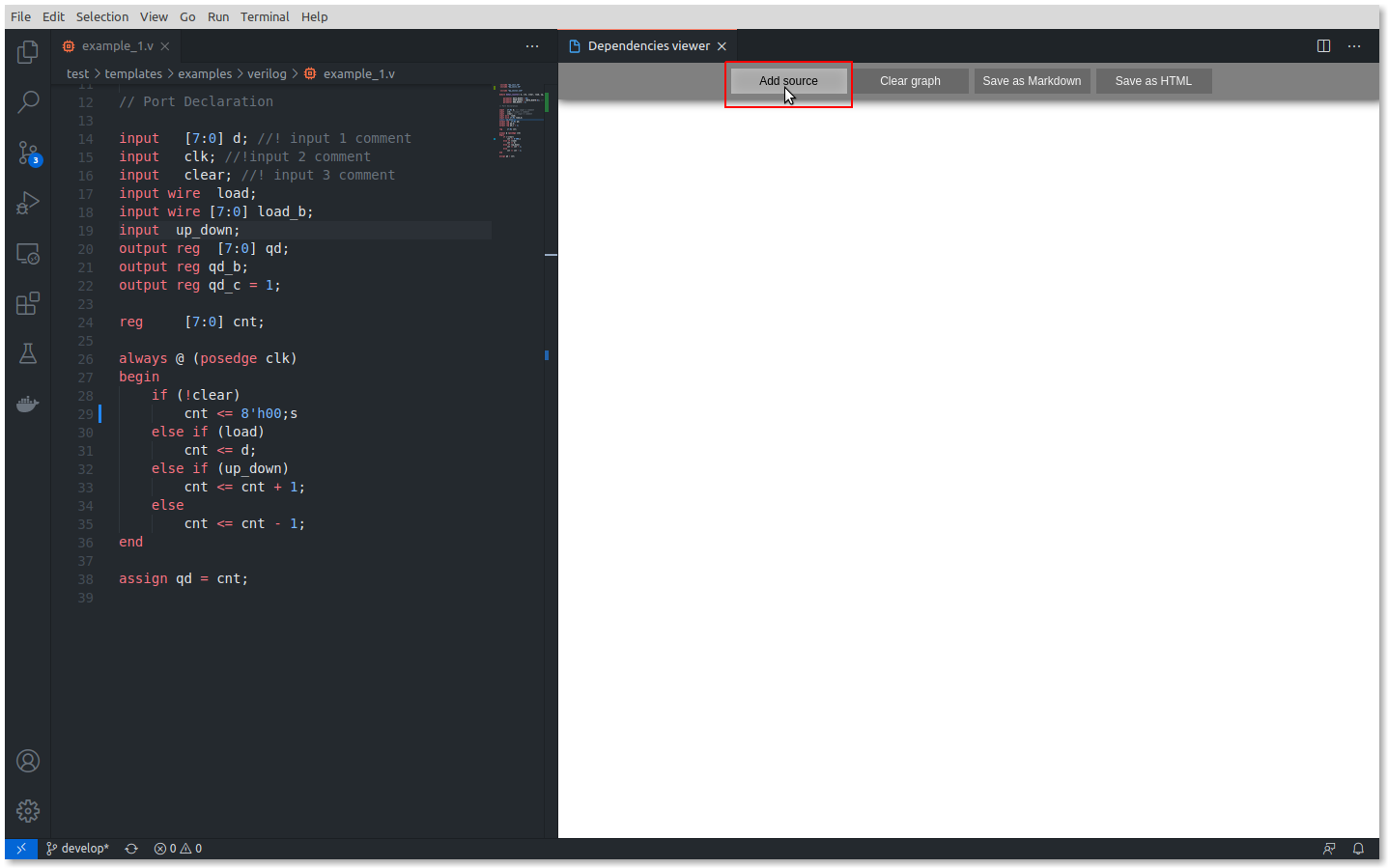

- Add a HDL files to the viewer (you can mix verilog and VHDL).

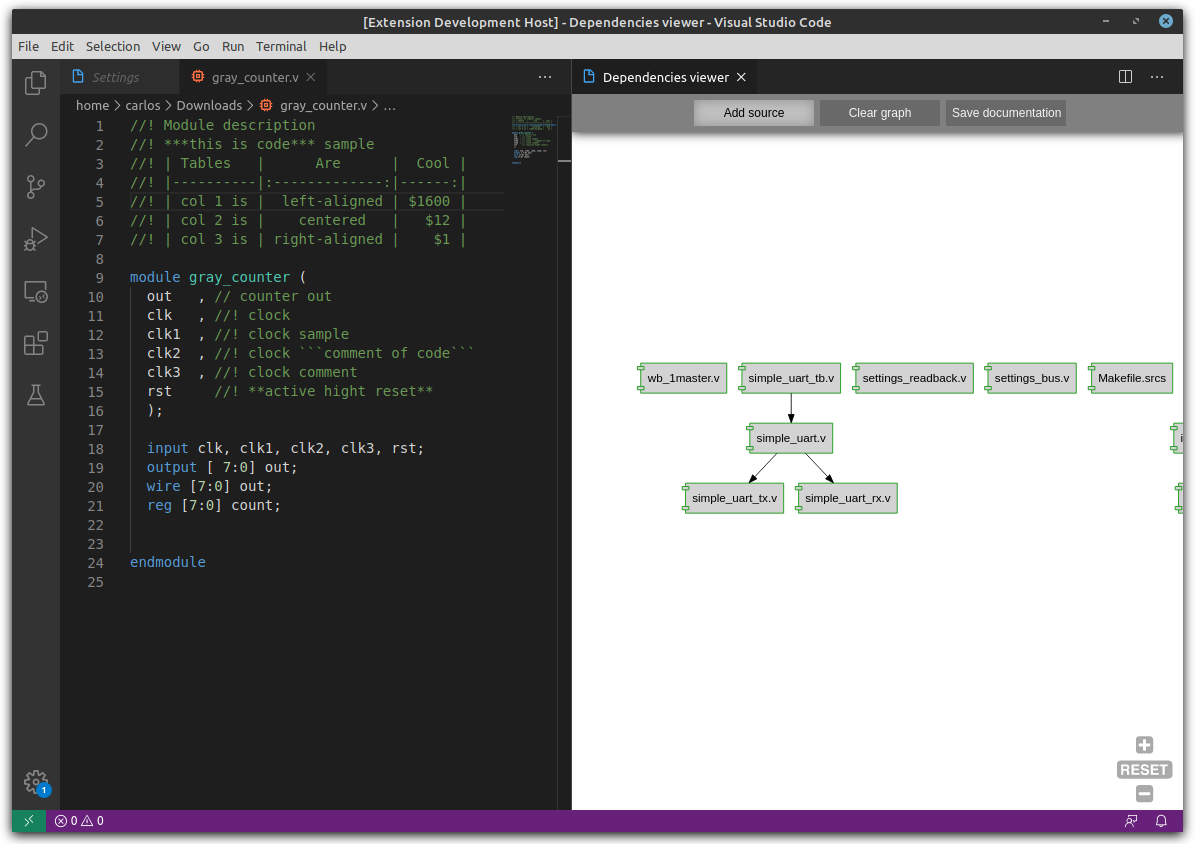

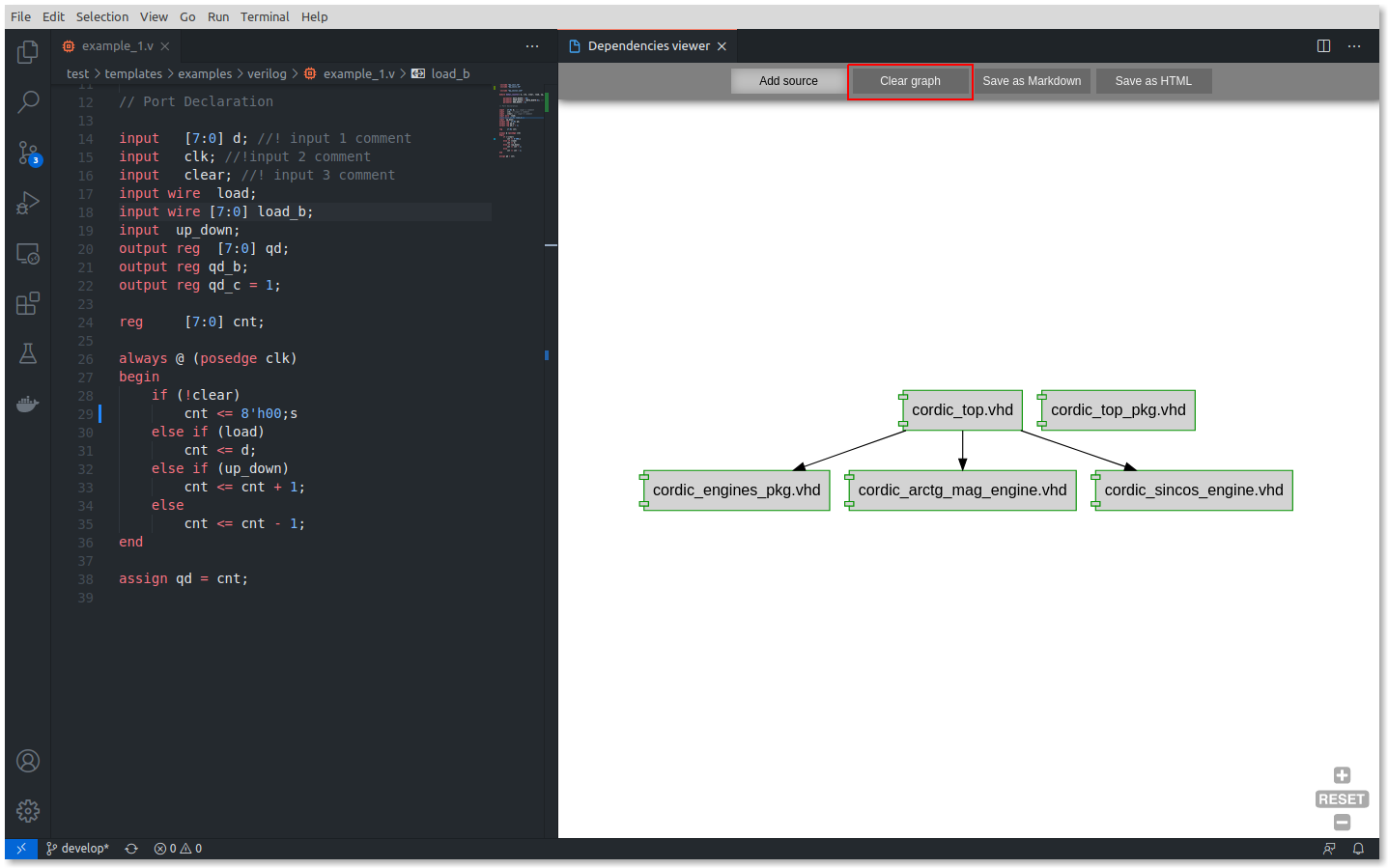

- TerosHDL will generate the dependencies graph:

- You can reset your viewer:

- You can generate the indexed Markdown documentation for all the files.

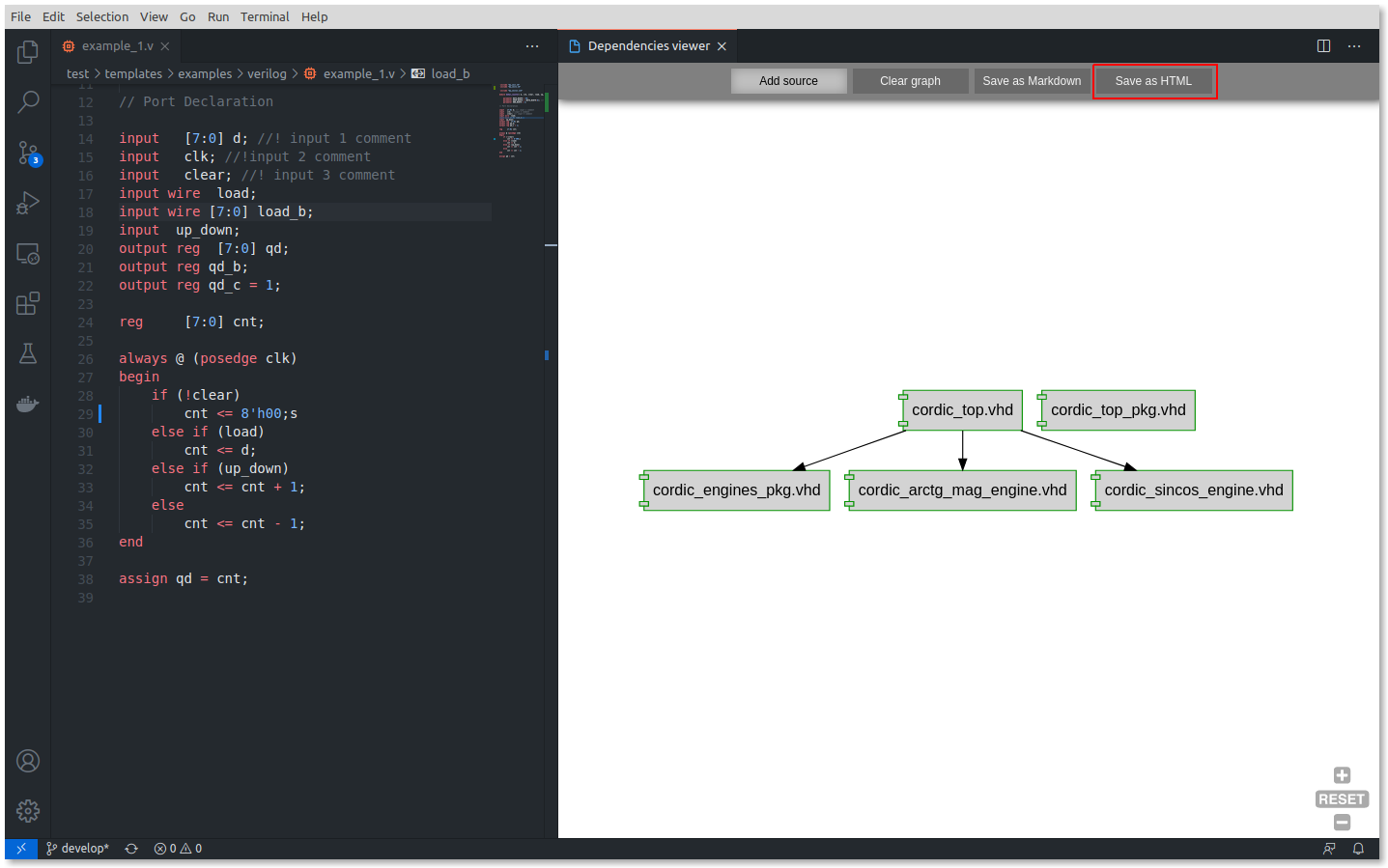

- And the indexed HTML documentation.

- Result in HTML format:

| Language | Grammar | Code snippets |

|---|---|---|

| Verilog | ✔ | ✔ |

| System Verilog | ✔ | ✔ |

| VHDL | ✔ | ✔ |

| XDC/SDC | ✔ | ✔ |

| ucf | ✔ | ✘ |

For a full description visit the documentation web.

- Project manager improvements.

- File tree view.

- Integrate triel