- Fully implemented RV32I instruction set

- Ziscr extension (under development)

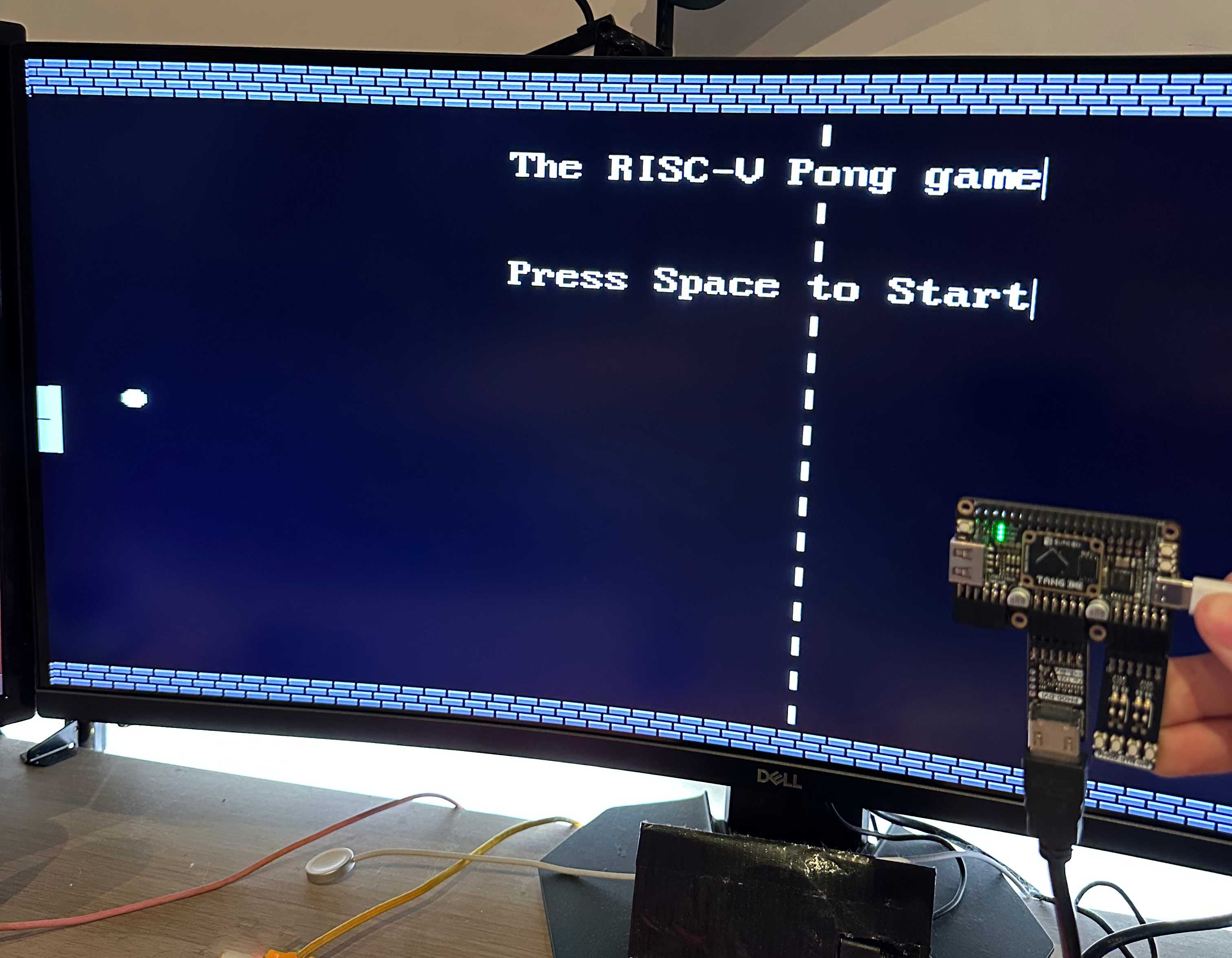

- HDMI and 40-pin LVDS display interfaces

- USB keyboard interface with a softcore microcontroller

- GCC Compiler and Scripts utilized for writing code and compiling it for our system

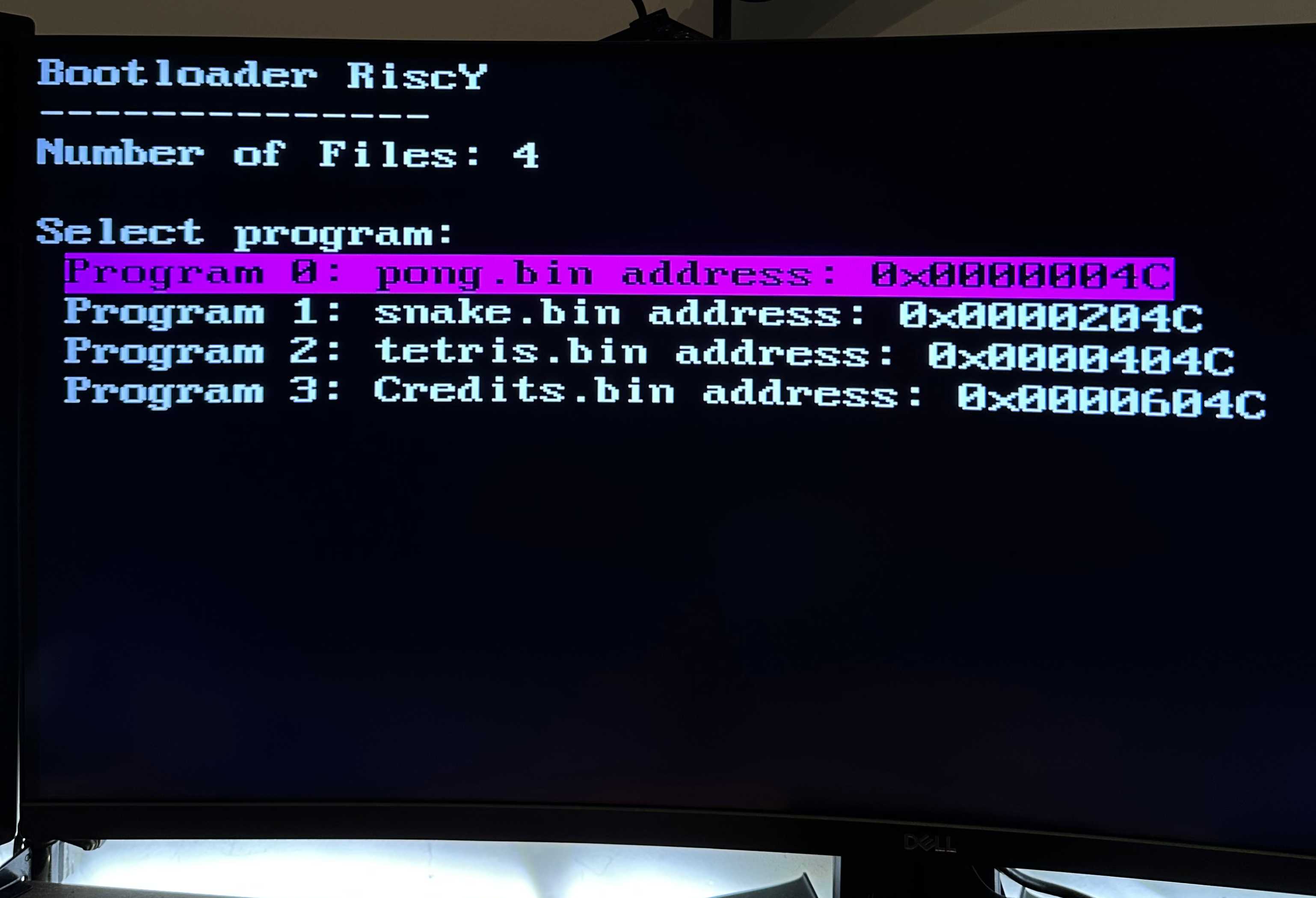

- Simple startup and program selector that loads programs from flash memory

- Gowin IDE version 1.9.10 or higher

- openFPGALoader

- Flash the Bitstream:

- Use the Gowin IDE to program the FPGA with the provided bitstream for either the Tang Nano 9k or Primer 25k.

- Burn Program Files to Flash:

- Utilize the

merger.pyscript to merge your program files. - Burn the merged program files to the flash memory.

- Utilize the

- Startup:

- Power on the FPGA board; the system will initiate the simple startup program.

- Program Selector:

- Choose from multiple programs stored in flash using the program selector interface.

- Interfaces:

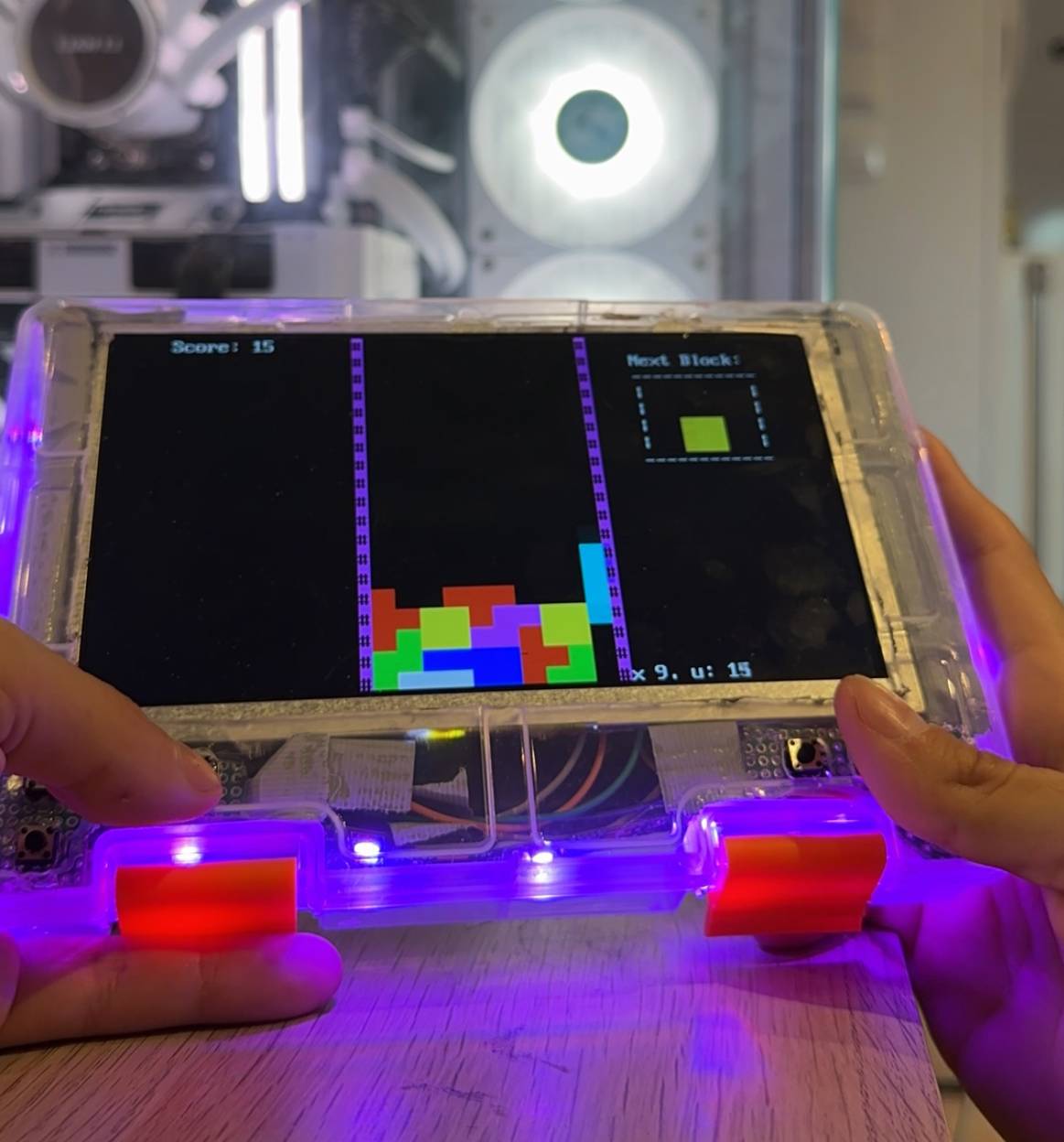

- Display Output: Connect via HDMI or the 40-pin LVDS display.

- Input Devices: Use a USB keyboard through the softcore microcontroller interface.

You can also see the documentation of our project (https://nanousis.com/riscY/documentation/)

- Gowin IDE (version 1.9.10 or higher): Download Here

- openFPGALoader: GitHub Repository

Developed at the University of Thessaly.

Contributions are welcome! Feel free to open an issue or submit a pull request.

For any questions or support, please open an issue in this repository.