An OSHW (Open-Source Hardware) FPGA (Field-Programmable Gate Array), initially running in its own online circuit simulator.

This operates under the CERN-OHL-P licence.

The first online presence for this project, is/was freedom.is/svg

- Currently converting parts of the original website into documentation here.

- Developing a new tool to generate complex SVG faster.

The previous slow generation of SVG diagrams, held up this documenting process for a while.

Rather untidily banged in here, starting from my talk at php-sw, in April 2024.

Documentation Restart

- Transcript

- Collection of slides to bung in. These will be integrated, eventually.

- Test page, for the slides.

Roadmap

- Newstyle Roadmap

- Done (Refumbled documentation from talks)

- Ongoing

- Future Plans

- Oldstyle Roadmap (Old structured documentation)

Main documentation, experimentally also merged into this readme:

Verilog syntax highlighting test

module Example_counter

#(parameter WIDTH=64,NAME="world")

(input clk,

output reg [WIDTH-1:0] q);

...(The above code has nothing to do with this project.)

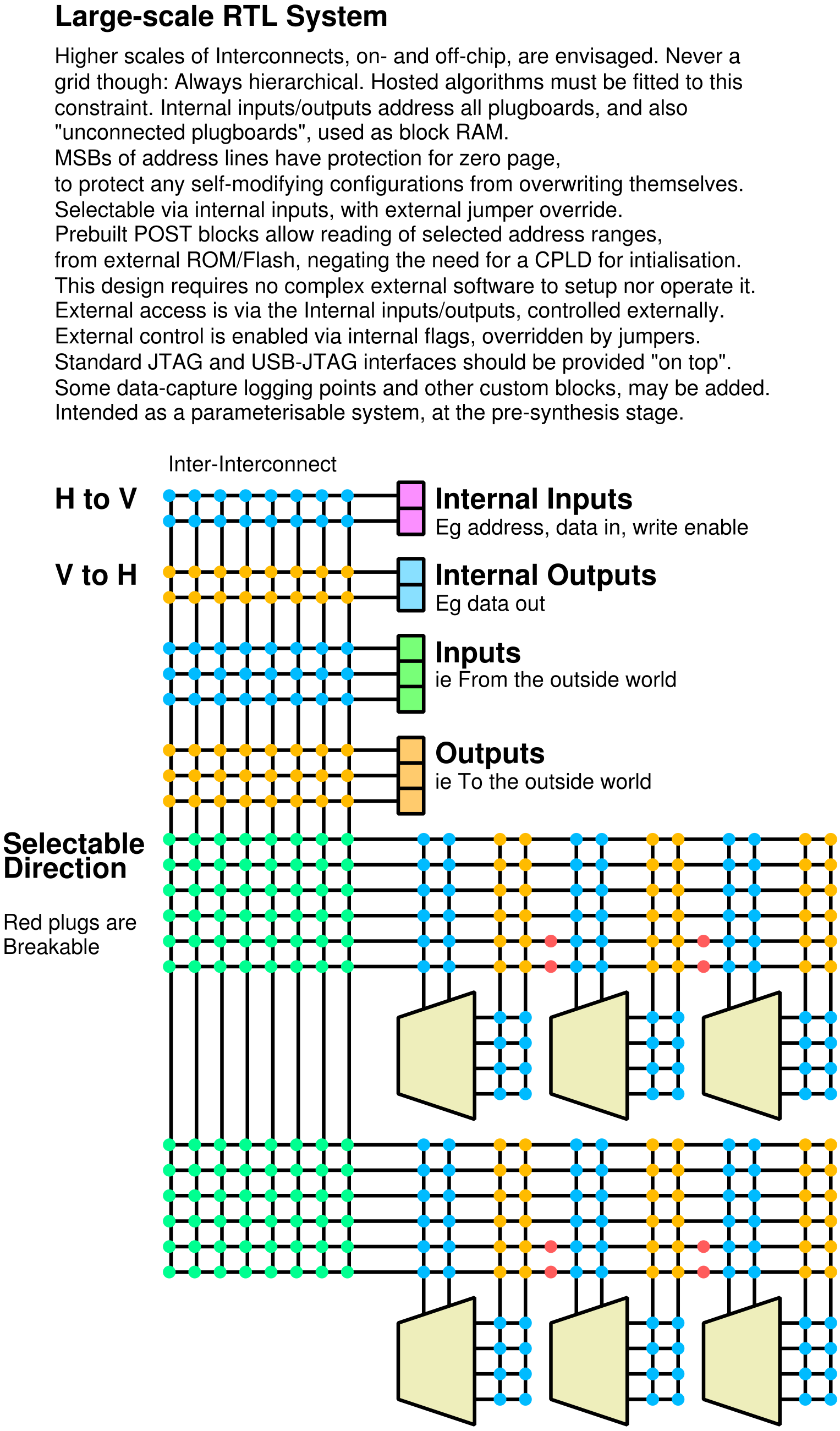

Large-scale RTL plan/explanation of my FPGA design

(Added 23/5/2023)You can also download this as a PDF: Click on the download rawfile button.