This repository contains:

- Unit Simulations of Individual Gates in HDL21

- Integration Simulations of the Multiplier in HDL21

- Complete Implementation in Verilog for OpenROAD Layout

- Special GDS Post-Processing + Simulation for this Design

- The Final Layout

Oscillator-Based Ising Machines combine Ising Machines with the inhomogeneous Kuramoto model of systems of oscillators with weights.

The Ising Machine is defined by the Hamiltonian:

where si is the spin of particle i. The probability of the system being in a particular state is given by the Boltzmann distribution:

where

Using these facts, we can start designing

However, this is a pretty mathematical machine, not a tangible engineering concept - so how exactly do we implement this in hardware? The answer is that we rely on the inhomogeneous Kuramoto model on a system of oscillators, this is defined by the differential equation:

assuming oscillators have neglible difference in natural frequency, where

We know that this model has steady states by its global Lyanpunov function given by:

The Lyapunov energy given here can be interpreted as an Ising Hamiltonian, where energy is minimized by having coupled oscillators with a positive coupling strength have the same phase (

Luckily enough, the correspondance between weights in the Ising Machine and coupling strengths in the Kuramoto model is one-to-one, so we can use the same weights we found in the Ising Machine to implement the Kuramoto model.

The bulk of wobblchip's design is to achieve two goals, digital I/O and deterministic oscillator coupling.

To encode digital signals into oscillators, we need a way to couple oscillators that guarantee that the oscillators are in-phase with a reference oscillators when that oscillator represents a 0 and in anti-phase when that oscillator represents a 1.

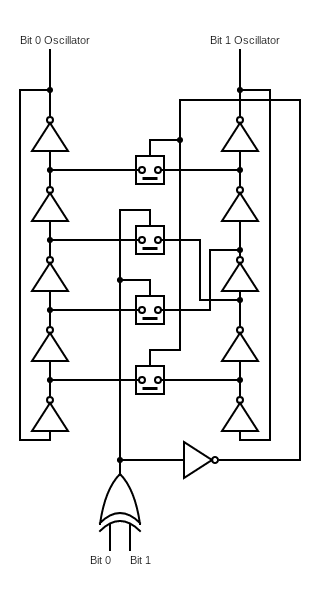

The basic method of coupling two oscillators so that they are "in-phase" or in "anti-phase" is shown in the circuit diagram below.

A few technical notes worth emphasizing in this design:

-

The analogue switches shown here are implemented using a typical transmission gate with single activation design that reflects the drive strength of unit-strength high-density SKY130 digital cells.

-

The general rule of thumb is that each inter-stage node in either oscillator should only support one kind of coupling analogue switch (symmetric or antisymmetric).

-

However, to avoid timing issues including fixed phase biases and dynamic phase drift - each coupling must actually be a pair of couplings, we see this the diagram.

-

More subtly, the antisymmetric coupling must take place across the same pair of nodes in either oscillator (ie. a coupling 1 → 2 and 2 → 1 is fine, 1 → 2, 4 → 3 is not)

This structure is repeated for the number of bits required, with the final unit removing the XOR-gate for a buffer which just repeats the value of the final bit - this controls the coupling between the final-bit oscillator and the reference oscillator.

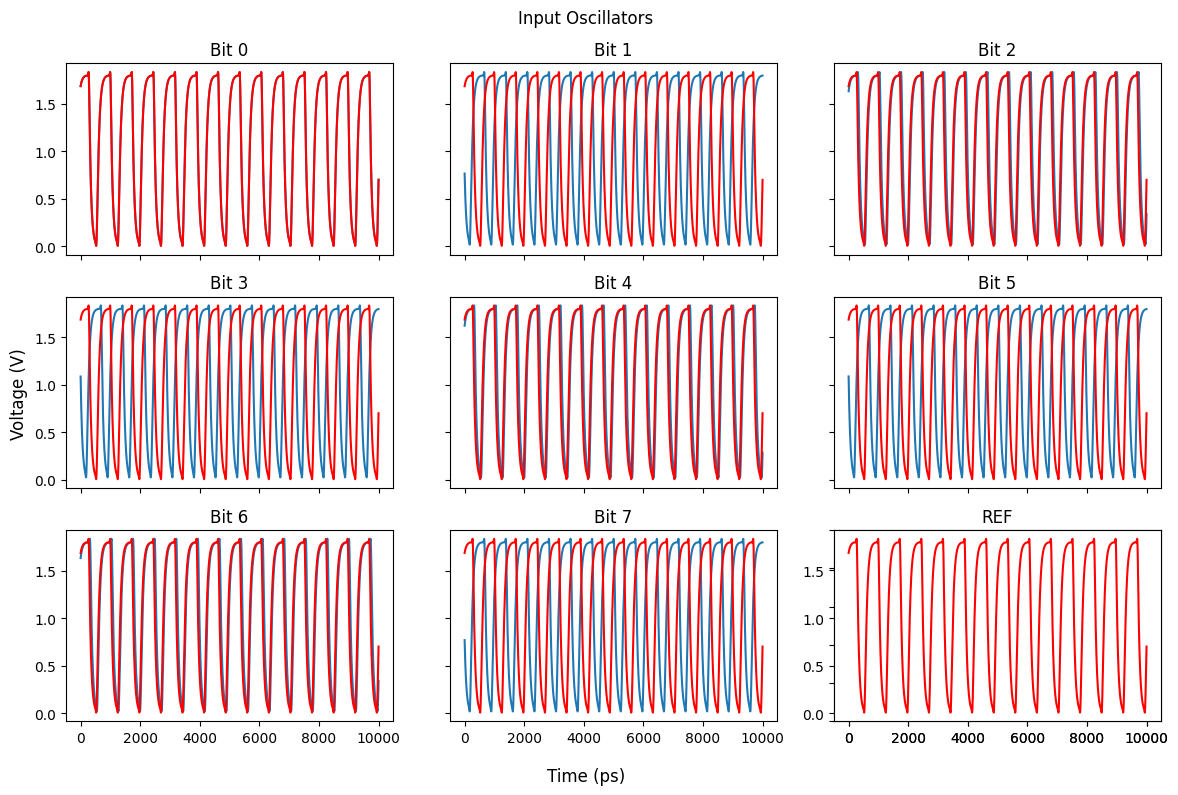

The final oscillator signal for each bit and reference is coupled to the internal oscillator circuitry using a standard resistor "COPY gate" and should produce signals like this example for 170 in 8-bits:

wobblchip is an oscillator-based implementation of Kamsari et al.'s sparse-Ising Machine multiplier (sIM-multiplier) - as such we only need replicate 4 logic circuits:

- COPY Gates

- AND Gates

- Half Adders

- Full Adders

We'll move onto the specifics of implementation after noting a couple theoretical tricks that are needed to realize them:

The Linear Programming methods used to compute the structure Ising model logic gates are given by the Hamiltonian which is minimized in "valid logic states" (eg. expected behavior of an AND gate should minimize this Hamiltonian in its Ising model):

Where

We can rearrange the Hamiltonian like so:

This gives us a symmetric matrix filled with coupling weights we can now use to program our oscillator systems which represent the logic gates we are interested in.

As the coupling is predetermined, we can instead use fixed resistors to connect oscillators together, we do this in the following process:

-

Determine a unit resistor that we subdivide to get a multiplier of its conductance.

-

Oscillators must be coupled in in-/anti-phase configuration using the method described above to prevent timing issues.