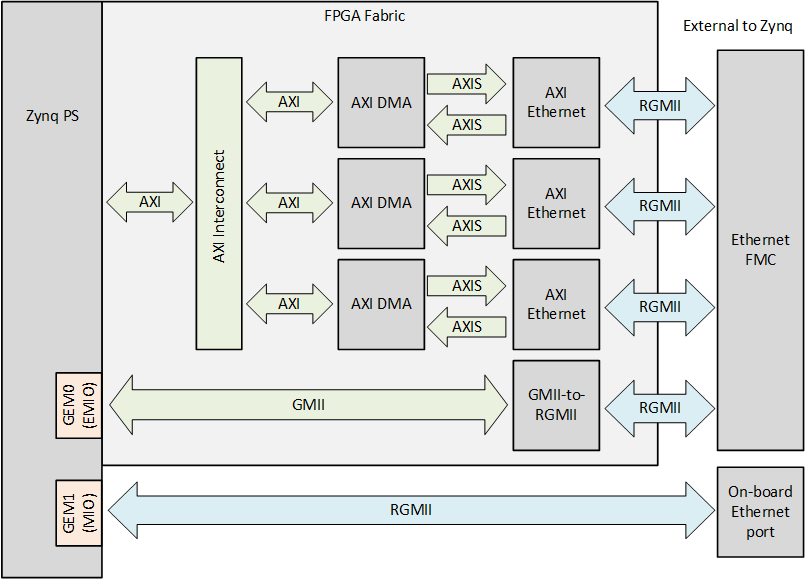

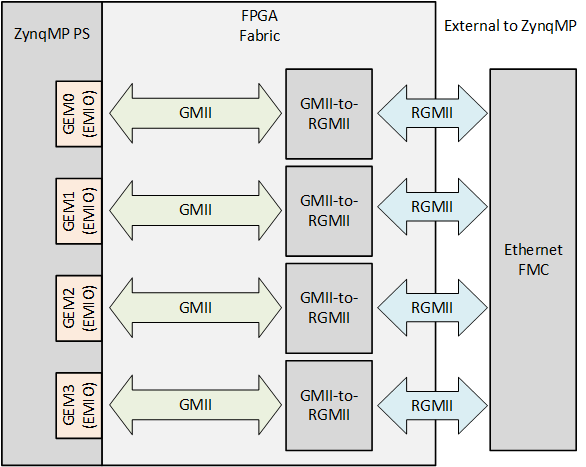

This project demonstrates the use of the Opsero Quad Gigabit Ethernet FMC. The design uses the GMII-to-RGMII IP core to connect the hard GEMs of the Zynq PS to the Ethernet FMC PHYs. The designs target both the Zynq and ZynqMP devices and are illustrated by the block diagrams below.

Important links:

- The user guide for these reference designs is hosted here: Zynq GEM for Ethernet FMC docs

- To report a bug: Report an issue.

- For technical support: Contact Opsero.

- To purchase the mezzanine card: Ethernet FMC order page.

This project is designed for version 2020.2 of the Xilinx tools (Vivado/Vitis/PetaLinux). If you are using an older version of the Xilinx tools, then refer to the release tags to find the version of this repository that matches your version of the tools.

In order to test this design on hardware, you will need the following:

- Vivado 2020.2

- Vitis 2020.2

- PetaLinux Tools 2020.2

- Ethernet FMC

- One of the supported evaluation boards

- For designs containing AXI Ethernet Subsystem IP: Xilinx Soft TEMAC license

We encourage contribution to these projects. If you spot issues or you want to add designs for other platforms, please make a pull request.

This project was developed by Opsero Inc., a tight-knit team of FPGA experts delivering FPGA products and design services to start-ups and tech companies. Follow our blog, FPGA Developer, for news, tutorials and updates on the awesome projects we work on.