Welcome to the uPIMulator Framework Documentation!

This documentation serves as your comprehensive guide to the uPIMulator framework, catering to both novice and experienced researchers. Here, you'll find the resources necessary to leverage uPIMulator effectively for your research projects.

We provide in-depth coverage of uPIMulator's features, from foundational concepts to advanced functionalities. Explore this documentation to unlock the full potential of uPIMulator and elevate your research endeavors.

KAIST, School of Electrical Engineering

Vertically Integrated Architecture Research Group

Office: N1 818 @ KAIST

- Bongjoon Hyun: bongjoon.hyun@gmail.com

- Taehun Kim: taehun.kim@kaist.ac.kr

- Dongjae Lee: dongjae.lee@kaist.ac.kr

- Minsoo Rhu: minsoo.rhu@gmail.com

Please feel free to reach out to us if you have any questions or require further assistance.

uPIMulator: A Flexible and Scalable Simulation Framework for General-Purpose Processing-In-Memory (PIM) Architectures

uPIMulator is a cycle-level performance simulator tailored for general-purpose Processing-In-Memory (PIM) systems adhering to the UPMEM Instruction Set Architecture (ISA). This tool provides a detailed simulation environment, empowering computer architecture researchers and PIM program developers to investigate and harness the capabilities of PIM technology.

For comprehensive insights into uPIMulator and its applications, we invite you to refer to our HPCA-2024 publication:

"Pathfinding Future PIM Architectures by Demystifying a Commercial PIM Technology", HPCA, 2024

Currently Available Versions are:

- Python & C++ version

- Go version

- Go & virtual machine version

All source code and version history can be accessed in our GitHub repository.

This was our initial implementation of uPIMulator, used in our HPCA-2024 publication.

You'll find it in the python_cpp directory. Refer to the included README for usage instructions.

Our second implementation, optimized for speed and memory efficiency.

Located in the golang directory, it offers an 8.5x speed increase and 7.5x memory reduction due to multi-threading.

We generally recommend this version for most use cases. See the README for details.

This latest version extends the Go version with virtual machine capabilities, eliminating the need for manual data preparation code in many scenarios. It's particularly suitable for complex or dynamic benchmarks where manual data preparation is challenging, though it may not offer the fastest simuation speed. Refer to the README for further guidance.

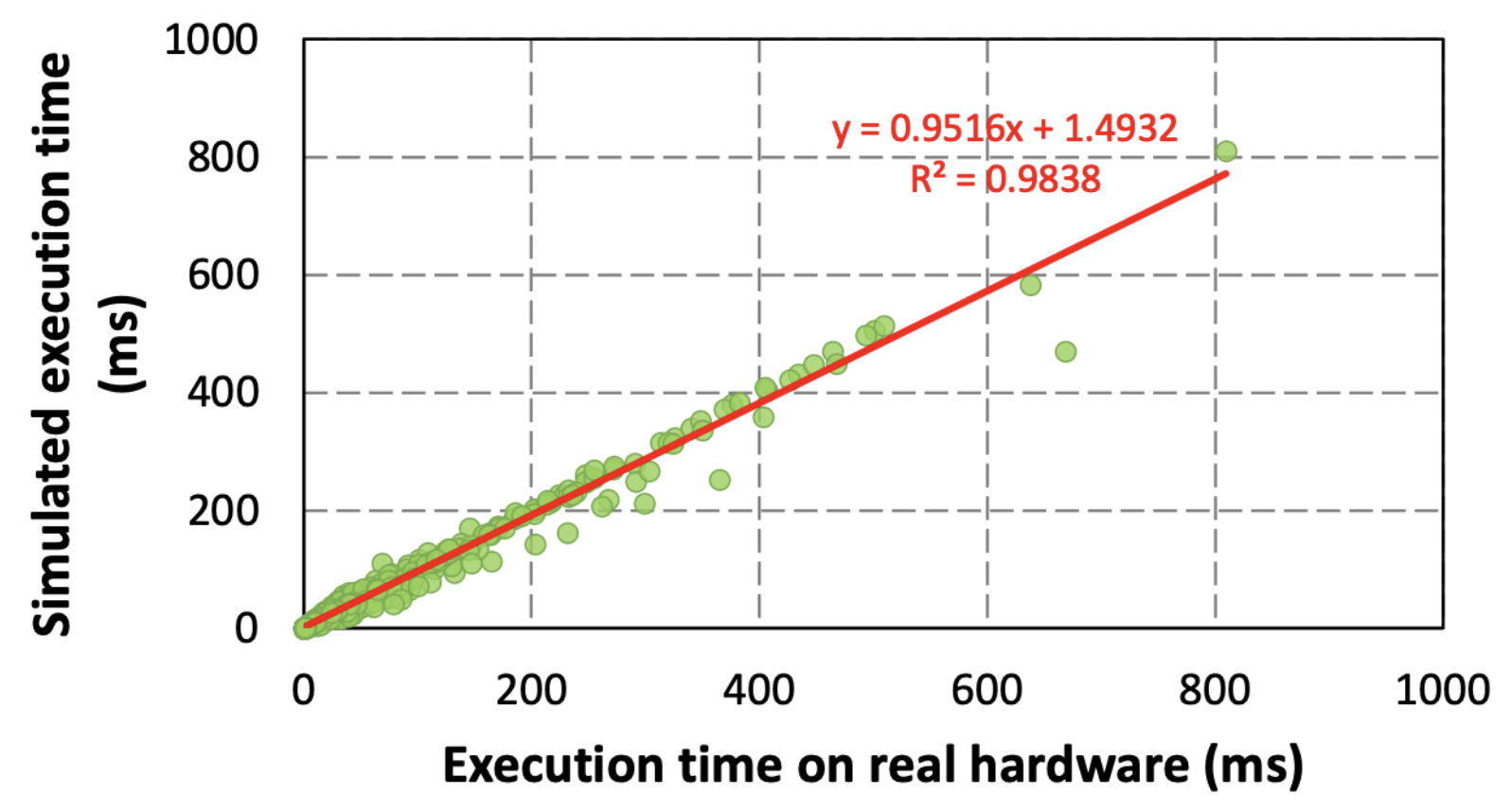

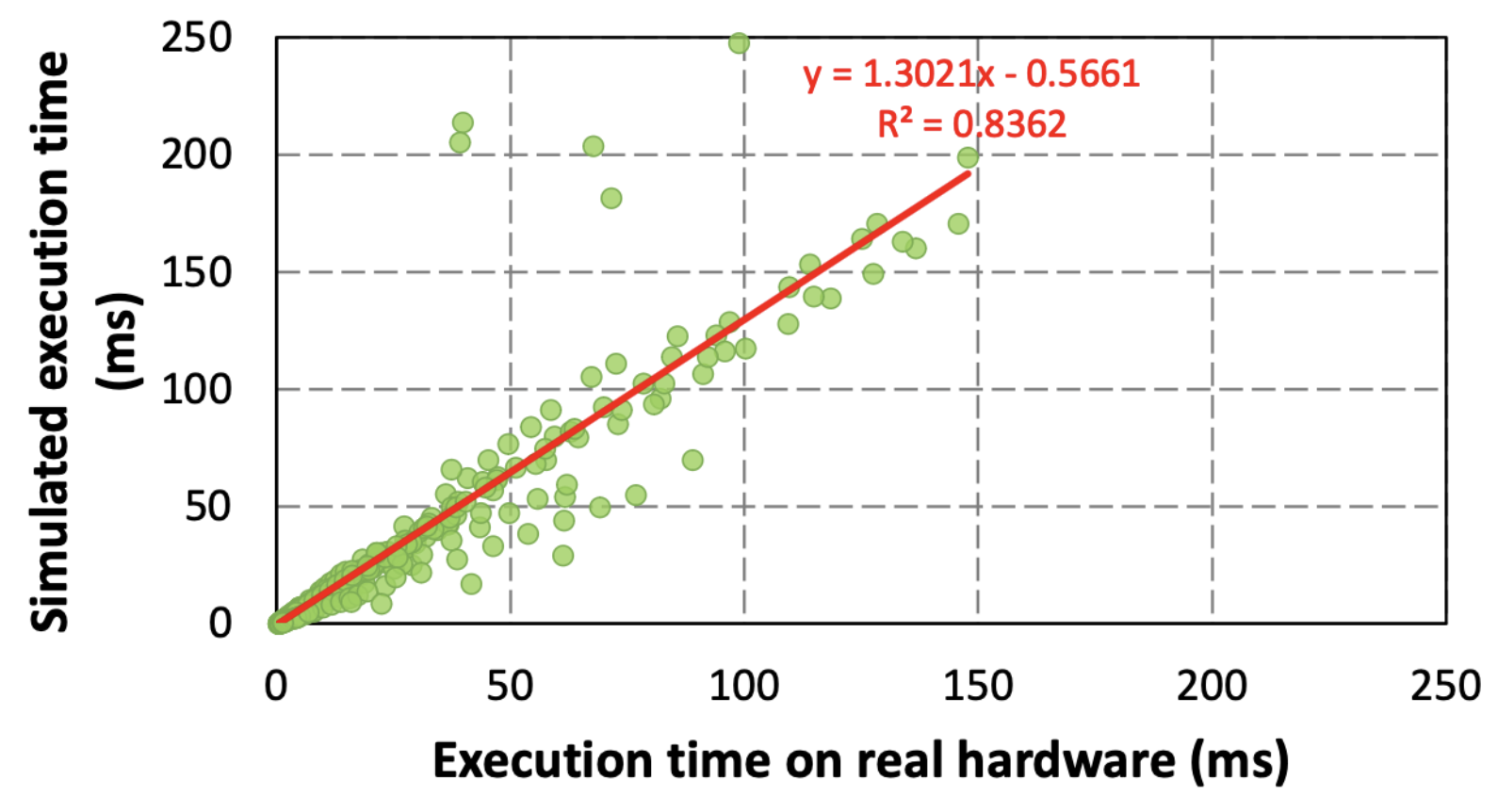

- Each data point represents a single kernel from the PrIM benchmark suite.

- Summary of Correlation Ratio (R²) and Mean Absolute Error (MAE) for single- and multi-DPU simulations:

| Scenario | Total Data Points | Correlation (R²) | MAE |

|---|---|---|---|

| Single DPU (no inter-DPU communication) | 710 | 98.4% | 12.0% |

| Multi-DPU (with inter-DPU communication) | 387 | 83.6% | 26.9% |

- The validation results were obtained using the Python & C++ version of uPIMulator.

-

uPIMulator currently supports 599 out of the 970 instructions defined in the UPMEM-PIM ISA. Due to limitations in the publicly available ISA documentation, support for the remaining 371 instructions is pending. However, the currently supported instructions have been sufficient to enable functionally correct simulations of the PrIM benchmark suite, producing results consistent with those obtained on real UPMEM-PIM hardware.

-

For a detailed list of the currently supported instructions, please refer to this Google spreadsheet.

- Bongjoon Hyun, Taehun Kim, Dongjae Lee, and Minsoo Rhu, "Pathfinding Future PIM Architectures by Demystifying a Commercial PIM Technology", The 30th IEEE International Symposium on High-Performance Computer Architecture (HPCA-30), Edinburgh, Scotland, Mar. 2024

${\textsf{\color{red}Best Paper Award}}$ - Acceptance rate: 18% (75 among 410)

- Slide

- Presentation

We welcome and encourage contributions to uPIMulator! If you are interested in contributing or have questions, please feel free to open an issue or submit a pull request.

- Bongjoon Hyun (bongjoon.hyun@gmail.com)

- Taehun Kim (taehun.kim@kaist.ac.kr)

- Dongjae Lee (dongjae.lee@kaist.ac.kr)

- Minsoo Rhu (minsoo.rhu@gmail.com)

We would like to thank the developers of the PrIM benchmark suite, which was instrumental in developing this project.

This research is funded by the generous support from the following organizations:

- Institute of Information & Communications Technology Planning & Evaluation (IITP) grant funded by the Korea government(MSIT) (No. 2022-0-01037, Development of High Performance Processing-in-Memory Technology based on DRAM) and the Korea government(MSIT) (No.RS-2024-00438851, (SW Starlab) High-performance Privacy-preserving Machine Learning System and System Software)

- National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (NRF-2021R1A2C2091753)

- Samsung Electronics

We appreciate their commitment to advancing research in this field.

Bongjoon Hyun, Taehun Kim, Dongjae Lee, and Minsoo Rhu, "Pathfinding Future PIM Architectures by Demystifying a Commercial PIM Technology", IEEE International Symposium on High-Performance Computer Architecture (HPCA), March 2024.