This repository is our Computer Organization and Design course project that we had to create a MIPS pipeline simulator.

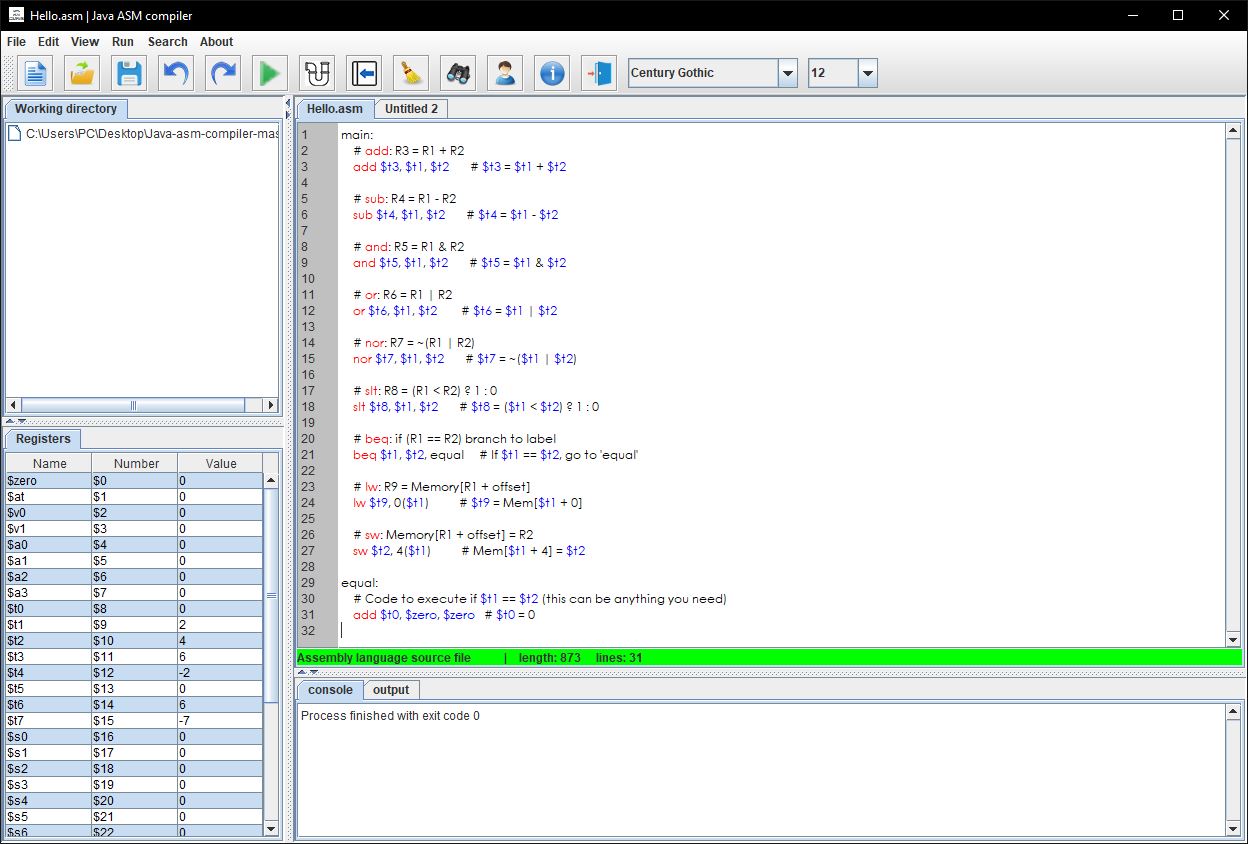

Main Window |

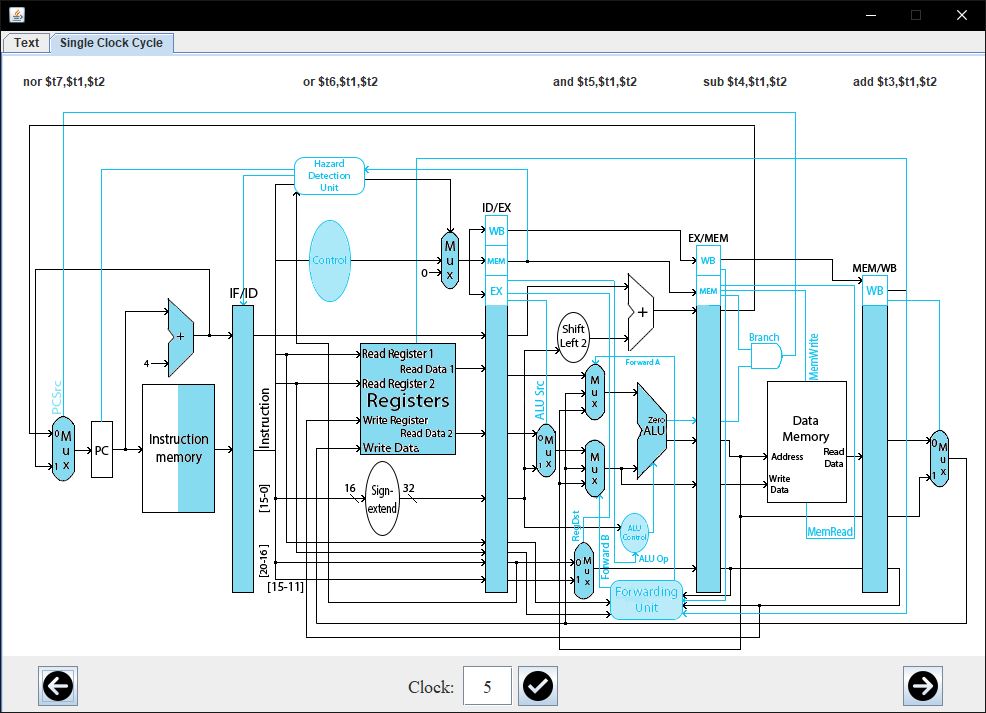

Pipeline Simulator |

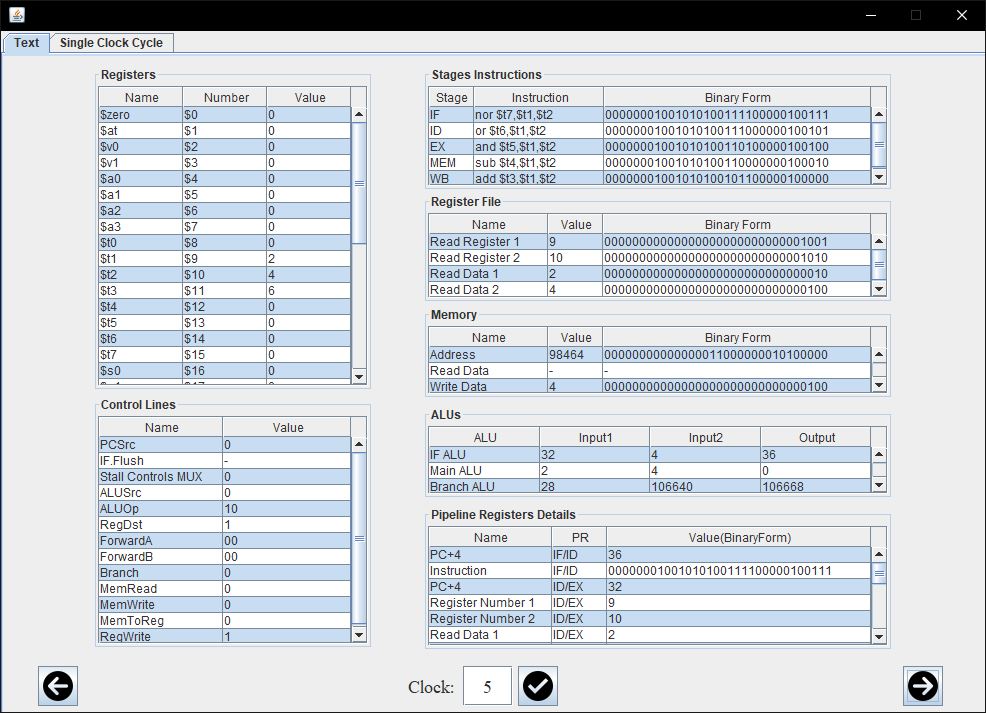

Pipeline Information |

Assembles and simulates 9 basic instructions (add, sub, and, or, nor, slt, beq, lw, sw) of the MIPS instruction set Our guideline reference for implementing the instruction set was Computer Organization and Design, Fifth Edition by Patterson and Hennessy.

Implemented exceptions for the project are:

- IllegalRegisterNumberException

- SymbolNotFoundException (for labels)

- UndefinedInstructionException (for unsupported instructions or wrong instructions)

- UnformattedInstructionException

Either

- Download the artifact and open the program

Or

- Clone the code, import it to the IDE of your choice, and run the JavaAsmCompiler.java file to open the program.

Then

- Write your MIPS code, click on the run button; if console displayed successful compile, click on pipeline button to display the simulation.

We had to develop this editor & emulator with many custom features that I listed some of them below:

- Editor features:

-

- Code color scheme

-

- predefine register's values

-

- User-friendly editor with common features

- Simulator features:

-

- All details of CPU pipeline in text and graphical view

-

- Single clock cycle diagram for CPU pipeline

-

- Forwarding Unit: Handles forwarding in execution stage

-

- Hazard detection unit in Instruction Detection (ID) stage: Handles lw data hazard with nop and beq control hazard using 3 bubble technique

MIPS (Microprocessor without Interlocked Pipelined Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by MIPS Computer Systems (an American company that is now called MIPS Technologies).

This project is open-source software licensed under the MIT license.