This repository contains a project developed as part of my bachelor thesis in Applied Informatics - Computer Science at the University of Macedonia. This simulation aims to illustrate the functioning of three distinct cache memory architectures: direct-mapped, fully associative with LRU (Least Recently Used) replacement policy, and set-associative with LRU.

As a student in the Applied Informatics - Computer Science program, this project serves as a practical exploration of theoretical concepts learned throughout my academic journey. The thesis focuses on cache memory, a critical component in computer architecture, and aims to provide a hands-on understanding of how different cache architectures function and their implications on overall system performance.

- Graphical User Interface: Explore cache simulations through an intuitive GUI.

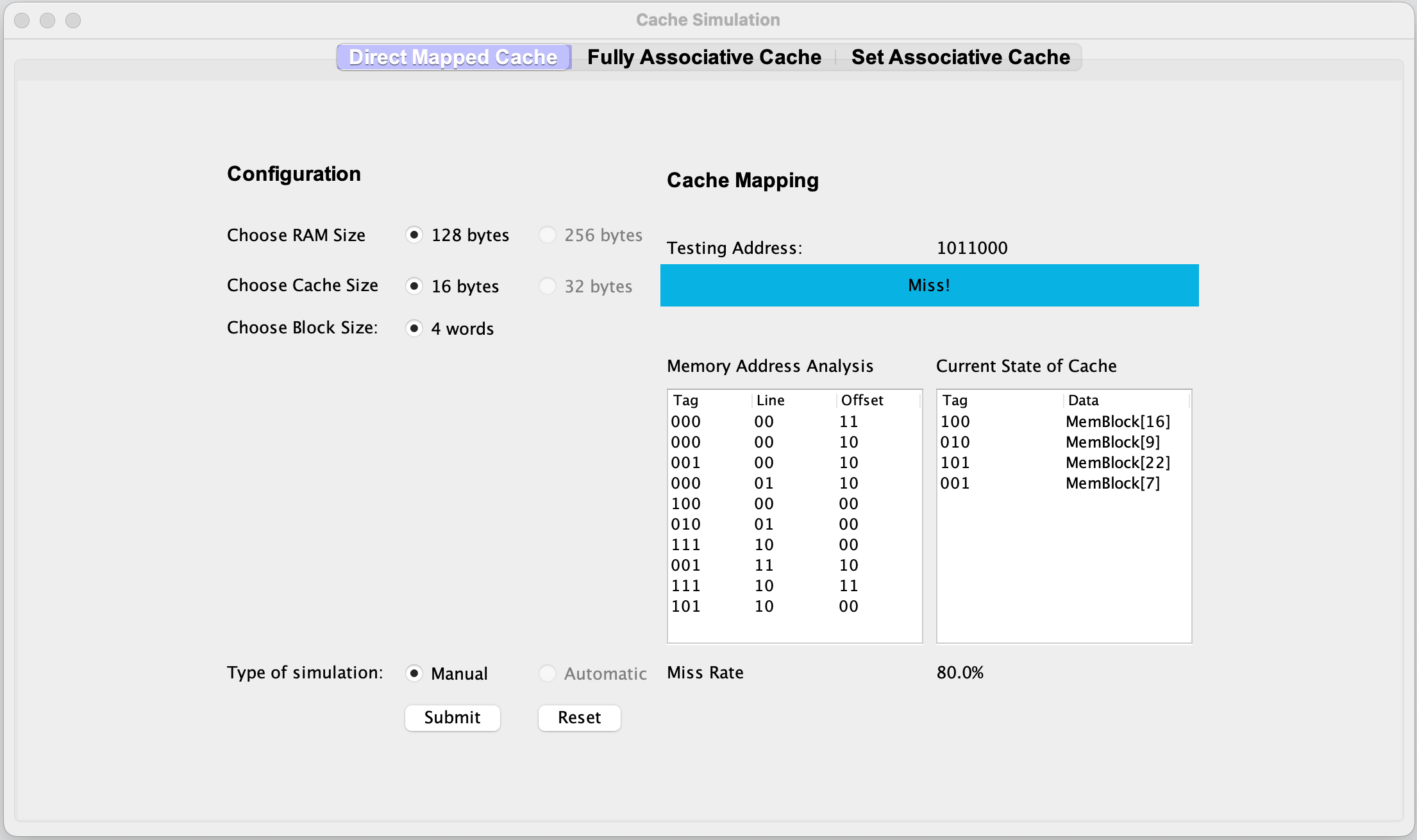

- Direct-Mapped Cache: Simulates a direct-mapped cache and its impact on memory access times.

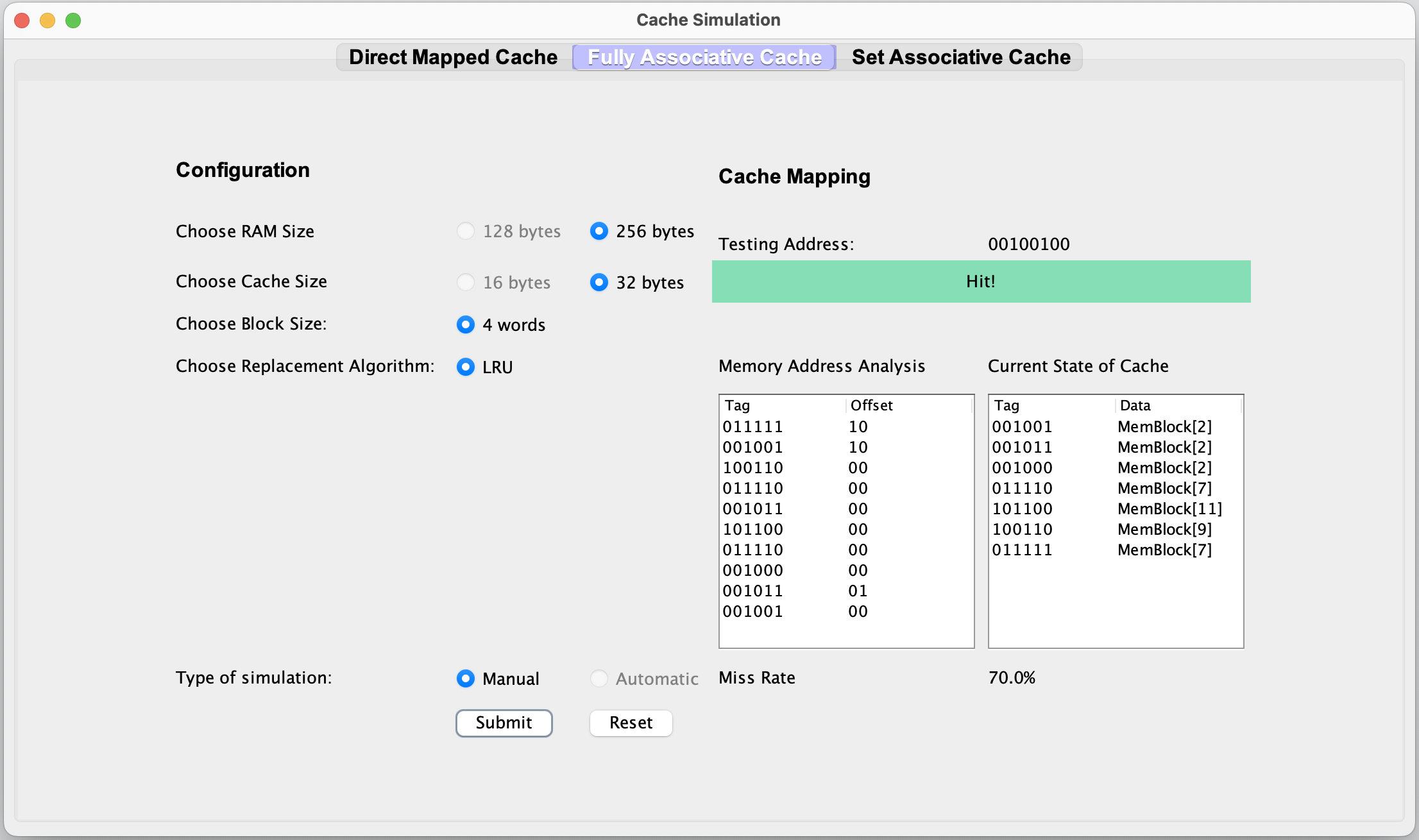

- Fully Associative Cache with LRU: Demonstrates a fully associative cache with the Least Recently Used replacement policy.

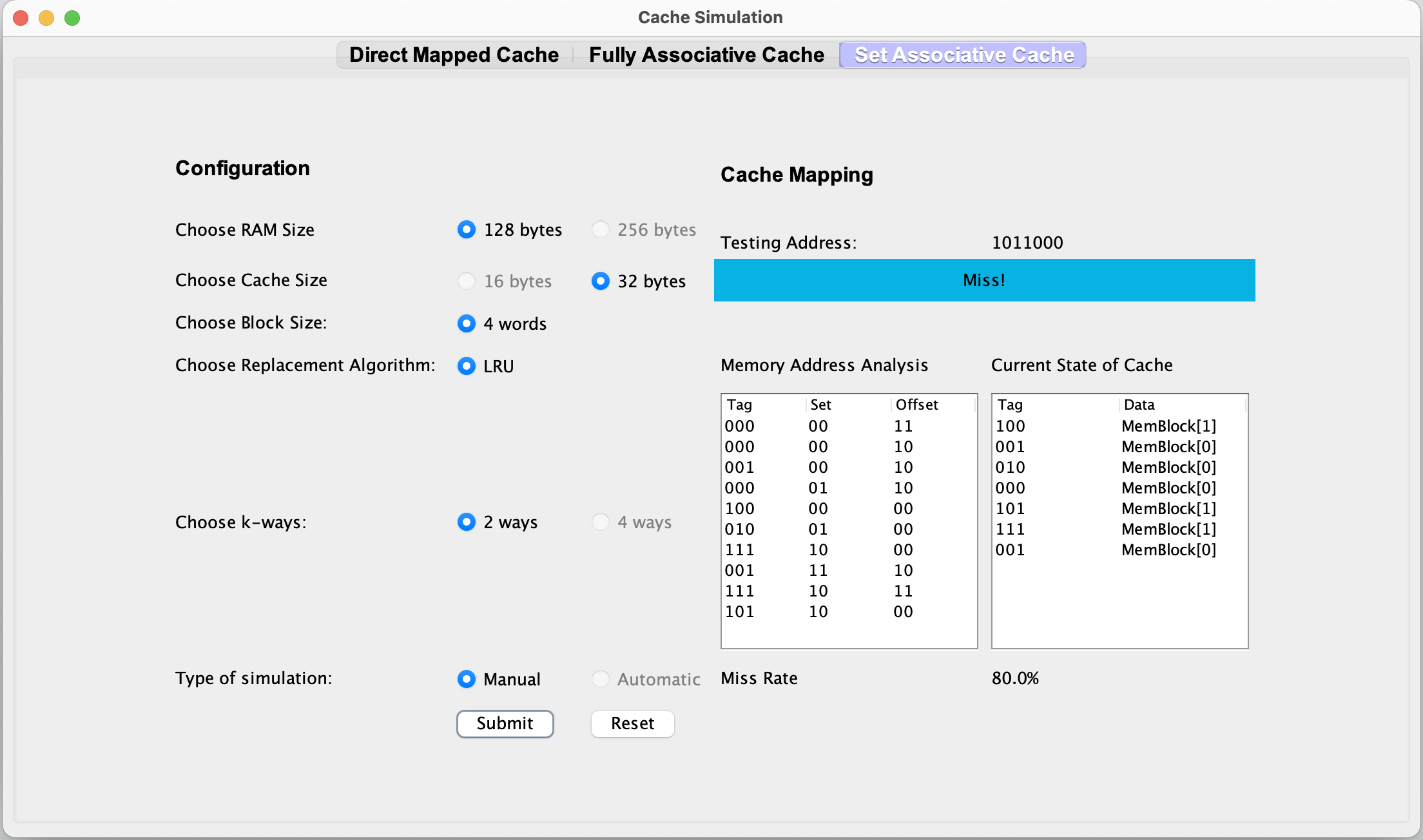

- Set Associative Cache with LRU: Simulates a set-associative cache with LRU replacement policy

- Direct Mapped Cache

- Fully Associative Cache

- Set Associative Cache

- Adjust simulation parameters, such as RAM size, cache size, block size, kWays, and associativity, in the GUI tab of each cache type.

Download and run Cache Simulation - ics20032.jar

This project is licensed under the MIT License.