This VS Code extension provides features to read, navigate and write SystemVerilog code much faster.

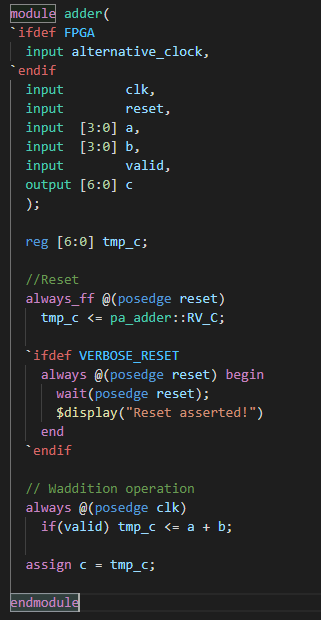

- Elaborate syntax highlighting

- Go to symbol in document (

Ctrl+Shift+O) - Go to symbol in workspace folder (indexed modules/interfaces/programs/classes/packages) (

Ctrl+T) - Go to definition (works for module/interface/program/class/package names and for ports too!) (

Ctrl+LeftClick) - Quick-start on already indexed workspaces

- Code snippets for many common blocks

- Instantiate module from already indexed module

- Linter capabilites with simulators (more info on the wiki)

- Fast real-time error identification through an integrated SystemVerilog parser and IntelliSense (fully accurate to IEEE Standard 1800-2017)

- If you find a bug or would like a feature, request it as an Issue or submit a Pull Request

- If you have netlists in your workspace you can exclude them in the settings, e.g.:

**/syn/** - Disclaimer: This is not a functional tool that will compile and simulate HDL, but it will make it easier and more user-friendly to write and navigate SystemVerilog and Verilog.

systemverilog.includeIndexing: Array, Globs defining files to be indexedsystemverilog.disableIndexing: Boolean, Disable indexingsystemverilog.excludeIndexing: String, Exclude files from indexing based on globsystemverilog.parallelProcessing: Integer, Number of files to process in parallel during indexingsystemverilog.antlrVerification: Boolean, Use ANTLR parser to verify code in real-timesystemverilog.launchConfiguration: String, Command to run when launching verilator- Default: verilator --sv --lint-only --language 1800-2012 --Wall

- If not in path, replace verilator with the appropriate command

systemverilog.compileOnSave: Boolean, Compile files when saved- Default: true

systemverilog.compilerType: String, Dropdown list to select a compiler type- Default: Verilator

systemverilog.trace.server: String, Dropdown to select verbosity of LSP message tracing

- Initial indexation might hog CPU/RAM when looking through files in very large workspaces

- Tree view of module hierarchy

- References document

- IntelliSense support (CompletionProvider)

- Back-end Language server for Systemverilog

- Update workspace state to save to storagePath

- If you want to contribute with the project please fork this repository, clone it, make changes (preferably in a branch other than master) and finally create a Pull Request (more details here).

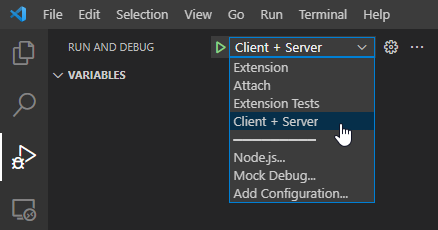

- To debug the extension locally first install the required dependencies (in the repository's root directory):

npm install

- Then compile the project at least once (this will generate the SystemVerilog lexer and parser in

src\compiling\ANTLR\grammar\build):

npm run compile

See the changelog for more details

- Syntax Highlighting Overhaul, thanks to

jecassis - Smaller extension footprint, thanks to

jecassis - Support for external formatter, thanks to

jecassis - Documentation upgrade, thanks to

jecassis - Dev update with ESLint, Prettier and tests update, thanks to

jecassis

- Folders outside the workspace can now be included with

systemverilog.includeIndexing - It now saves the indexed database between runs, allowing quickstart on previous workspaces

- Increased the number of symbols the parser understands.

- Extensive bug squashing

- Compile an opened document using

Verilatorsimulator, display errors/warnings asDiagnosticsin documents, thanks tooehaddouchi - Compile documents on save feature using

Verilatorsimulator - Added output channel

SystemVerilog - Added an

LSP, set it to communicate with the extension's client - Keep track of the recently used modules in the indexer

- Added diagnostic support for

VCScompiler

- Instantiate module from already indexed module, thanks to

oehaddouchi - Update to documentSymbolProvider

- Stability and performance upgrade

- PCRE Regexes

- HoverProvider added, thanks to

toastedcornflakes - Improvements to DocumentSymbolProvider to better support Hover

- Added setting to exclude folders from indexing

- DefinitionProvider fetching from indexed modules implemented

- Indexing is now more safe, and will work for large workspaces

- Alpha 2 release with expanded syntax highlighting and snippets

- Indexing of every module/interface/program/class in workspace

- Alpha 1 release with syntax highlighting, and go to symbols