本リポジトリには、M5Stack社が製造・販売している ATOM Display, ATOM Display Lite, Display Module 13.2 (以下 ATOM Display と記載)に搭載されているFPGA上の論理回路のソースおよび合成手順が含まれている。

ATOM Displayに搭載されているFPGAはGOWIN社の GW1NR-LV9QN88 であり、GOWIN社から提供される GOWIN EDA ツールを用いて論理合成、配置配線、ビットストリームの生成を行うことにより、付属のテストコードと結合して、生成したビットストリームを動かすことができる。

(注:GOWIN EDA Education版非対応のデバイスなので、GOWIN EDA Standard版が必要)

----------------------------------------------------------

Resources | Usage

----------------------------------------------------------

Logic | 4971/8640 57%

--LUT,ALU,ROM16 | 4785(3896 LUT, 889 ALU, 0 ROM16)

--SSRAM(RAM16) | 31

Register | 4081/6807 59%

--Logic Register as Latch | 0/6480 0%

--Logic Register as FF | 4078/6480 62%

--I/O Register as Latch | 0/327 0%

--I/O Register as FF | 3/327 1%

CLS | 3824/4320 88%

I/O Port | 39

I/O Buf | 38

--Input Buf | 5

--Output Buf | 33

--Inout Buf | 0

IOLOGIC | 47%

--IDDR | 16

--ODDR | 36

BSRAM | 53%

--SDPB | 7

--SDPX9B | 7

DSP | 5%

--MULT18X18 | 1

PLL | 1/2 50%

DCS | 0/8 0%

DQCE | 0/24 0%

OSC | 0/1 0%

User Flash | 0/1 0%

CLKDIV | 0/8 0%

DLLDLY | 0/8 0%

DHCEN | 0/8 0%

DHCENC | 0/4 0%

==========================================================

現在のところLinux環境上でのみ、リポジトリ内のビルドスクリプトの動作を確認している。 また、以下のツールが使える状態になっている必要がある。

- Chisel 3.4.3が動作する環境

- GOWIN EDA v1.9.8.08

- PlatformIO

このリポジトリをクローンする際に --recursive を指定していない場合、以下のコマンドでサブモジュールを取得する。

git submodule update --init --recursive

デザインを合成するには、まずはChiselのデザインからVerilog HDLを生成する必要がある。

以下のコマンドを実行すると、Scalaのビルドツールである sbt を起動して、ATOM Display用のデザインのエラボレーションを行い、

結果として rtl/m5stach_hdmi/video_generator.v を出力する。

- コマンド

sbt "project atom_display; runMain system.ElaborateM5StackHDMI"- 実行結果

[info] welcome to sbt 1.5.4 (Ubuntu Java 11.0.13)

[info] loading global plugins from /home/kenta/.sbt/1.0/plugins

[info] loading settings for project atom_display_fpga-build-build from metals.sbt ...

[info] loading project definition from /home/kenta/repos/atom_display_fpga/project/project

[info] loading settings for project atom_display_fpga-build from metals.sbt ...

[info] loading project definition from /home/kenta/repos/atom_display_fpga/project

[success] Generated .bloop/atom_display_fpga-build.json

[success] Total time: 0 s, completed Jan 13, 2022, 4:00:10 AM

[info] loading settings for project root from build.sbt ...

[info] loading settings for project fpga_samples from build.sbt ...

[info] set current project to root (in build file:/home/kenta/repos/atom_display_fpga/)

[info] set current project to atom_display (in build file:/home/kenta/repos/atom_display_fpga/)

[info] running system.ElaborateM5StackHDMI

Elaborating design...

Done elaborating.

[success] Total time: 5 s, completed Jan 13, 2022, 4:00:15 AM

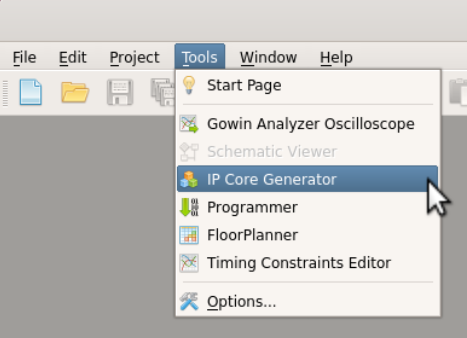

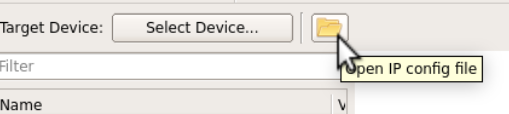

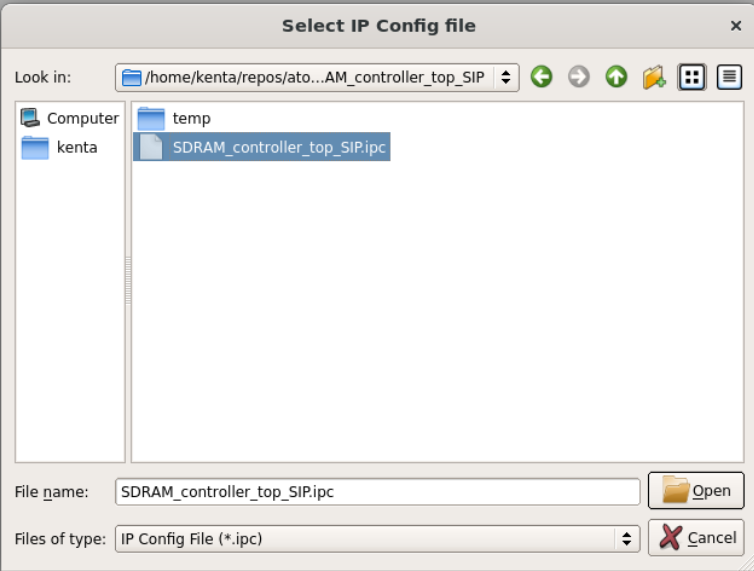

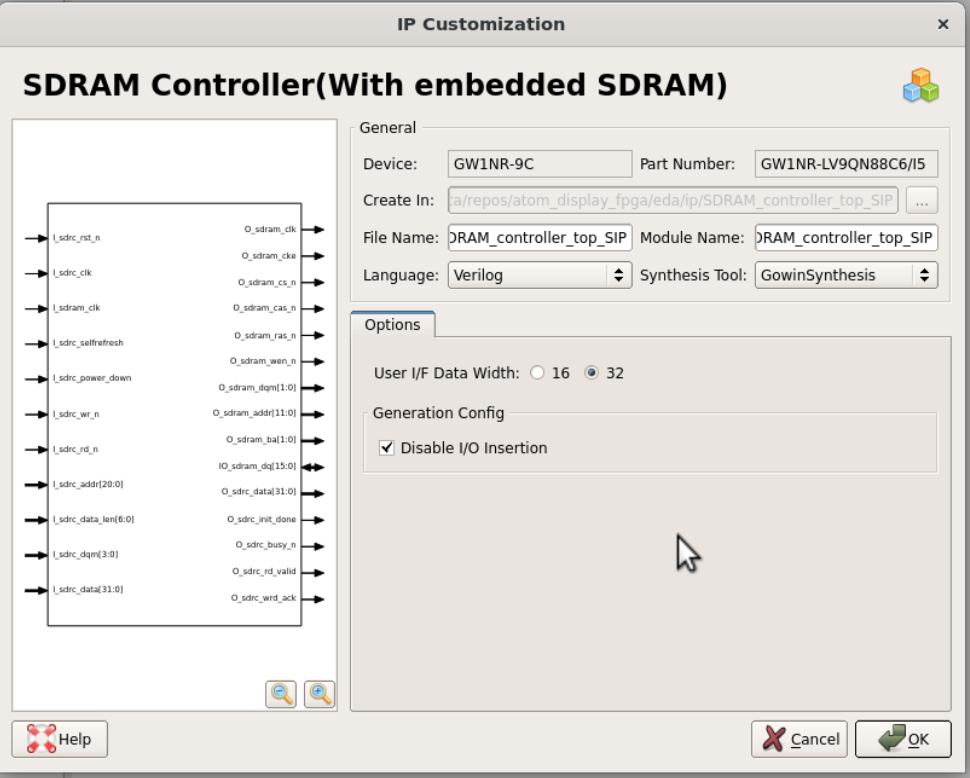

eda/ip ディレクトリにあるGOWIN IPの定義ファイルから、GOWIN IPの合成用ファイルを再生成する。

GOWIN EDAのGUIを起動し、IP Generatorから eda/ip/SDRAM_controller_top_SIP/SDRAM_controller_top_SIP.ipc および eda/ip/sdram_rpll/sdram_rpll.ipc を開き、立ち上がったウィザードでそのままOKを押す。

eda/atomdisplay に移動して make を実行すると、GOWIN EDAを使って論理合成を行い、ビットストリームを生成する。

また、M5GFXにてビットストリームを取り扱うために生成されたビットストリームをRLEにて圧縮する。

- コマンド

cd eda/atomdisplay

make- 実行結果

gw_sh ./project.tcl atomdisplay

*** GOWIN Tcl Command Line Console ***

current device: GW1NR-9C GW1NR-LV9QN88C6/I5

add new file: "/home/kenta/repos/atom_display_fpga/atom_display/rtl/m5stack_hdmi/video_generator.v"

add new file: "/home/kenta/repos/atom_display_fpga/eda/ip/SDRAM_controller_top_SIP/SDRAM_controller_top_SIP.v"

add new file: "/home/kenta/repos/atom_display_fpga/eda/ip/sdram_rpll/sdram_rpll.v"

add new file: "/home/kenta/repos/atom_display_fpga/eda/src/top.sv"

add new file: "/home/kenta/repos/atom_display_fpga/eda/src/atomdisplay.cst"

add new file: "/home/kenta/repos/atom_display_fpga/eda/src/m5stack_display.sdc"

GowinSynthesis start

Running parser ...

...

[100%] Power analysis completed

Generate file "/home/kenta/repos/atom_display_fpga/eda/atomdisplay/impl/pnr/atomdisplay.power.html" completed

Generate file "/home/kenta/repos/atom_display_fpga/eda/atomdisplay/impl/pnr/atomdisplay.pin.html" completed

Generate file "/home/kenta/repos/atom_display_fpga/eda/atomdisplay/impl/pnr/atomdisplay.rpt.html" completed

Generate file "/home/kenta/repos/atom_display_fpga/eda/atomdisplay/impl/pnr/atomdisplay.rpt.txt" completed

Generate file "/home/kenta/repos/atom_display_fpga/eda/atomdisplay/impl/pnr/atomdisplay.tr.html" completed

Thu Jan 13 04:14:21 2022

python3 ../../script/fs2rle.py impl/pnr/atomdisplay.fs impl/pnr/atomdisplay.rle

以下の手順でテストコードのビルドとATOM Displayへの書き込みを行う。

- ATOM DisplayをPCとディスプレイに接続する。

- ATOM DisplayのUSBシリアル変換器のデバイス名を調べておく。 (例:

/dev/ttyACM0) platformio.iniをエディタで開き、upload_portとmonitor_portを (2)で調べたデバイス名に変更する。testディレクトリでmakeを実行する

ソースコードのうち、 src ディレクトリ以下のChiselのコード、 eda ディレクトリ以下のSystemVerilogで記述したトップモジュールは GPLv3 の元で使用できる。

GOWIN EDA のIP Generatorで生成したIPのライセンスは、それぞれのIPのライセンスに従う。