| 1. Introduction | 2. Developing for FPGAs | 3. Working with Merlin | 4. Platform-Specific | ||

Some cogntive-era applications such as Genomics, Machine Learning inferencing and Big data analytics can be compute-heavy. Accelerating such applications can be achieved by offloading parts of the applications from a typical CPU to other types of hardware, such as FPGAs. For specific categories of applications, FPGAs can deliver much faster results than a typical CPU. This is due to the highly parallel nature inhereted to FPGAs by architecture.

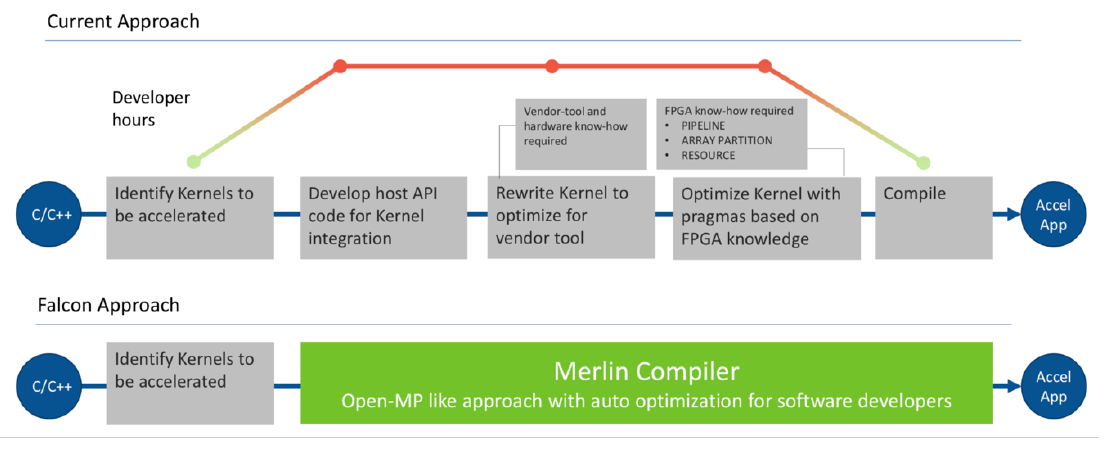

Traditionally, designing for FPGA is done using hardware descriptive languages such as Verilog or VHDL. Learning and using such languages can be quite involved, especially for a software developer. The Merlin Compiler from Falcon Computing solves these challenges. It enables software developers to be able to compile their applications for FPGA acceleration without FPGA expertise. Merlin Compiler takes C/C++ code as an input and generates an executable that includes the CPU host-code & the FPGA bitstream .

Why Merlin?

By abstracting all the hardware design details away from the software developers, Merlin provides an easier alternative to leverage FPGAs hosted in public clouds (such as Amazon AWS F1 ) or within an on-premises environment. It is able to automatically generate performance comparable to FPGA Ninjas with Hardware expertise working for several weeks or months using High Level Synthesis such as SDAccel or Intel OpenCl

This is a tutorial on how to use Merlin Compiler on Amazon AWS as well as on-premises. In this tutorial, you will see a few design examples. The below table gives a brids’eye view of the benefits on Merlin in terms of # of pragmas & comparable performance:

| Design Example | HLS Source | Merlin Source | HLS # of pragmas | Merlin # of pragmas |

|---|---|---|---|---|

| Vector Add | vadd.cpp | vec_add_kernel.cpp | 8 | 2 |

| BlackScholes |

blackAsian.cpp blackScholes.cpp |

blackAsian.cpp blackScholes.cpp |

33 | 5 |

| AES | N/A | aes.cpp | N/A | 6 |

Start the next module: 2. Developing for FPGAs