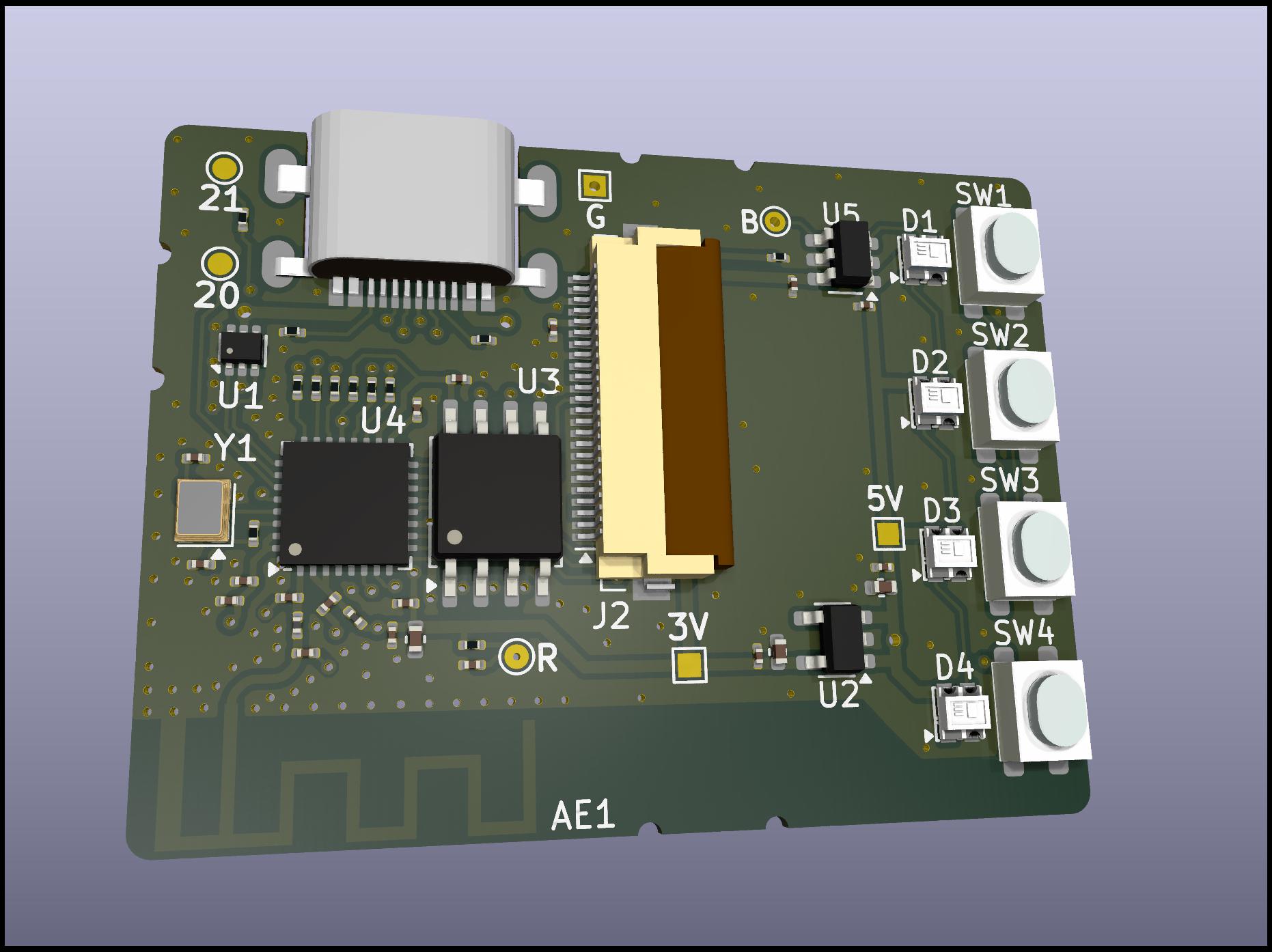

The hardware design, schematics and PCB layouts for the Firefly Pixie Hardware Wallet for Ethereum (and ilk).

See the CHANGELOG for high-level changes between board revisions.

- Processor: ESP32-C3 (32-bit RISC-V)

- Speed: 160Mhz

- Memory: 400kb RAM, 16Mb Flash, 4kb eFuse

- Inputs: 4x tactile buttons

- Outputs:

- 240x240px IPS 1.3" display (16-bit color; RGB565)

- 4x RGB LED (WS2812B; 24-bit color; GRB888)

- Conectivity:

- USB-C (power + JTAG/CDC-ACM)

- BLE

- To modify the files, use KiCad (open-source EDA application)

- Sicne the

git diffinvolved in modifying these files is somewhat opaque, please start a discussion first, so any changes can be coordinated

See the output folder for rendered schematics, PCBs and 3D renders along with photos of the various revisions.

MIT License.