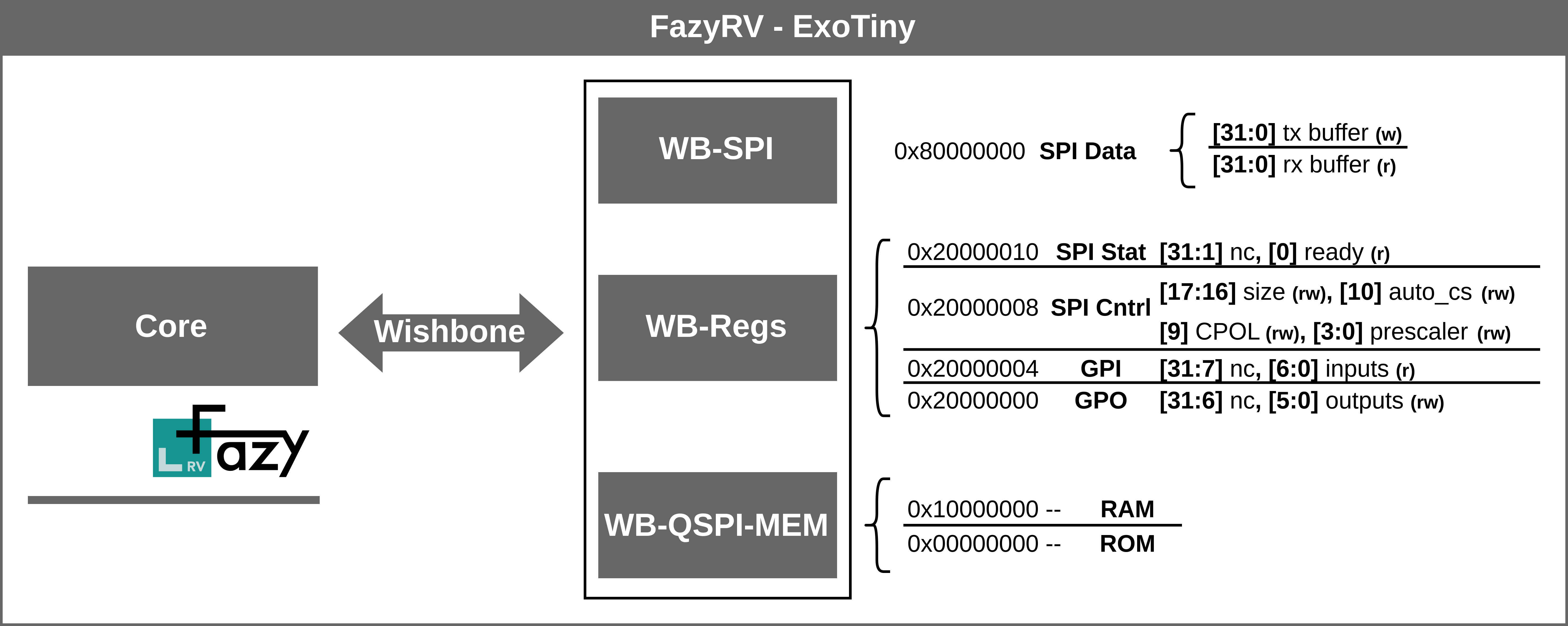

FazyRV-ExoTiny implements a minimal System-on-Chip based on the FazyRV RISC-V core. It targets platforms that do not have on-chip memory available through external QSPI RAM and ROM memory. This repository is tailored to a particular use case. We recommend taking a look at the documentation given in FazyRV.

Important

FazyRV-ExoTiny is designed to showcase FazyRV in specific scenarios when on-chip memory is not available. We highly recommend re-verifying the design when adopting it.

Warning

WIP! Full verification is yet to be done.

Init the submodules recursively.

git submodule update --init --recursiveYou may want to use a Python virtual environment.

python3 -m venv .venv

source .venv/bin/activate

pip install -r requirements.txtStart by adding core files to the fusesoc library.

fusesoc library add exotiny .To run the riscv-tests with default options, run the following make target. The FazyRV variant may be overwritten by setting environment variables.

# riscv-tests

cd sim

make test

# or

make test_vcdThe RISCOF framework provides more extensive simulation-based design tests.

# RISCOF

make riscof.prepare

make riscof.run.<CHUNKSIZE>-<CONF>-<RFTYPE>

# e.g.,

make riscof.prepare

make riscof.run.2-MIN-BRAM