Example design for the Opsero Ethernet FMC and Robust Ethernet FMC using an FPGA based hardware packet generator/checker to demonstrate maximum throughput.

This project is designed for version 2024.1 of the Xilinx tools (Vivado/SDK/PetaLinux). If you are using an older version of the Xilinx tools, then refer to the release tags to find the version of this repository that matches your version of the tools.

In order to test the Ethernet FMC using this design, you need to use an Ethernet cable to loopback ports 0 and 2, and ports 1 and 3. You will also need the following:

- Vivado 2024.1

- Vitis 2024.1

- Vivado HLS 2024.1

- Ethernet FMC or Robust Ethernet FMC

- Supported FMC carrier board (see list of supported carriers below)

- Two Ethernet cables

- Xilinx Soft TEMAC license

- Zynq-7000 ZedBoard

- LPC connector

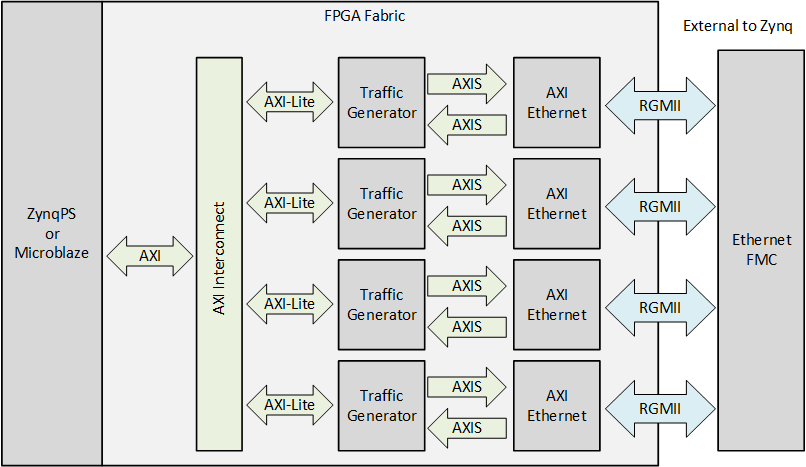

This project is used for testing the Ethernet FMC or Robust Ethernet FMC at maximum throughput. The design contains 4 AXI Ethernet blocks and 4 hardware traffic generators. The transmitted frames contain fixed destination and source MAC addresses, the Ethertype, a payload of random data and the FCS checksum.

- Download the repo as a zip file and extract the files to a directory on your hard drive --OR-- clone the repo to your hard drive

- Open Windows Explorer, browse to the repo files on your hard drive.

- In the

Vivadodirectory, double click on thebuild-vivado.batbatch file. You will be prompted to select a target design to build. You will find the project in the folderVivado/<target>. - Run Vivado and open the project that was just created.

- Click Generate bitstream.

- When the bitstream is successfully generated, select File->Export->Export Hardware. In the window that opens, tick Include bitstream and use the default name and location for the XSA file.

Before running these steps, you must first build and export the Vivado project as described above.

- Return to Windows Explorer and browse to the Vitis directory in the repo.

- Double click the

build-vitis.batbatch file. You will be prompted to select a target design. A Vitis workspace with hardware platform and software application will be created for the selected target design. You will find the Vitis workspace in the folderVitis/<target>_workspace.

- Open a command terminal and launch the setup script for Vivado:

source <path-to-vivado-install>/2024.1/settings64.sh - Clone the Git repository and

cdinto theVivadofolder of the repo:git clone https://github.com/fpgadeveloper/ethernet-fmc-max-throughput.git cd ethernet-fmc-max-throughput/Vivado - Run make to create the Vivado project for the target board. You must replace

<target>with a valid target (alternatively, skip to step 5):Valid targets are:make project TARGET=<target>zedboard. That will create the Vivado project and block design without generating a bitstream or exporting to XSA. - Open the generated project in the Vivado GUI and click Generate Bitstream. Once the build is complete, select File->Export->Export Hardware and be sure to tick Include bitstream and use the default name and location for the XSA file.

- Alternatively, you can create the Vivado project, generate the bitstream and export to XSA (steps 3 and 4),

all from a single command:

make xsa TARGET=<target>

The following steps are required if you wish to build and run the standalone application. You are not required to have built the Vivado design before following these steps, as the Makefile triggers the Vivado build for the corresponding design if it has not already been done.

- Launch the setup script for Vivado (only if you skipped the Vivado build steps above):

source <path-to-vivado-install>/2024.1/settings64.sh - Launch the setup scripts for Vitis:

source <path-to-vitis-install>/2024.1/settings64.sh - To build the Vitis workspace,

cdto the Vitis directory in the repo, then run make to create the Vitis workspace and compile the standalone application:You will find the Vitis workspace in the foldercd ethernet-fmc-max-throughput/Vitis make workspace TARGET=<target>Vitis/<target>_workspace.

In order to test an Ethernet device at maximum throughput (back-to-back packets at 1Gbps), one could setup the MACs to loopback to each other and then send packets to each port from an external source such as a PC which could compare the returned packets to the sent ones. However, it is generally difficult to use a PC Ethernet port at full throughput, because a PC typically has too many overheads which create a delay between consecutive packets. For this reason, this design uses four hardware packet generator/checkers that are implemented in the FPGA. These generator/checkers drive the AXI Ethernet cores (the MACs) with a continuous stream of packets. By using the FPGA to generate the Ethernet packets, we are able to exploit almost 100% of the potential bandwidth.

The software application sets up the MACs in promiscuous mode which allows them to pass through all packets, regardless of their destination MAC address. It also sets them up to receive the FCS (checksum) from the user design, rather than calculating and inserting it itself.

Due to the FCS (checksum) which is present in every Ethernet packet, most bit errors that are injected into the system will result in dropped packets at the receiving MAC (ie. the receiving MAC will reject packets where the FCS does not match the frame data). Therefore, our primary method for detection of bit errors involves polling the MACs for rejected frames. The number of rejected frames is tracked by the software application.

To ensure that the MACs are truly rejecting frames with bit errors, we inject one bit error into one packet per second, on all 4 ports. Our design supplies the FCS to the transmit interface of the MACs, rather than having the MACs calculate and append the FCS. This allows us to inject a bit error that should render the FCS incorrect for the frame.

The traffic generator IP was designed in Vivado HLS (High-level Synthesis) and is coded in C++. Vivado HLS allows hardware algorithms to be programmed in the C/C++ language which offers tremendous advantages over VHDL and Verilog, especially when developing packet processing systems. This example design serves as a good platform for developing Ethernet packet processing algorithms with the Ethernet FMC.

The Ethernet Traffic Generator IP can be simulated in Vivado by using the RTL testbench that

is included with the project. The Vivado project contains two block designs, maxtp and maxtp_sim,

used for implementation and simulation respectively. The maxtp_sim block design contains one

instantiation of the Ethernet Traffic Generator IP (the DUT) and one AXI VPI IP core that we use to initialize the

software registers of the DUT. To run the simulation, simply open the Vivado project and select

Run Simulation->Run Behavioral Simulation.

This design is actually used as a production test for the Ethernet FMC and Robust Ethernet FMC because it places maximum stress on the PHYs, which forces the maximum current consumption, heat dissipation and possibility for cross-talk between lanes. It can however be a very useful design for people who need to communicate over Ethernet with another FPGA or an Ethernet device that can support the high throughput.

Check the following if the project fails to build or generate a bitstream:

Check the version specified in the Requirements section of this readme file. Note that this project is regularly maintained to the latest version of Vivado and you may have to refer to an earlier commit of this repo if you are using an older version of Vivado.

All the projects in the repo are built, synthesised and implemented to a bitstream before being committed, so if you follow the instructions, there should not be any build issues.

Vivado doesn't cope well with long directory structures, so copy/clone the repo into a short directory structure such as

C:\projects\. When working in long directory structures, you can get errors relating to missing files, particularly files

that are normally generated by Vivado (FIFOs, etc).

We encourage contribution to these projects. If you spot issues or you want to add designs for other platforms, please make a pull request.

This project was developed by Opsero Inc., a tight-knit team of FPGA experts delivering FPGA products and design services to start-ups and tech companies. Follow our blog, FPGA Developer, for news, tutorials and updates on the awesome projects we work on.