- 1 FP1-based FPGA Development Suite

- 2 FPGA Development Guide for High-Performance Architecture

- 3 FPGA Development Guide for General-Purpose Architecture

The FP1-based FPGA development suite is a cloud FPGA hardware/software development kit based on Huawei enterprise cloud services. This suite helps users to design, simulate, implement, and one-click compilation run on FPGA, and provides professional design and verification components to help users efficiently implement FPGA development. The suite provides tools for hardware and software development, respectively. The hardware development suite helps users to complete project compilation, simulation, generate the .dcp or .xclbin file, and register an FPGA image. The software development suite guides users to load an FPGA image, and compile and debug user applications.

Before using the FPGA development suite, you must perform 1.2.1~1.2.2 steps to complete the development kit acquisition and tool installation and configuration. The hardware development tools are stored in the hardware directory, including Vivado and SDAccel development tools. The software development tools are stored in the software directory, including configure files, drivers, tools, and related applications which are needed when running instances.

-

For HTTPS connections, run the

git clone https://github.com/huaweicloud/huaweicloud-fpga.gitcommand to download the suite. -

For SSH connections, run the

git clone git@github.com:huaweicloud/huaweicloud-fpga.gitcommand to download the suite.

Ensure that the ECS is bound with an EIP before using the ECS to download the development suite.

Ensure that the Git tool is installed before downloading the development suite.

The fisclient is a cross-platform command-line interface (CLI) tool used for FPGA image management, which is mandatory before FPGA image loading. By using fisclient, you can register, delete, and query FPGA images (AEIs), or manage the association between AEIs and elastic cloud server (ECS) images. You can associate an AEI with an ESC image, and release the AEI to the cloud market or share it with other users through the ESC image.

For details, please see the chapter of installation and configuration in fisclient README.

When a high-performance architecture is used, the FPGA development is divided to three scenarios: hardware development, software development, and example using. During hardware development, you can generate and register an FPGA image by using the Vivado tools. During software development, you can develop applications based on the existing FPGA image. By using examples, you can quickly master the FPGA development process under the current server architecture.

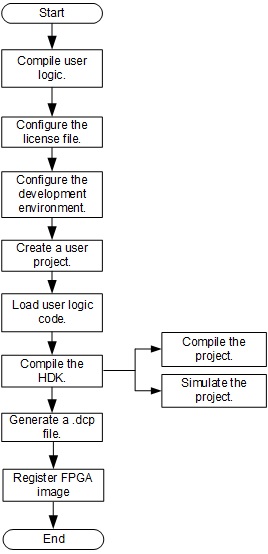

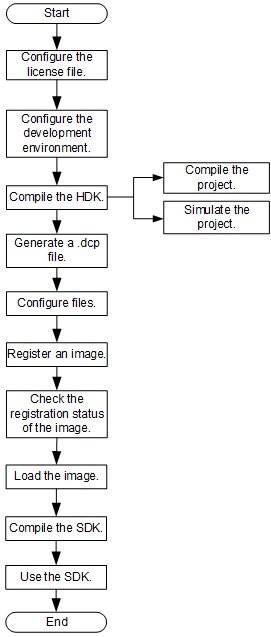

When a high-performance architecture FACS is used, the FPGA hardware development is based on the Vivado tools. This development process guides users to create, compile, and simulate a project, generate a .dcp file, and register an FPGA image (AEI, Accelerated Engine Image). After the hardware development, if you need to develop your own applications based on the registered FPGA image, see section 2.2.

For details about how to develop a .dcp file based on the Vivado, see Vivado-Based Hardware Development Process.

Before registering an FPGA image, if you have not installed this tool yet, please install the image management tool fisclient by referring to section 1.2.2.

You can use AEI_Register.sh to register an FPGA image with the image management module. After the registration, an ID is assigned to the FPGA image. Please record this ID, because it can be used to query the registration status, and load, delete, and associate the image.

Users can run the fis fpga-image-list command to query information about an FPGA image. If the image status is active, users can load the image using the image ID.

For details about how to use the fisclient to query the FPGA image, see fisclient README.

After hardware development and FPGA image registration, you can develop FPGA user applications by referring to this section.

After an FPGA image is registered, use the FPGA image loading tool FpgaCmdEntry to load the image to the FPGA before software development.

The FPGA image loading tool FpgaCmdEntry is a command-line interface (CLI) tool, which supports FPGA information query, image loading and query, and virtual LED status query.

For details, please see the chapter of compiling and installing in fpga_tool README.

For details, see the following file.

For more details of loading tool, see fpga_tool README.

The high-performance architecture development mode uses the DPDK architecture to exchange data between the FPGA and the processors. For details about how to compile and debug user applications, see DPDK-Based User Applications Development Description. If you need to modify the driver, refer to DPDK-Based Driver Development Description.

After the FPGA image loading and application compilation, you can go to the huaweicloud-fpga/fp1/software/app/dpdk_app/bin directory to run user applications.

For high-performance server architectures, FAC services provide three examples. Example 1 implements user logic version reading, data inversion, and addition functions. Example 2 implements user logic DMA (Direct Memory Access) loopback channels and DDR (DDR SDRAM) read functions. Example 3 implements user logic FPGA memory manage unit (FMMU) function. The following figure shows the Vivado-based example operation process.

For details, see Using a Vivado-based Example.

When a general-purpose architecture is used, the FPGA development is divided to three scenarios: hardware development, software development, and example using. During hardware development, you can generate and register an FPGA image by using the SDAccel tools. During software development, you can develop applications based on the existing FPGA image. By using examples, you can quickly master the FPGA development process under the current server architecture.

- 3.1 Hardware Development Process

- 3.2 Software Development Process

- 3.3 Using an SDAccel-Based Example

If the kernel compilation has been implemented offline , and the corresponding xclbin file generation is done, please refer to the link as SDAccel-based offline development online usage process description.

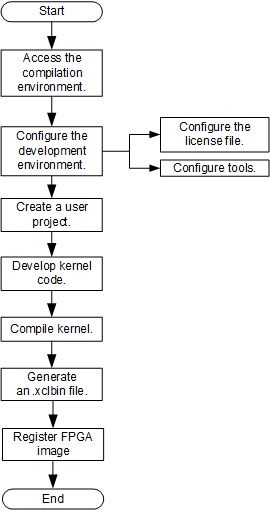

When a general-purpose architecture is used, the hardware development is based on the SDAccel tools. This development process guides users to create, compile, and simulate a project, generate an .xclbin file, and register an FPGA image (AEI). After the hardware development, if you need to develop your own applications based on the registered FPGA image, see section 3.2.

For details about how to develop an .xclbin file based on the SDAccel, see SDAccel-Based Hardware Development Process.

Before registering an FPGA image, if you have not installed this tool yet, please install the image management tool fisclient by referring to section 1.2.2. After the installation, you can use AEI_Register.sh to register an FPGA image with the image management module. For details about how to register an FPGA image, see Registering an FPGA Image. After the registration, an ID is assigned to the FPGA image. Please record this ID, because it can be used to query the registration status, and load, delete, and associate the image.

You can run the Fisclient command to query the registration result. For details, see step 2 in section 2.1.2.

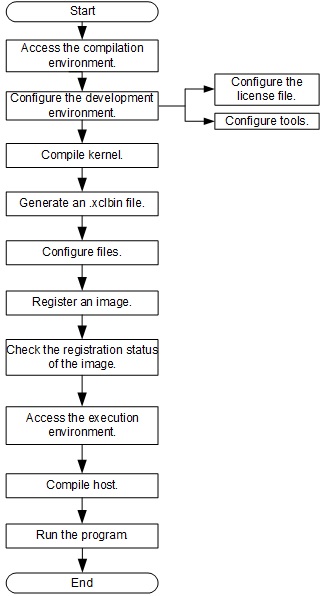

After hardware development and FPGA image registration, you can develop FPGA user applications by referring to this section.

The general-purpose architecture development mode uses the Xilinx SDAccel architecture to exchange data between the FPGA and the processors. For details about how to compile and debug user applications, see SDAccel-Based User Applications Development Description. If you need to modify the HAL, see the SDAccel Mode HAL Development Description.

After the FPGA image loading and application compilation, you can go to the huaweicloud-fpga/fp1/software/app/sdaccel_app directory to run user applications.

When a general-purpose architecture is used, the Huawei FAC services provide three examples. Example 1 is an example of matrix multiplication using C to implement the logic algorithm. Example 2 is an example of vector addition using OpenCL C to implement the logic algorithm.Example 3 is an example of vector addition using RTL to implement the logic function. The following figure shows the SDAccel-based example operation process.

For details, see Using an SDAccel-Based Example.

----End