O projeto consiste em uma CPU arquitetada em verilog para a execução de 33 instruções do assembly Mips, conseguindo lidar com erros de Overflow, divisão por 0 e de instrução inválida.

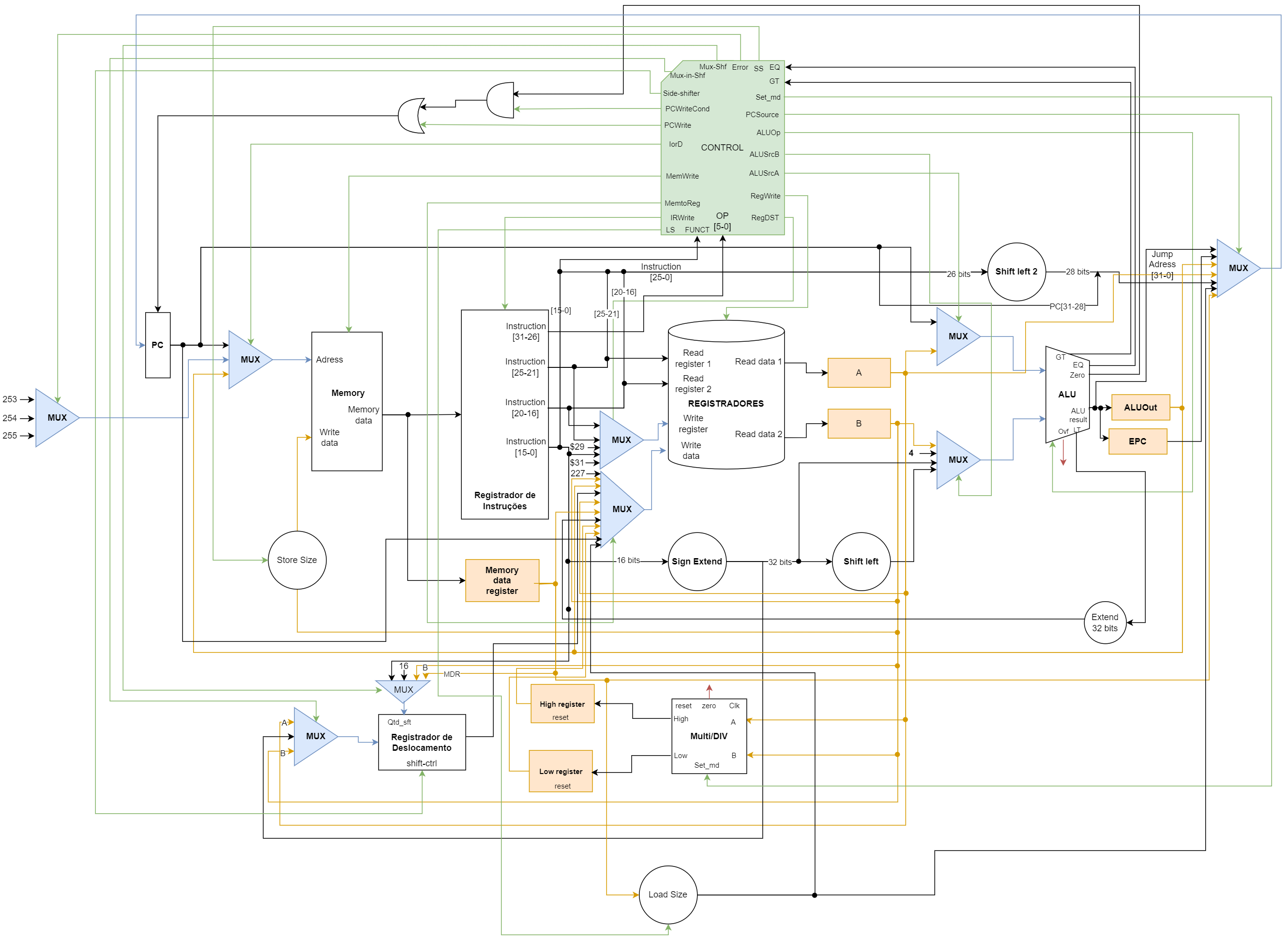

A CPU foi implementada com base no diagrama de blocos a seguir:

Foi elaborado também uma máquina de estados (FSM) para mapear os ciclos de execução de cada instrução.

O repositório contém também o relatório com a simulação e descrição de cada uma das 33 instruções implementadas, além da explicação de cada um dos estados.

Para poder testar, é necessário algum simulador, como o ModelSim e inserir a versão binária das instruções no arquivo /modules/instrucoes.mif, que pode ser obtido por meio da conversão para binário dos valores em hexadecimal nas imagens abaixo, ou forçar valores manualmente.

Abaixo segue a listas de instruções e seus valores para os parsers.