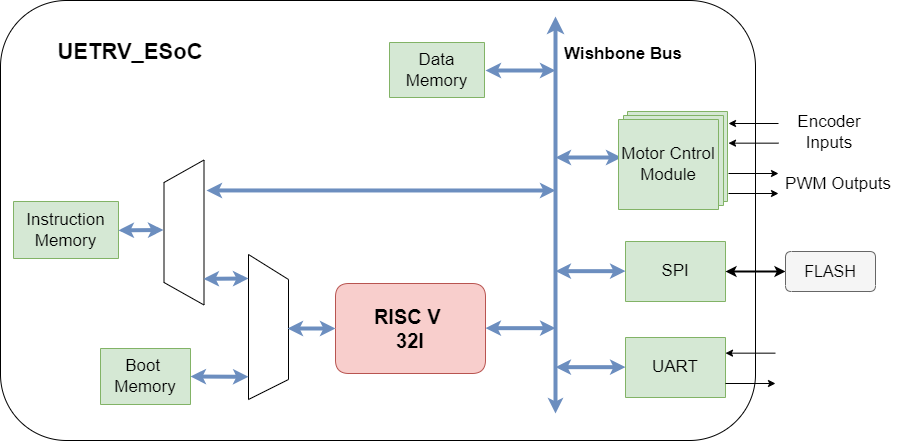

UETRV_ESoC is a RISC-V based Embedded class SoC integrating 3-stage pipelined core with multiple peripherals for embedded applications. Currently, the core implements RV32I ISA based on User-level ISA Version 2.0 and Privileged Architecture Version 1.11 supporting machine mode only. The core does not have any structural hazards, while data hazards are resolved using forwarding and stalling. Following is the status of current implementation:

- Machine level interrupts has been added, including the support for vectored interrupts.

- External interrupts are supported using bits 16 and above of MIP & MIE CSRs as provisioned by Privileged Architecture Version 1.11.

- Data hazards are resolved using forwarding, while Load-Use hazard leads to one cycle stall.

- Memory and peripherals are integrated through Wishbone Interconnect.

- The SoC has on-chip pre-initialized boot memory with a simple boot loader.

- The system boots from external flash using SPI interface.

- Three motor control modules, capable of controlling dc-servo motors with encoder feedback, have been integrated for coordinated multi-axis motion control.

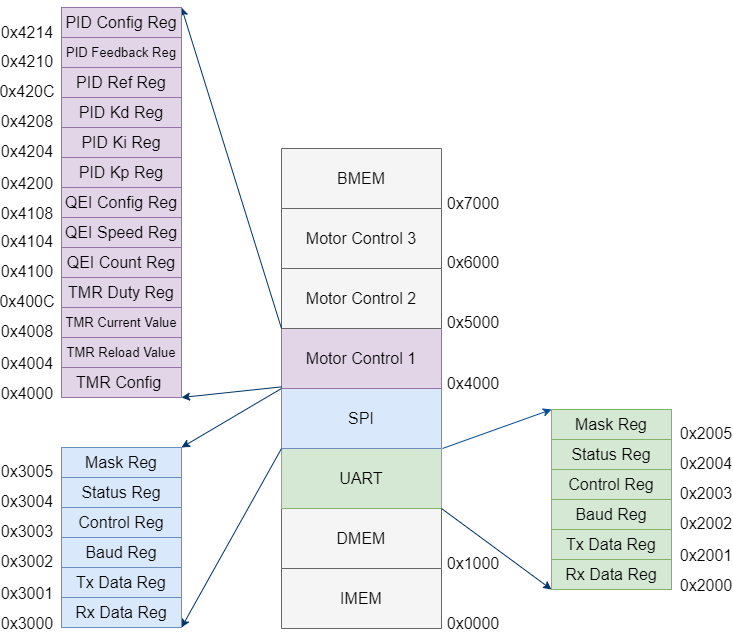

The memory map of SOC is shown in the following table

| Base Address | Description | Attributes |

|---|---|---|

| 0x0000_0000 | Instruction Memory | R-X-W |

| 0x0000_1000 | Data Memory | R-W |

| 0x0000_2000 | UART | R-W |

| 0x0000_3000 | SPI | R-W |

| 0x0000_4000 | Motor Control 1 | R-W |

| 0x0000_5000 | Motor Control 2 | R-W |

| 0x0000_6000 | Motor Control 3 | R-W |

| 0x0000_7000 | Boot Memory | R-X |

R: Read accessW: Write accessX: Execute access

The pictorial representation of memory map is in the following picture.

The linker.ld file has the memory defination as follows.

MEMORY

{

FLASH_INST (rx) : ORIGIN = 0x00000000, LENGTH = 2K

FLASH_BOOT (rx) : ORIGIN = 0x00007000, LENGTH = 1K

RAM (rwx) : ORIGIN = 0x00001000, LENGTH = 2K

}

Different building blocks for the SoC are integrated using the top module './src/main/scala/soc_tile.scala'. To generate the Verilog, Scala Build Tool (sbt) and its dependencies needs to be installed. The verilog code can be generated by executing the following command:

> sbt run

The output verilog file './soc_tile.v' has been generated using sbt 1.3.13.

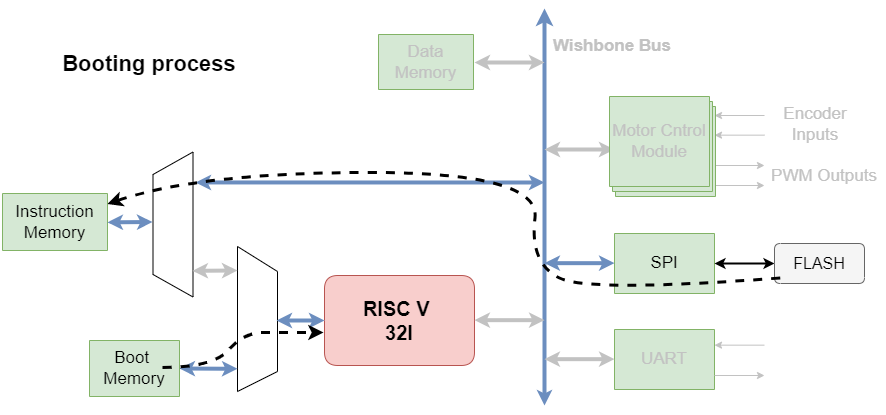

Out of reset, the Boot Memory is invoked by the core and the processor starts executing the instructions that are hard coded into the Boot memory. As a result of this execution, the Application program is loaded from the external SPI FLASH Memory into the Instruction Memory. This phenomenon is demonstrated using the following diagram.

Two application example programs are provided for demo purpose. A simple demo program prints hello using the uart interface ('.\examples\uart'). The second program demonstrates the working of the motor module and is also illustrated using the demo video. Assuming the compilation tools are available, executing the 'make.bat' generates 'imem.c', which is used by the SPI flash programmer to write the flash. The demo video below further explains the working of the project.

The project demo includes an FPGA based implementation to control a DC motor with encoder feedback. The demo project illustrating the motor control configuration is available here. The FPGA based implementation is available here.

A simple bootloader for SPI flash is implemented and has been integrated in the SoC using preinitialized boot memory ('.\src\main\scala\memory\bmem.scala'). The bootloader source code and further details are available here.

A custom SPI flash memory progammer, using TI's TivaC embedded board is also developed and is available in a separate repo.