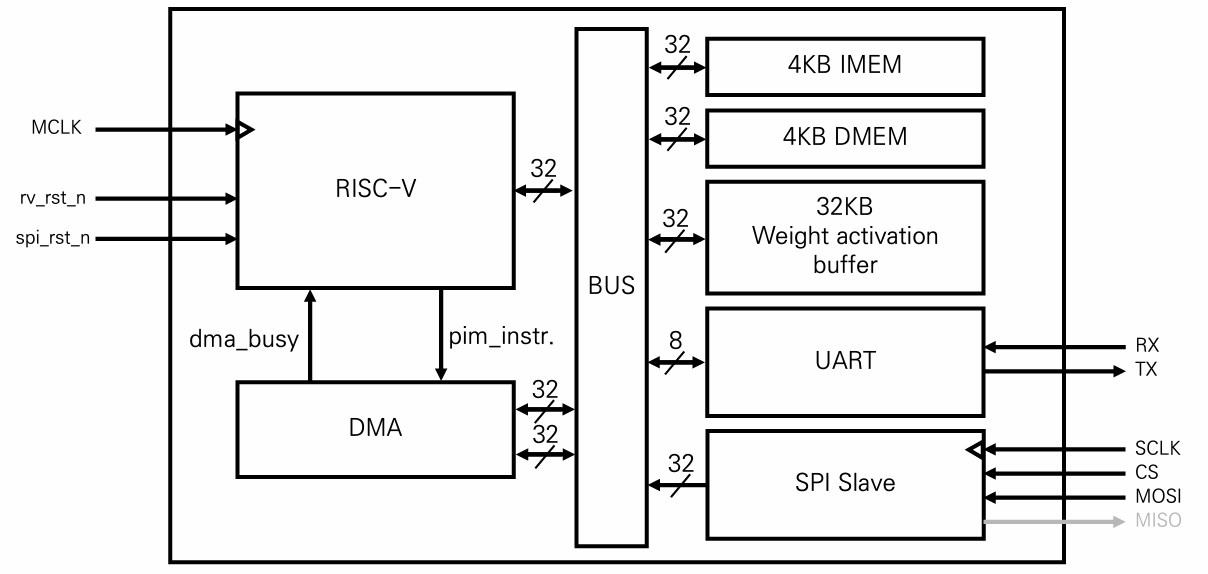

4-stage, in-order core which implements the 32-bit RISC-V instruction set.

- [v] Base Instruction (RV32I)

Peripherals

- [v] UART

- [v] SPI Slave

The following instructions will allow you to compile and run an icarus verilog model of the core within the Cocotb testbench sim/test_core.py.

- Checkout the repository

git clone https://github.com/jypark1257/rv_mpw.git- Install the GNU Toolchain riscv-gnu-toolchain

git clone https://github.com/riscv-collab/riscv-gnu-toolchain.git --recursive

cd riscv-gnu-toolchain

./configure --prefix=/opt/riscv

sudo make- Install the sifive elf2hex

git clone https://github.com/sifive/elf2hex.git

cd elf2hex

autoreconf -i

./configure --target=riscv64-unknown-elf

make

make install- Install the testbench environment cocotb

sudo apt-get install make python3 python3-pip

pip install cocotbAssembly tests are done by using test programs from riscv-tests .

- Compile test programs using Makefile

software/asm_tests/Makefile.- To compile a specific extension test program, use the

EXTENTvariable.

- To compile a specific extension test program, use the

- Run cocotb testbench model in

sim/asm_sim/test_asm.py.

Here is how you can test rv32imf assembly test with the cocotb testbench:

cd software/asm_test

# Compile test programs using Makefile

# default test extension = rv32i

make EXTENT=rv32ui

cd ../../sim/asm_sim

make