A MIPS hardware design for the Computer Design Discipline (6th semester) Computer Engineering @ Insper.

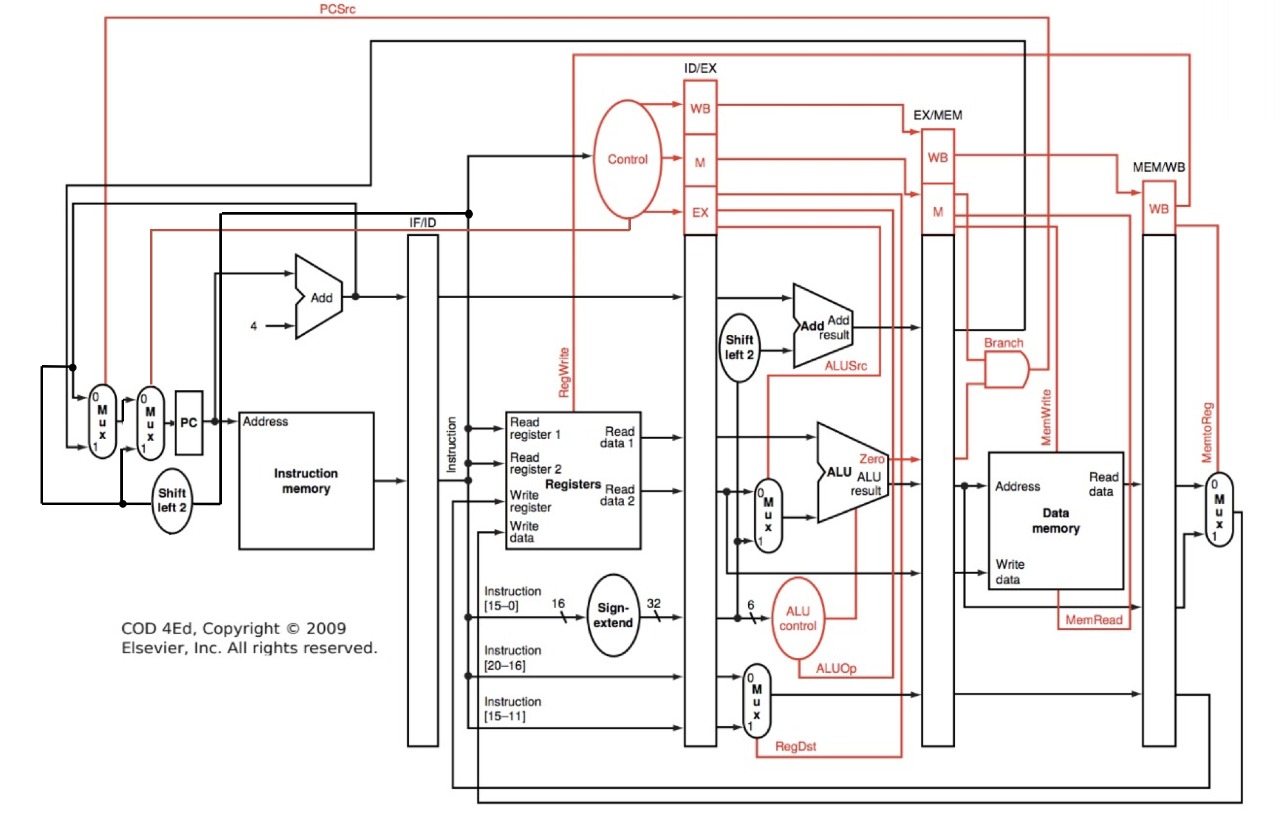

Implemented pipeline version of the MIPS processor.

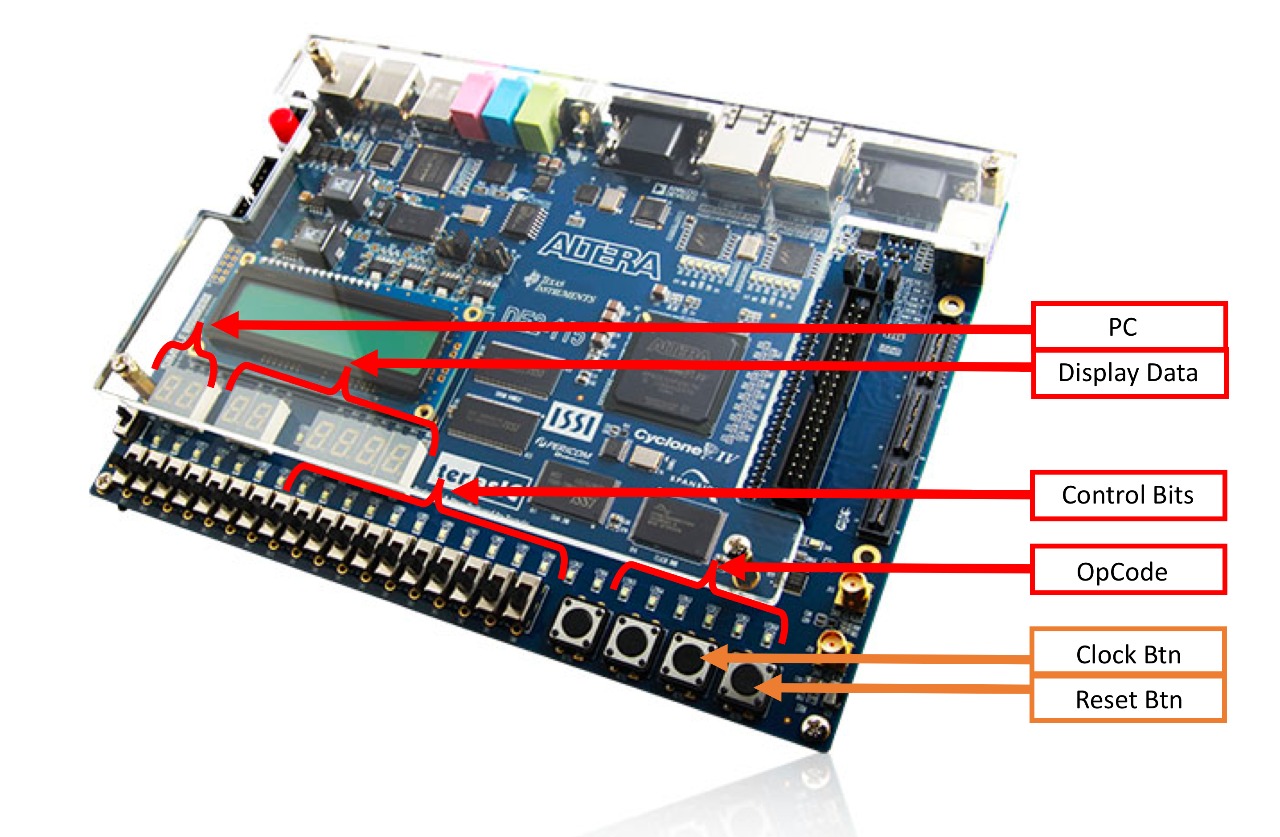

The concept was to develop a MIPS architecture processor in VHDL, that would run on a Altera FPGA board.

With the goal of learning computer design by doing, we implemented a instruction-set of 9 instructions, that run in a pipeline.

An available Single-cycled version of the MIPS Processor can be found in the md-working branch.

in black: the Dataflow in red: the Control unit

Top Level Entity: MIPS Handles the interaction between the Dataflow and ControlUnit

Program: Instruction Program

The current implementation of the processor doesn't handle Hazards. Meaning that any instruction conflict needs to be solved with nops in the compiler.

This images shows the usage of the board functionalities.

This version of MIPS instruction set counts with the following instructions:

- ADD

- SUB

- AND

- OR

- SLT

- LW

- SW

- BEQ

- JUMP

- Hazard prevention

- Refactor components using 'generic'