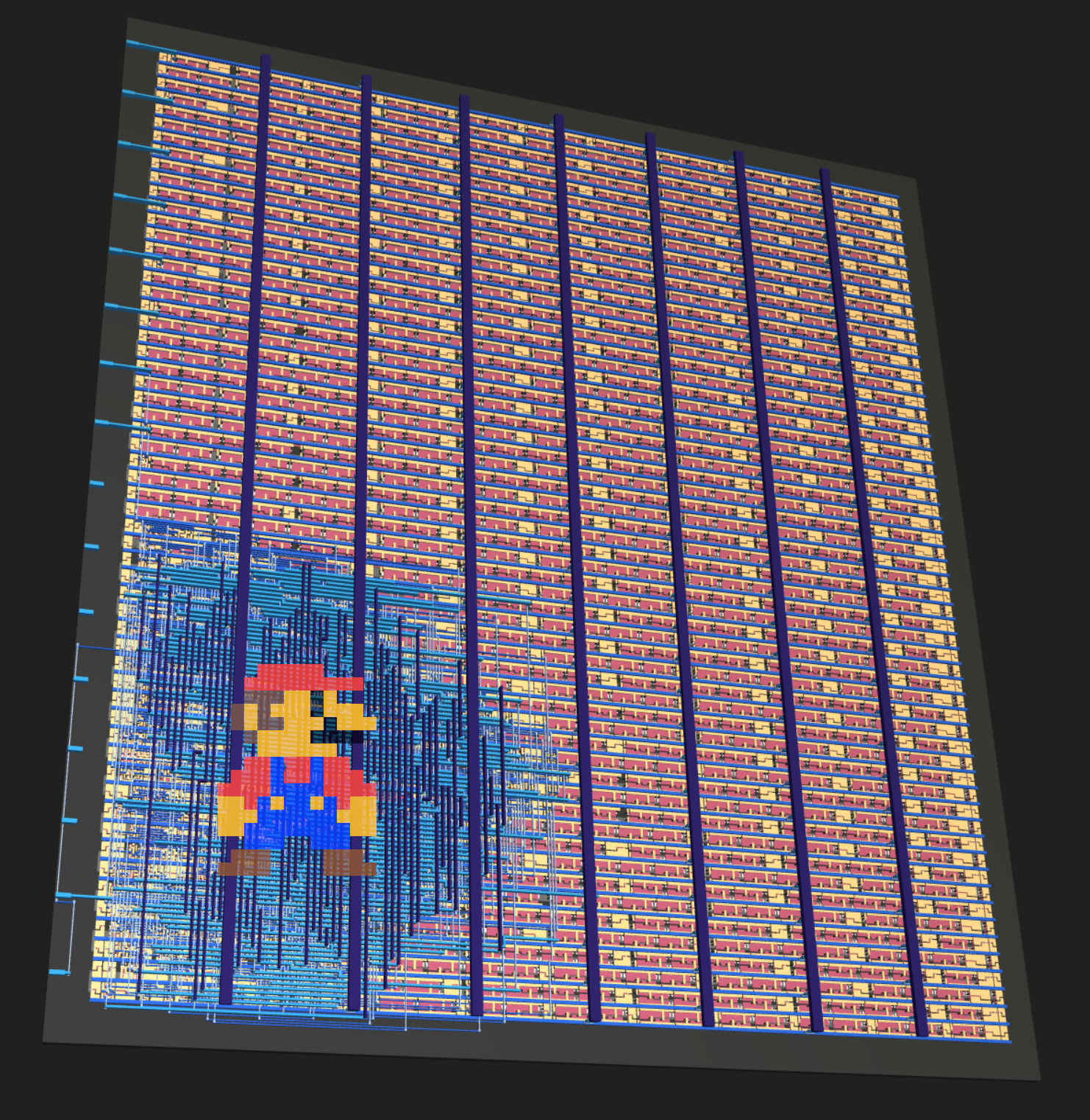

This Verilog chip design is made for the TinyTapout tt03 shuttle. It will play the Super Mario Tune over a Piezo Speaker connected across io_out[1:0]. The speaker is driven in differential PWM mode to increase its output power.

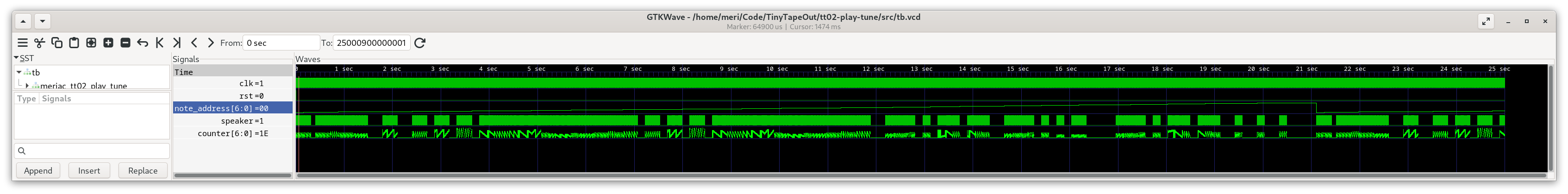

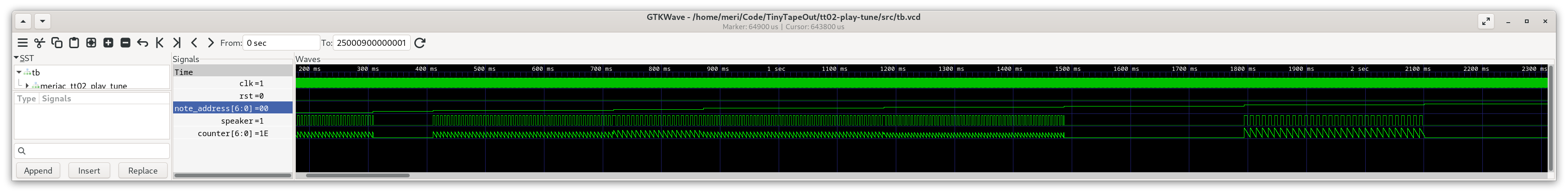

Listen to the Verilog Simulation PWM output for 62505Hz clock frequency here.

(see also the interactive version of this design)

(see also the interactive version of this design)

- Playback Logic

- Autogenerated Super Mario Tune Storage. This project contains a Python-based script for converting a RTTL ringtone into optimized Verilog. An additional script converts TIM-file waveforms from the Verilog simulator back to a WAV-sound file to verify the correctness of the hardware-based player's sound.

Using GTKWave for visualization of Simulation Results:

Provide 6250Hz clock on io_in[0], briefly hit reset io_in[1] (Low, High, Low) and io_out[1:0] will play a differential sound wave over piezo speaker (Super Mario Tune).

Piezo speaker connected across io_out[1:0]