SpaceFFT

Signal Processing ACcElerator For Fast Target detection (SPACEFFT detection)

Overview

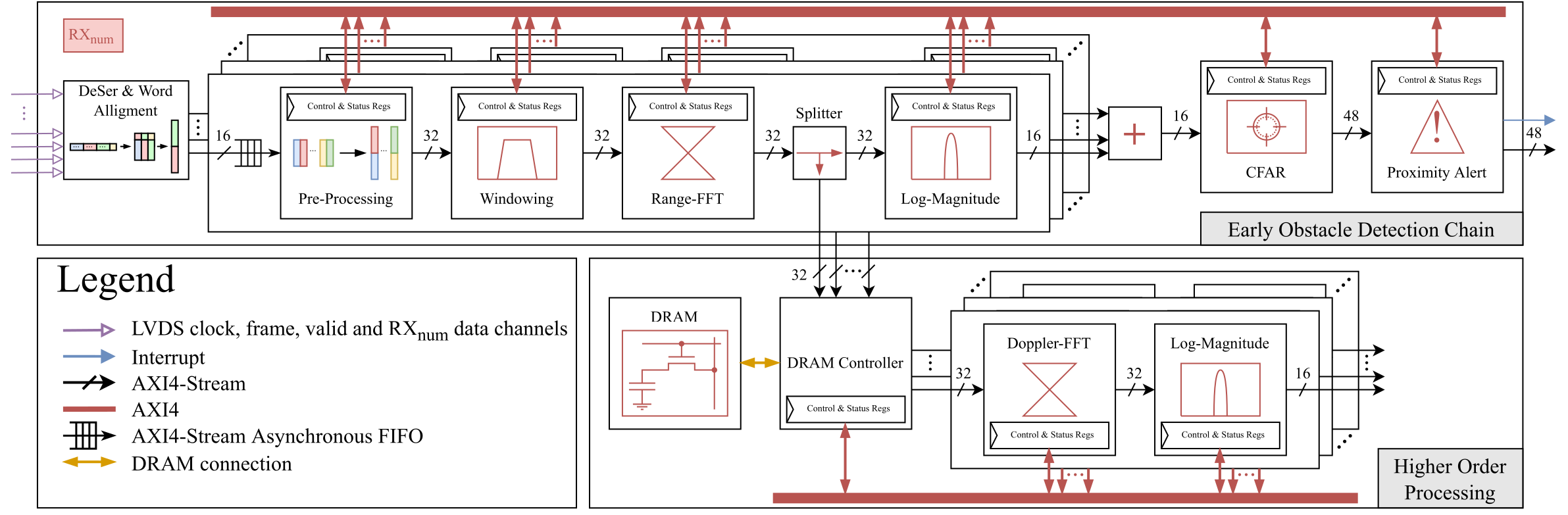

This repository contains a radar signal processing architecture for early detection of automotive obstacles that does not impede subsequent higher order processing. Proposed architecture was designed using agile digital design methodology and it is written in Chisel hardware design language. This architecture is suitable for interfacing with different types of automotive radar front-ends. It supports a collection of pipelined FFT processors with plethora of parameterization options and multiple different variants of CFAR algorithm.

Prerequisites

The following software packages should be installed prior to running this project:

Parameter settings

Design parameters are defined inside case class DissertationParameters. Users can customize design per use case by setting the appropriate parameters.

To understand each parameter, the user should read the parameter explanations of the main blocks:

Setup

Clone this repository, switch directory and run tests:

git clone https://github.com/milovanovic/SpaceFFT.git

cd SpaceFFT

git submodule update --init --recursiveGenerate verilog

To generate verilog code run:

make SpaceFFTVerilog code will be generated in folder:

verilog/SpaceFFT