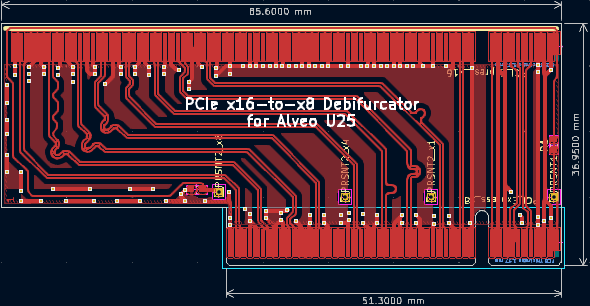

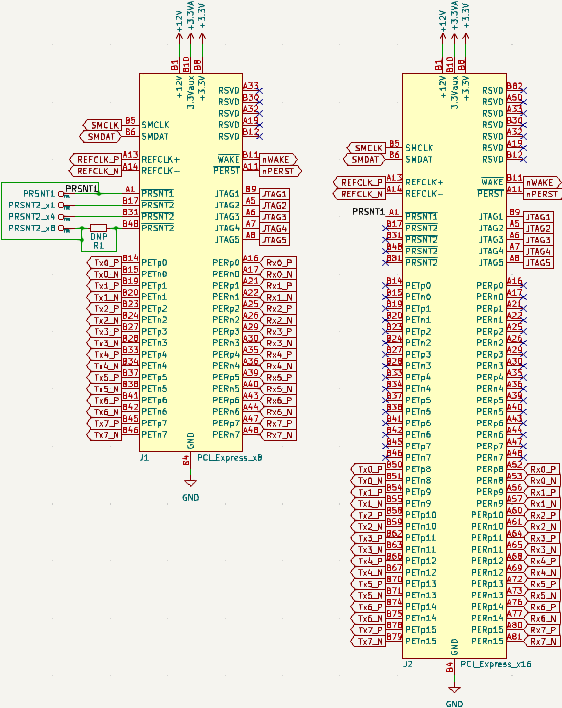

Designed for use with the Alveo U25 which has an x16 PCIe interface that is bifurcated to two x8 interfaces, one for the SFC9250 X2 GbE Controller and the other for the XCZU19EG FPGA. This board connects the FPGA's PCIe x8 interface directly to a host system. The X2 GbE Controller is disconnected and ignored.

Only a straddle-mount PCIe x16 Connector is required, such as: 10025026-10103TLF, 10025026-10003TLF, or 10146027-A40010LF.

Related Projects: alveo_u25_notes, AlveoU25_JTAG_Adapter, ATX_Boot_Delay

I have been able to successfully test an XDMA design using the debifurcator and an Alveo U25 in a system that does not support PCIe Bifurcation.

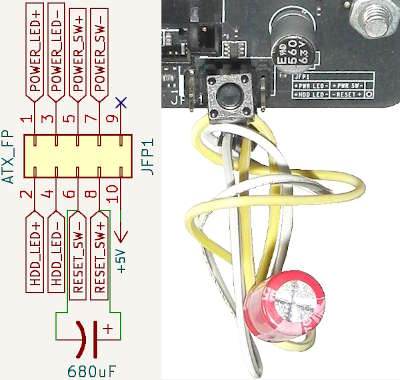

The XCZU19EG uses its ARM processor to configure the FPGA's Programmable Logic (PL) bitstream. It is difficult to get this to finish within the PCIe Specification's 100ms time limit. Motherboard boot must be delayed to allow the FPGA to configure itself before PCIe devices are enumerated by the host system. This can be accomplished by toggling the POWER button, then pressing and holding the RESET button for a second before releasing it. Or, connect a capacitor across the reset pins of an ATX motherboard's Front Panel Header:

All differential pairs are length-matched to within 1mm both inter-pair and intra-pair.

The PCIe Connector's Mounting Post needs to be snapped off with needle-nose pliers.

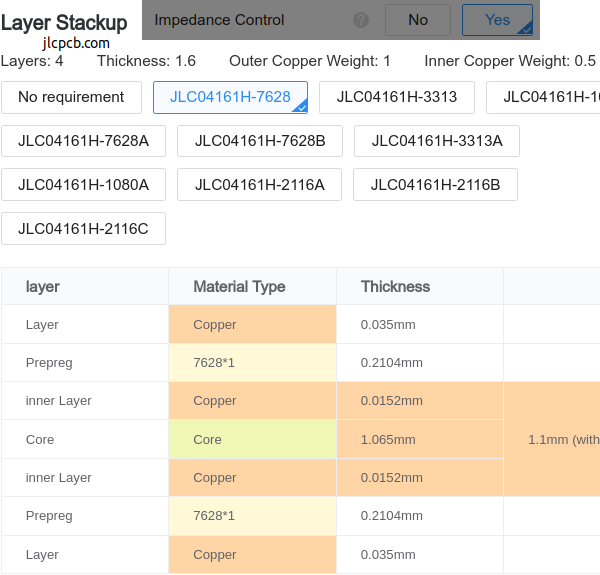

4-Layer PCB stackup taken from JLCPCB.

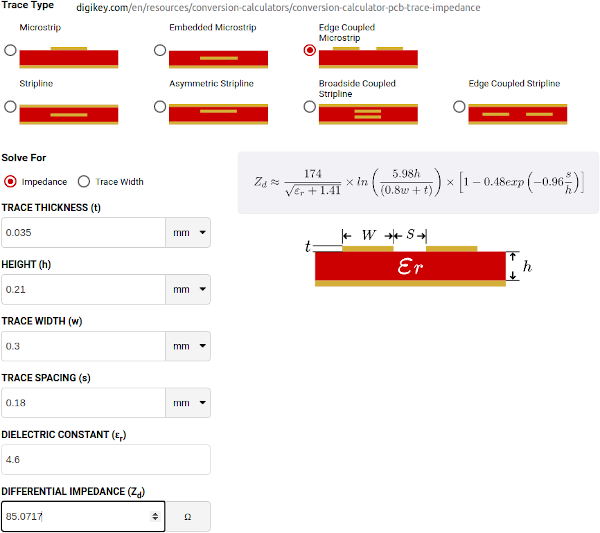

Differential Impedance parameters were calculated using the DigiKey Online Calculator.