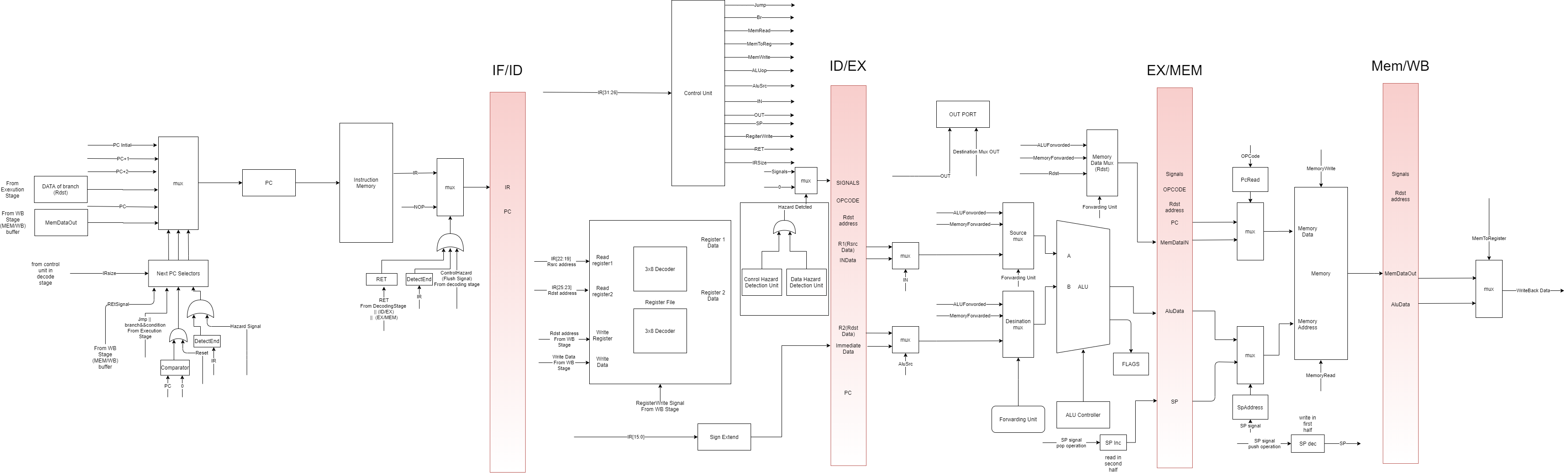

32-bit 5-stage pipelined processor has a RISC-like instruction set and Harvard Archeticure with features as:

- Forwarding Unit (Data-Hazard)

- ALU Forwarding

- Memory Forwarding

- Hazard Detection Unit (For Stalling)

- Data Hazard Load-Use Case

- Control Hazards

- Static Branch Prediction

| Fetch |

Decode |

Execute |

Memory |

Write Back |

| General Purpose Registers |

R0 |

R1 |

R2 |

R3 |

R4 |

R5 |

R6 |

R7 |

|

Program Counter

|

PC

|

|

Stack Pointer

|

SP

|

| Jump |

Branch |

MemRead |

MemToReg |

MemWrite |

AluOp |

AluSrc |

In |

Out |

SP |

RegisterWrite |

Ret |

IRSize |

| 2-Operand |

1-Operand |

Immediate |

InOut |

Jump |

Stack |

| Operations Type [31:29] |

Function Opcode [28:26] |

Rdst [25:23] |

Rsrc [22:20] |

| Operation |

Function |

| NOP |

No operation -zeros control signals- |

| SETC |

Set Carry Flag - Carry=1 - |

| CLRC |

Clear Carry Flag - Carry=0 - |

| MOV Rsrc , Rdst |

Move value from register Rsrc to register Rdst |

| ADD Rsrc , Rdst |

Add the values stored in registers Rsrc, Rdst

and store the result in Rdst and updates carry |

| SUB Rsrc, Rdst |

Subtract the values stored in registers Rsrc, Rdst

and store the result in Rdst and updates carry |

| AND Rsrc, Rdst |

AND the values stored in registers Rsrc, Rdst

and store the result in Rdst |

| OR Rsrc, Rdst |

OR the values stored in registers Rsrc, Rdst

and store the result in Rdst |

| Operations Type [31:29] |

Function Opcode [28:26] |

Rdst [25:23] |

Rdst [22:20] |

| Operation |

Function |

| CLR Rdst |

Sets Rdst to zeros |

| NOT Rdst |

NOT value stored in register Rdst |

| INC Rdst |

Increment value stored in Rdst |

| DEC Rdst |

Decrement value stored in Rdst |

| NEG Rdst |

Negate the value stored in register Rdst |

| RLC Rdst |

Rotate left Rdst ; Carry ←R[ Rdst ]<31>;

R[ Rdst ] ← R[ Rdst ]<30:0>&Carry |

| RRC Rdst |

Rotate right Rdst ; Carry ←R[ Rdst ]<0>;

R[ Rdst ] ←Carry&R[ Rdst ]<31:1> |

| Operations Type [31:29] |

Function Opcode [28:26] |

Rdst [25:23] |

Rdst [22:20] |

| Operation |

Function |

| OUT Rdst |

OUT.PORT ← Rdst |

| IN Rdst |

Rdst ←IN.PORT |

| Operations Type [31:29] |

Function Opcode [28:26] |

Rdst [25:23] |

Rsrc [22:20] |

Immediate/Offset [15:0] |

| Operation |

Function |

| IADD Rdst,Imm |

Add the values stored in registers Rdst to Immediate Value

and store the result in Rdst and updates carry |

| SHL Rdst, Imm |

Shift left Rdst by #Imm bits and store result in same register |

| SHR Rdst, Imm |

Shift right Rdst by #Imm bits and store result in same register |

| LDM Rdst, Imm |

Load immediate value (16 bit) to register Rdst |

| LDD Rdst, offset(Rsrc) |

Load value from memory address Rsrc + offset to register Rdst |

| STD Rdst, offset(Rsrc) |

Store value that is in register Rdst to memory location Rsrc + offset |

| Operations Type [31:29] |

Function Opcode [28:26] |

Rdst [25:23] |

Rdst [22:20] |

| Operation |

Function |

| JZ Rdst |

Jump if zero : PC ← Rdst; (Z=0) |

| JMP Rdst |

Jump ; PC ← Rdst |

| Operations Type [31:29] |

Function Opcode [28:26] |

Rdst [25:23] |

Rdst [22:20] |

| Operation |

Function |

| PUSH Rdst |

MEM[SP] ← Rdst ; SP-=2 |

| POP Rdst |

SP+=2; Rdst ← MEM[SP] |

- Create new project in modelsim.

- Add all the .vhd files in src to the project.

- start your simulation by running .do file as in do_1.do after changing the directory of the memory1.mem to your directory

This software is licensed under MIT License, See License