Deniser is a drop-in replacement for the Amiga computer Denise chip.

This repository contains board design files, FPGA logic source code and synthesis scripts. The idea is to make the material available for anyone to build and program the board for use as a Denise chip replacement.

Denise is the Amiga custom chip responsible for most of the graphic related tasks such as bitplane display, palette registers, smooth scrolling, hardware sprites, flexible screen object priority, collision detection and more. In the Amiga, Denise operates in concert with the Agnus (DMA, blitter, copper) and Paula (I/O, interrupt controller). The chipset was released in 1985.

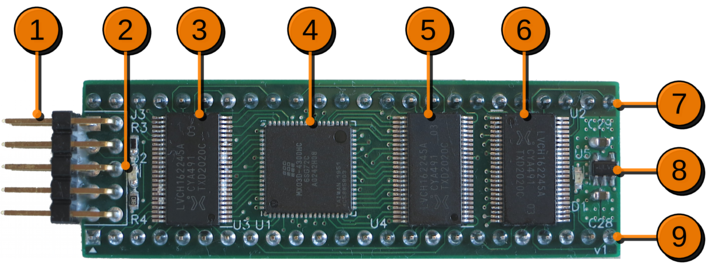

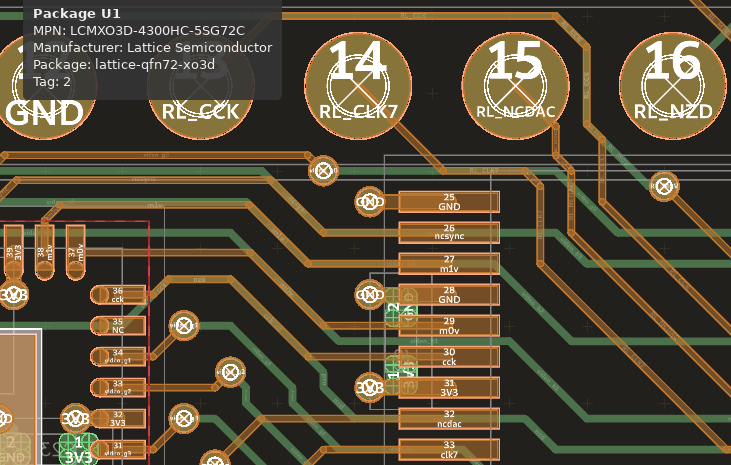

| Item | Description | Item | Description |

|---|---|---|---|

1 |

JTAG header |

4 |

MachXO3D FPGA |

2 |

User LED |

7, 9 |

48-pin DIP connector |

3, 5, 6 |

Bus transceiver 5 V ←→ 3.3 V |

8 |

Voltage regulator |

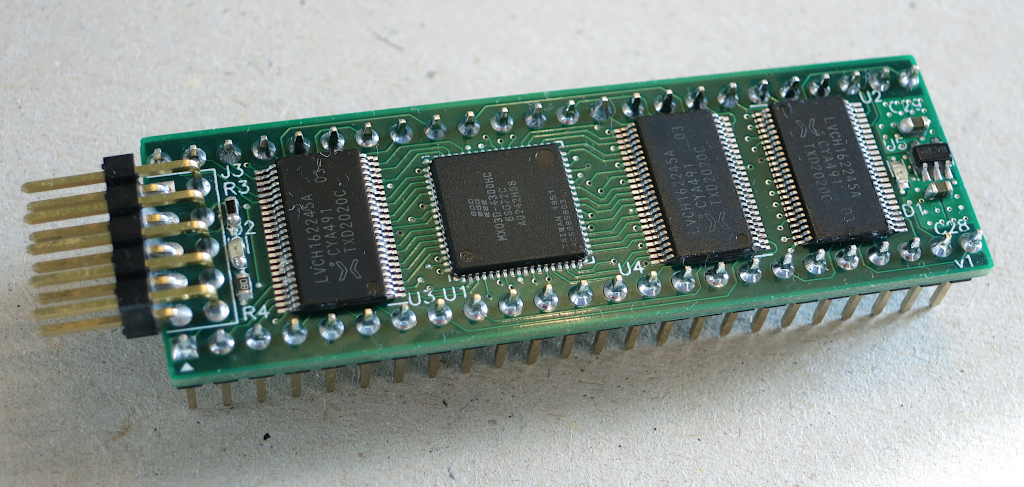

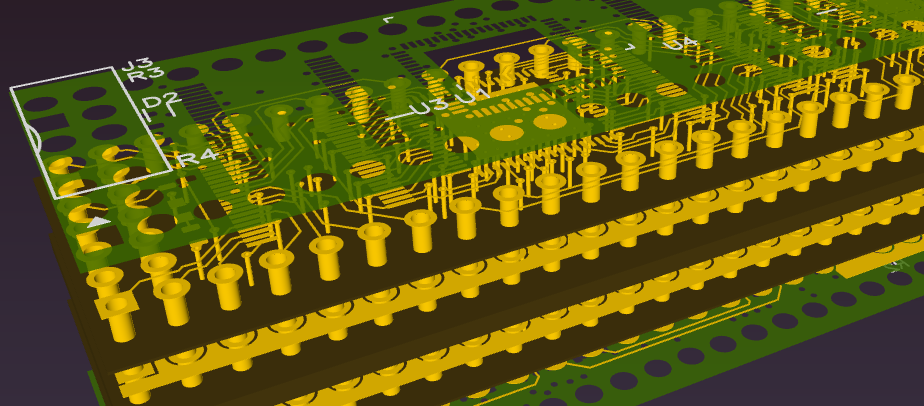

The Deniser board has 48-pin DIP form factor ready to be mounted in an IC socket. Schematic, BOM and more information can be found in the dedicated Deniser board document.

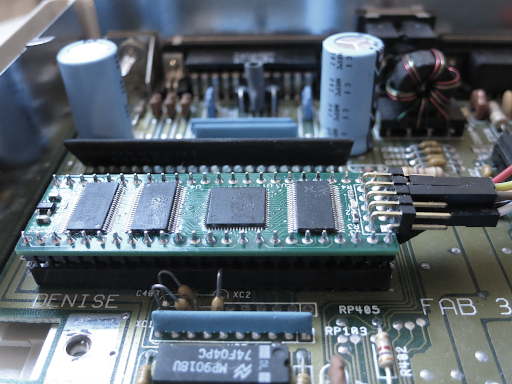

Installation is as easy as removing the original Denise IC from its socket and put the Deniser board in its place.

The jumper wires in the picture are not required for normal operation and can be disconnected after the FPGA on-chip configuration flash has been programmed.

Schematic and board layout is designed using Horizon EDA. Project files are located in the pcb directory from which Gerber files and bill of materials (BOM) can be generated.

The digital logic is written in VHDL. Source code can be found in the hdl directory.

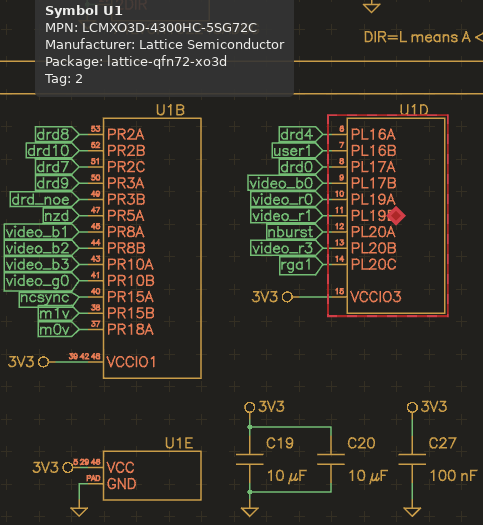

Lattice MachXO3D is the target FPGA device. The vendor tool Lattice Diamond 3.12 comes with the third party tool Synplify for synthesis and ModelSim for simulation.

To run the synthesis and place and route flow with Lattice Diamond:

cd dia make export

The above command generates an FPGA bitstream.

Configure the FPGA volatile RAM with make conf, or

program the FPGA non-volatile flash with make prog.

Information on how to connect the JTAG interface is available in the

Deniser board documentation.

make slaunch starts an interactive Synplify synthesis session.

make launch brings up Lattice Diamond interactively for working with

the constraints, floor plan, etc.

The Deniser board is licensed under the GNU General Public License version 2 or any later version. This applies to the design files (schematic and board layout) in the pcb directory.

The logic design is licensed under the GNU General Public License version 2 or any later version. This applies to the VHDL files in the hdl directory.

-

Known to work:

-

Schematic, PCB layout and BOM

-

Use in Amiga A500 with ECS Agnus (PAL)

-

Workbench, Deluxe Paint, demos

-

Extra Half Brite (EHB) mode

-

OCS features

-

-

Things that probably work:

-

Use in Amiga A1000, A2000 and A3000

-

Use with OCS Agnus

-

Collision detection

-

Hold-and-modify (HAM) mode

-

Genlock

-

-

Known limitations:

-

Some sprites appear above and below the display window.

-

No NTSC

-

The Deniser has been developed based on information in the following sources.