GPGPU processor supporting RISCV-V extension, developed with Chisel HDL.

Copyright 2021-2023 by International Innovation Center of Tsinghua University, Shanghai

We are calling for contributors. If you are interested in Ventus GPGPU, please contact yang-zx21@mails.tsinghua.edu.cn

“乘影”在RVV编译器工具链、验证环境开发和硬件设计方面还有很多不足,如果您有意愿参与到“乘影”的开发中,欢迎在github上pull request,也欢迎联系 yang-zx21@mails.tsinghua.edu.cn

乘影2.0架构文档在这里,添加了对OpenCL支持所需的改动。如果您在软硬件方面有任何建议,欢迎提issue或邮件联系。

乘影开源GPGPU项目网站:opengpgpu.org.cn

Home page of Ventus-GPGPU project: opengpgpu.org.cn

乘影软件工具链release版本在这里获取.

You can get the release version of software toolchain here.

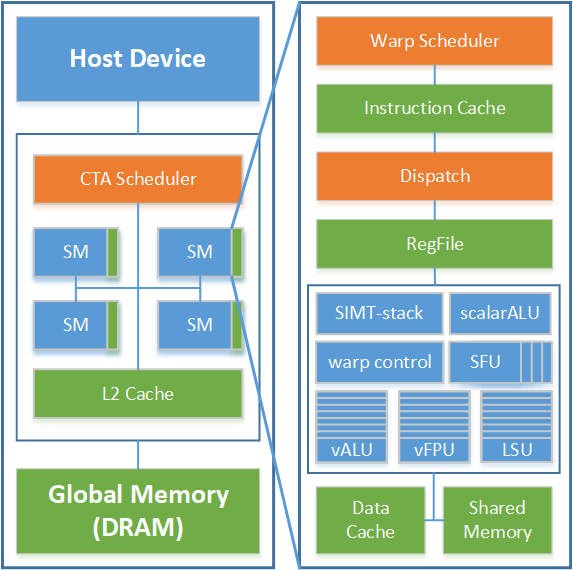

The micro-architecture overview of Ventus(乘影) is shown below.

ISA and micro-architecture docs is here. Chinese docs is here.

OpenCL C compiler based on LLVM is developed by Terapines(兆松科技).

Use the script in ventus-llvm to configure the complete software toolchain, including isa-simulator, pocl and driver.

从零开始的配置教程(中文,从WSL和IDEA安装讲起)

The tutorial of Chisel development environment configuration comes from chipsalliance/playground: chipyard in mill :P

- Install dependencies and setup environments:

- Arch Linux

pacman -Syu --noconfirm make parallel wget cmake ninja mill dtc verilator git llvm clang lld protobuf antlr4 numactl - Nix

nix-shell - Ubuntu

apt-get install make parallel wget cmake verilator git llvm clang lld protobuf-compiler antlr4 numactl

curl -L https://github.com/com-lihaoyi/mill/releases/download/0.10.8/0.10.8 > mill && chmod +x millWe recomment using java 17 or higher versions.

- Init and update dependences

make init

make patch-

IDE support

make bsp # generate IDE bsp -

to generate verilog file, use

make verilog. The output file isGPGPU_top.v. Notice that if you install 'mill' with 'curl', use./millto replacemillin Makefile commands. -

to run tests, use

make tests. Output waveform file is attest_run_dir

Notice that current codes are not stable and there are conflicts between existing codes and testcase

gaussiangemm. We are preparing new testcase format to integrate with software toolchain and please wait for our new version.

We refer to some open-source design when developing Ventus GPGPU.

| Sub module | Source | Detail |

|---|---|---|

| CTA scheduler | MIAOW | Our CTA scheduler module is based on MiaoW ultra-threads dispatcher. |

| L2Cache | block-inclusivecache-sifive | Our L2Cache design is inspired by Sifive's block-inclusivecache |

| Multiplier | XiangShan | We reused Array Multiplier in XiangShan. FPU design is also inspired by XiangShan. |

| Config, ... | rocket-chip | Some modules are sourced from RocketChip |