For Bit manipulation analysis, implementation, and documentation within the workgroup.

Editor: Po-wei Huang

* Verilog coding: Done, but just for 32 bit now, 64 bit version not finished.* Verification: Not yet.

* Evaluation: Done, as long as there is not a bug inside verilog code. Please see the analysis section.

TBD The reference implementation comes from [1].

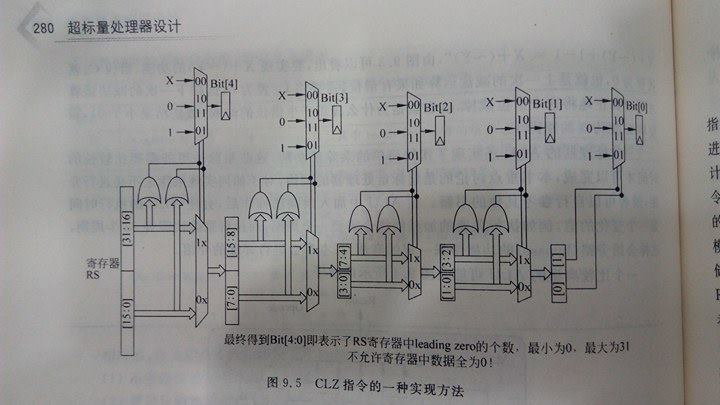

For code in verilog, please refer to CLZ.v. From the verilog code and architecture diagram, I'm convinced that it's log(N) for timing.

For further evaluation, we should use EDA tool to see the critical path for 32 bit and 64bit to verify that it's log(N) in timing.

* Verification not yet.* 64 bit version .

* Synthesize to make sure it's log(N).

* Considering area effect.

[1]. Superscalar processor design (a chinese book)

http://www.books.com.tw/products/CN11105742