It is a designed implementation of Direct Mapped Cache in Verilog.

The cache is designed to hold 256 BLocks, each containing 16 words (words = 32-bits), with 32-bit address line

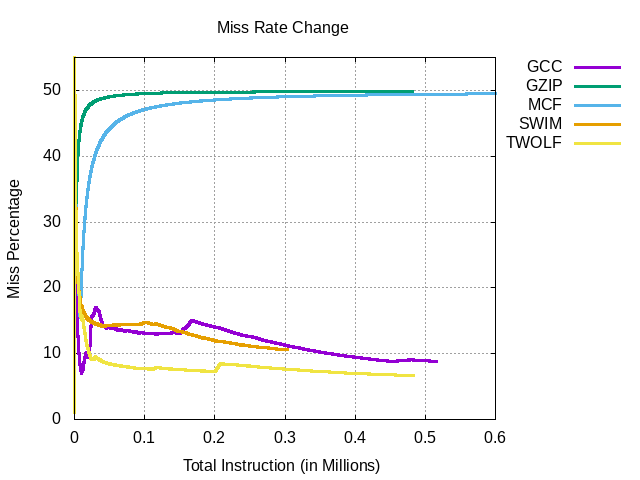

This plot is showing how miss rate for a specific compiler varies with number of instructions given it to run

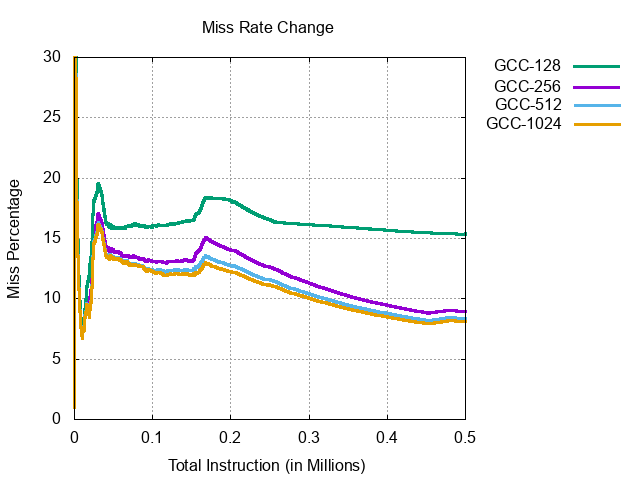

This plot is analysis of how "miss rate" change with number of instructions given it to run, for a GCC compiler when number of blocks in the cache is varied. Different plots representing how miss rate decreases with increase in size of cache.