This project provides a Python script for detecting data hazards in MIPS assembly instructions and generating timing diagrams for pipeline stages. The script supports ADD, SUB, LW (load word), and SW (store word) instructions. It can handle both scenarios with and without a forwarding unit, inserting stalls as needed to resolve hazards.

- Data Hazard Detection: Detects RAW (Read After Write), WAR (Write After Read), and WAW (Write After Write) hazards.

- Timing Diagram Generation: Generates timing diagrams showing the pipeline stages (Fetch, Decode, Execute, Memory, Write Back).

- Forwarding Unit Support: Supports scenarios with and without a forwarding unit, adjusting the timing diagram accordingly.

- Python 3.x

--commands: Pipe-separated list of MIPS commands.--operation: Desired operation -detectto find all hazards,timingto generate a timing diagram, orbothto show hazards and generate a timing diagram.--forwarding_unit:onto enable the forwarding unit,offto disable it.

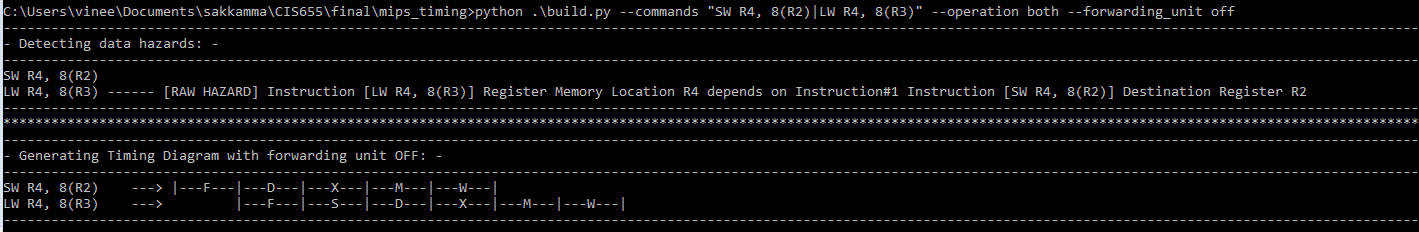

python build.py --commands "SW R4, 8(R2)|LW R4, 8(R3)" --operation both --forwarding_unit off

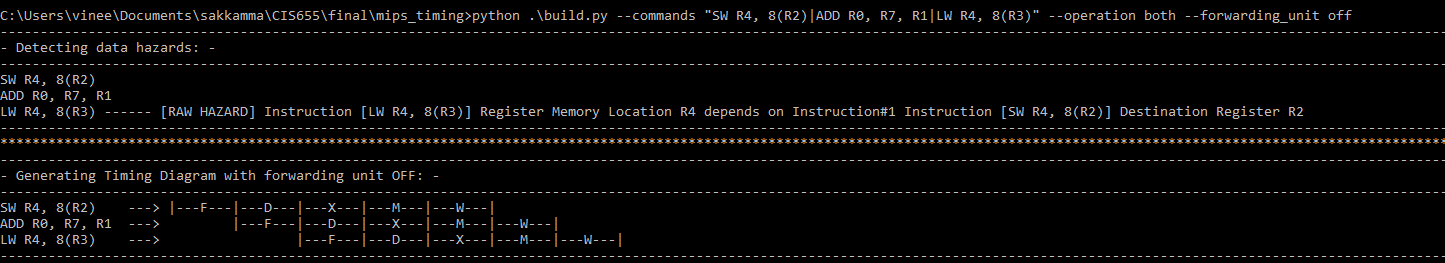

python build.py --commands "SW R4, 8(R2)|ADD R0, R7, R1|LW R4, 8(R3)" --operation both --forwarding_unit offExample output with hazards:

SW R4, 8(R2)

ADD R0, R7, R1

LW R4, 8(R3) ------ [RAW HAZARD] Instruction [LW R4, 8(R3)] Register Memory Location R4 depends on Instruction#1 Instruction [SW R4, 8(R2)] Destination Register R2

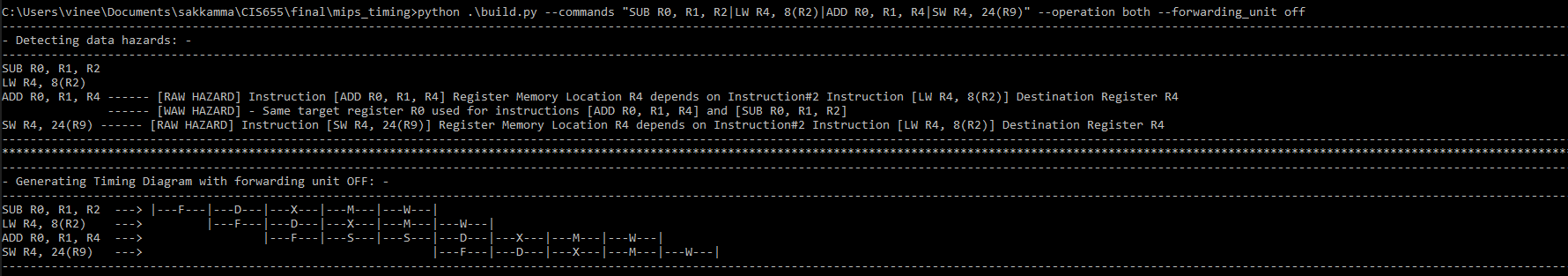

python build.py --commands "SUB R0, R1, R2|LW R4, 8(R2)|ADD R0, R1, R4|SW R4, 24(R9)" --operation both --forwarding_unit offExample output with multiple hazards:

SUB R0, R1, R2

LW R4, 8(R2)

ADD R0, R1, R4 ------ [RAW HAZARD] Instruction [ADD R0, R1, R4] Register Memory Location R4 depends on Instruction#2 Instruction [LW R4, 8(R2)] Destination Register R4

------ [WAW HAZARD] - Same target register R0 used for instructions [ADD R0, R1, R4] and [SUB R0, R1, R2]

SW R4, 24(R9) ------ [RAW HAZARD] Instruction [SW R4, 24(R9)] Register Memory Location R4 depends on Instruction#2 Instruction [LW R4, 8(R2)] Destination Register R4

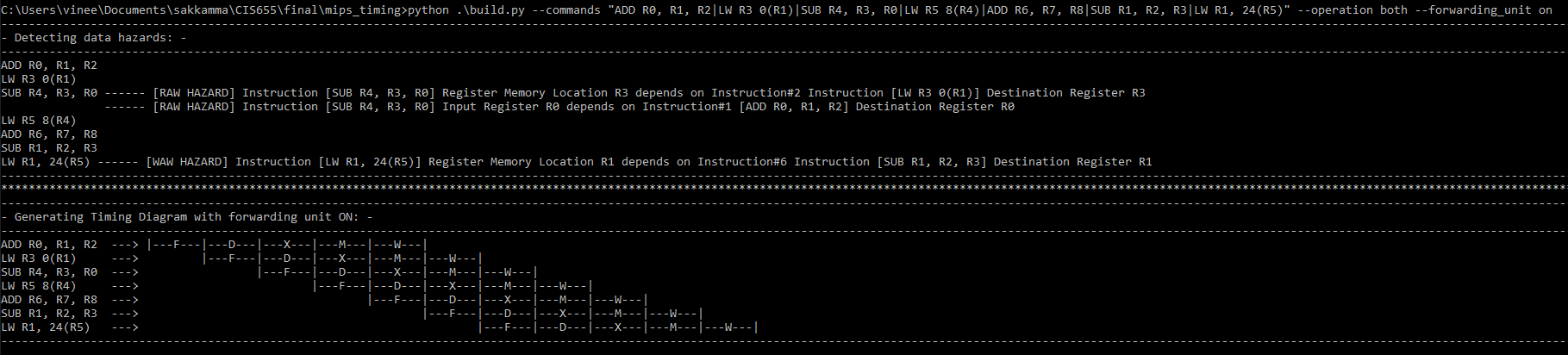

python build.py --commands "ADD R0, R1, R2|LW R3 0(R1)|SUB R4, R3, R0|LW R5 8(R4)|ADD R6, R7, R8|SUB R1, R2, R3|LW R1, 24(R5)" --operation both --forwarding_unit onbuild.py: Main script to detect hazards and generate timing diagrams.helpers.py: Helper functions and classes used bybuild.py.demo_use.txt: Example usage of the script.

To detect hazards and generate a timing diagram for a sequence of MIPS instructions:

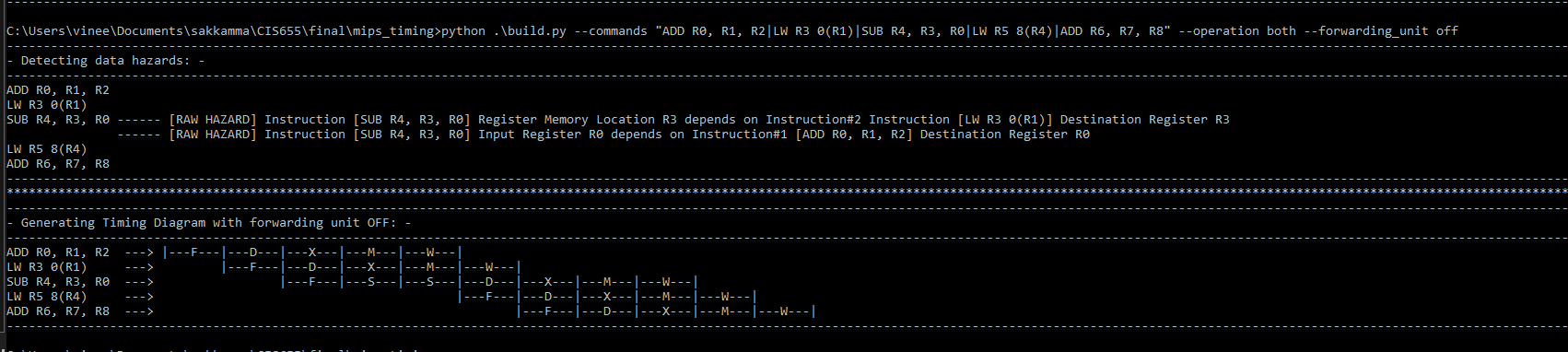

python build.py --commands "ADD R0, R1, R2|LW R3 0(R1)|SUB R4, R3, R0|LW R5 8(R4)|ADD R6, R7, R8" --operation both --forwarding_unit offTo generate a timing diagram with a forwarding unit:

python build.py --commands "ADD R0, R1, R2|LW R3 0(R1)|SUB R4, R3, R0|LW R5 8(R4)|ADD R6, R7, R8|SUB R1, R2, R3|LW R1, 24(R5)" --operation both --forwarding_unit onpython .\build.py --commands "SW R4, 8(R2)|LW R4, 8(R3)" --operation both --forwarding_unit off

python .\build.py --commands "SW R4, 8(R2)|ADD R0, R7, R1|LW R4, 8(R3)" --operation both --forwarding_unit off

python .\build.py --commands "SUB R0, R1, R2|LW R4, 8(R2)|ADD R0, R1, R4|SW R4, 24(R9)" --operation both --forwarding_unit off

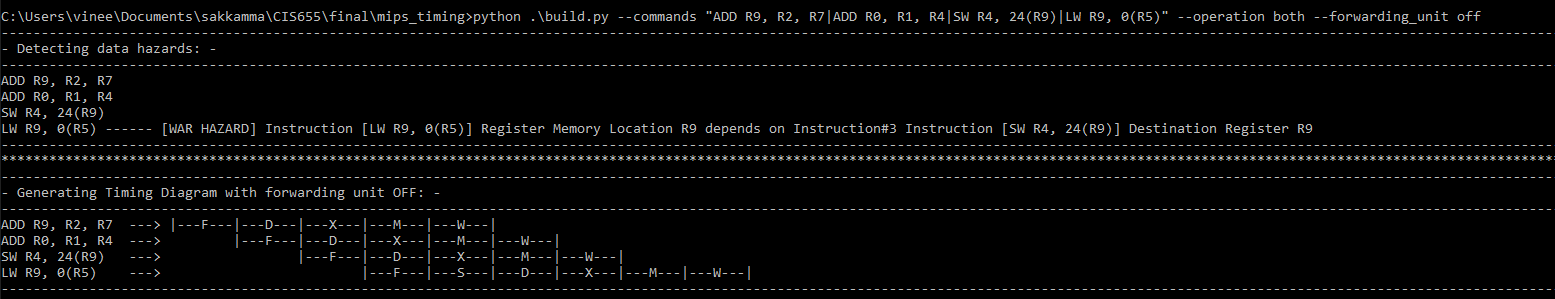

python .\build.py --commands "ADD R9, R2, R7|ADD R0, R1, R4|SW R4, 24(R9)|LW R9, 0(R5)" --operation both --forwarding_unit off

python .\build.py --commands "ADD R0, R1, R2|LW R3 0(R1)|SUB R4, R3, R0|LW R5 8(R4)|ADD R6, R7, R8" --operation both --forwarding_unit off

python .\build.py --commands "ADD R0, R1, R2|LW R3 0(R1)|SUB R4, R3, R0|LW R5 8(R4)|ADD R6, R7, R8|SUB R1, R2, R3|LW R1, 24(R5)" --operation both --forwarding_unit off

python .\build.py --commands "ADD R0, R1, R2|LW R3 0(R1)|SUB R4, R3, R0|LW R5 8(R4)|ADD R6, R7, R8|SUB R1, R2, R3|LW R1, 24(R5)" --operation both --forwarding_unit on

This project is licensed under the MIT License. See the LICENSE file for details.