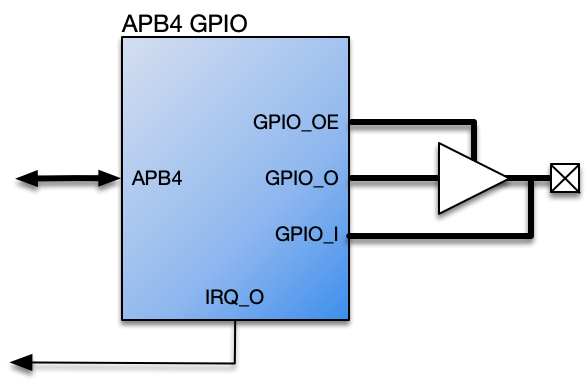

The APB4 GPIO Core is fully parameterised core designed to provide a user-defined number of general purpose, bidirectional IO to a design.

The IO are accessible via an AMBA APB v2.0 Specificationinterface – typically referred to as APB4 – and the core operates synchronously with the rising edge of the APB4 Bus Clock..

Inputs to the core may operate asynchronously to the core and will be automatically synchronised to the bus clock. Outputs may be configured to operate in push-pull mode or open-drain

GPIO inputs may also be individually configured to generate a level or edge sensitive interrupt. A single IRQ output is provided to connect to the host.

- Compliant with AMBA APB v2.0 Specification

- User-defined number of Bi-directional General Purpose IO

- Automatic synchronisation of General Inputs to Bus Clock

- Each General Output configurable as push-pull or open-drain

- Programmable IRQ generation

- Each General Input individually configurable as a level or edge triggered interrupt.

- APB Slave Interface

Released under the RoaLogic Non-Commercial License

This release requires the ahb3lite package found here https://github.com/RoaLogic/ahb3lite_pkg