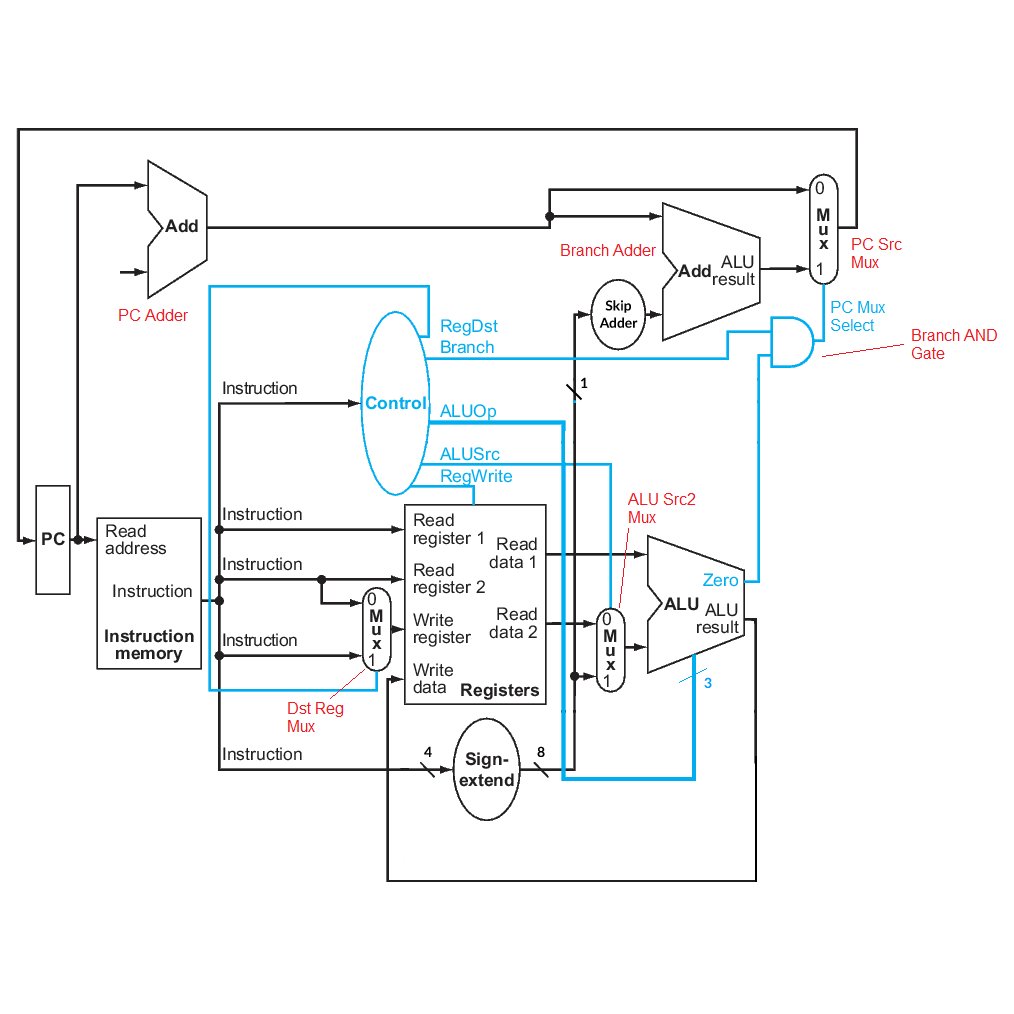

The design of this single-cycle calculator roughly follows the simple, single-cycle MIPS processor shown in this image, including the naming of components:

sudo add-apt-repository ppa:pgavin/ghdl

sudo apt update

sudo apt install ghdl

-

Enter make directory: cd make

-

Remove current test bench binaries (may not be necessary): make clean

-

Make test bench binaries a. Make all test bench binaries make b. Make a specific test bench binary make add2 make alu make and2 make calculator make control_unit make full_adder make half_adder make mux2 make or2 make register_file make sign_extend make xor2 make debug_aluregfile make debug_pc

-

Execute a test bench binary ./add2_tb ./alu_tb ./and2_tb ./calculator_tb ./comparator2_tb ./control_unit_tb ./debug_aluregfile_tb ./debug_pc_tb ./full_adder_tb ./half_adder_tb ./mux2_tb ./or2_tb ./register_file_tb ./sign_extend_tb ./xor2_tb

-

Enter make directory: cd make

-

Remove current test bench binaries (may not be necessary): make clean

-

Make calculator's test bench binary Make all or make calculator (they are equivalent) make make calculator

-

Execute the test bench binary ./calculator_tb

-

Create a GHW Waveform for GTKWave ./calculator_tb --wave=../gtkwave/pipelined.ghw

- We print every clock cycle.

- Overflow and underflow flags are set accordingly internally inside of the calculator, but our calculator never does anything about it.

- Register file does reads just after (not on!) the rising_edge of clock.