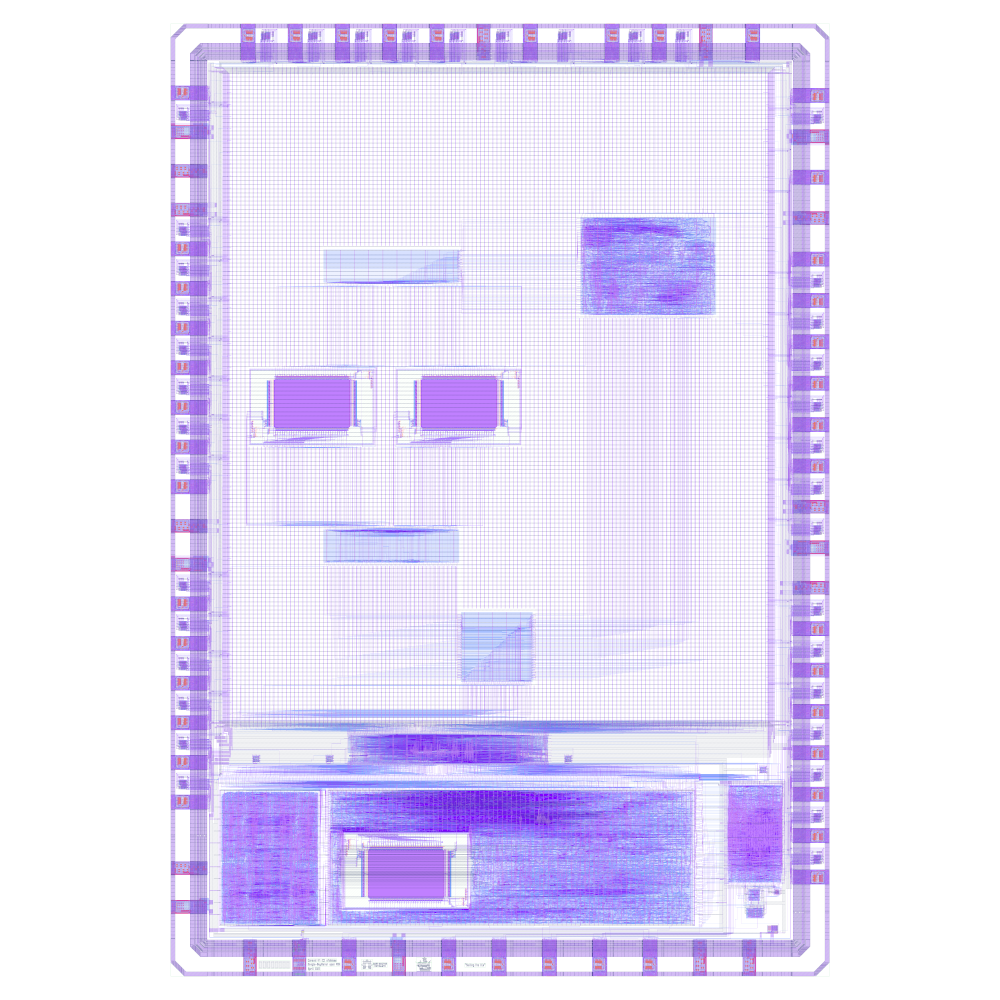

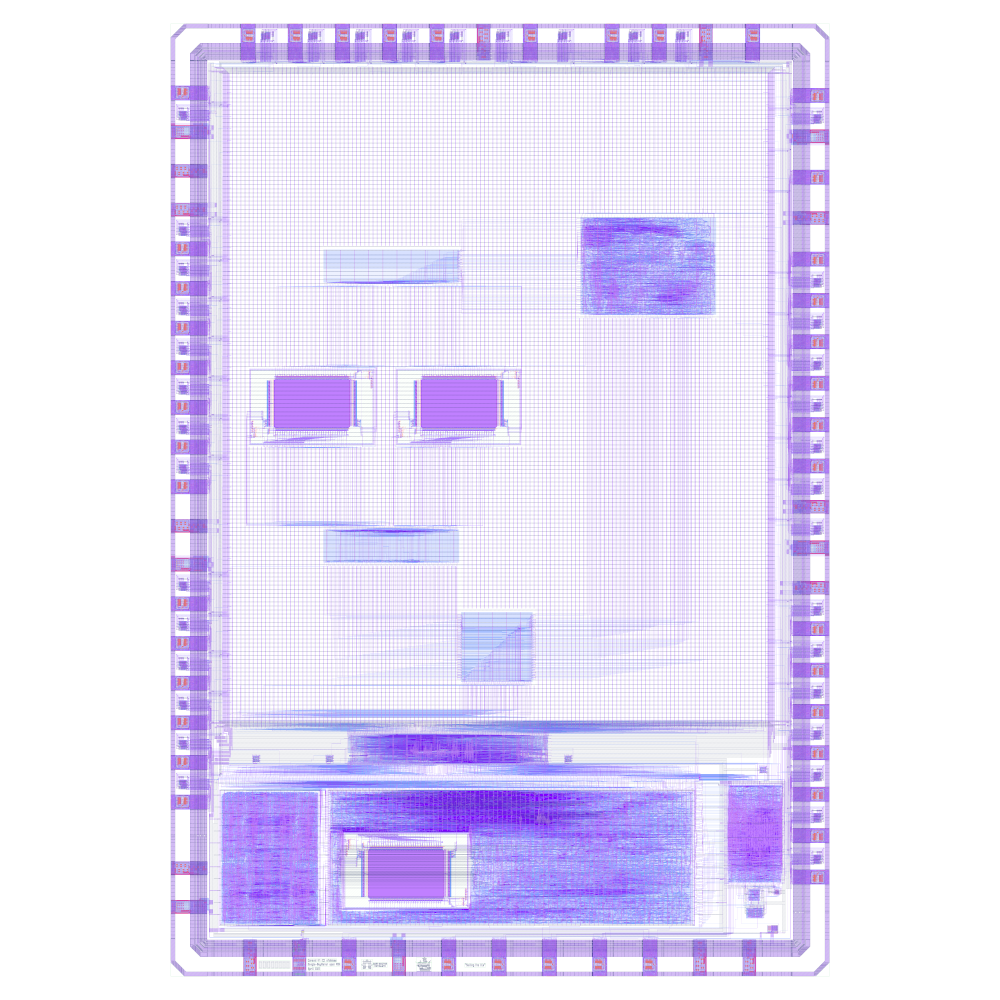

The source files for the Waveform Generator can be found under the waveform-generator repository.

The general idea is that various stimuli can be arbitrarily connected to different driver.

Currently the following blocks are implemented:

wfg_stim_sinewfg_stim_mem

wfg_drive_spiwfg_drive_pat

wfg_interconnectwfg_corewfg_subcore

The base address of the user project is 0x30000000.

By adding an offset to this base address, the various peripherals can be configured.

For more information about the register entries please refer to the waveform-generator repository.

| Offset |

Name |

Description |

| 0x10 |

CTRL |

Core control register |

| 0x14 |

CFG |

Core configuration register |

| Offset |

Name |

Description |

| 0x20 |

CTRL |

Subcore control register |

| 0x24 |

CFG |

Subcore configuration register |

| Offset |

Name |

Description |

| 0x30 |

CTRL |

Control register for interconnect |

| 0x34 |

DRIVER0 |

Driver configuration register |

| 0x38 |

DRIVER1 |

Driver configuration register |

| Offset |

Name |

Description |

| 0x40 |

CTRL |

Control register for sine wave generation unit |

| 0x44 |

INC |

Increment register |

| 0x48 |

GAIN |

Gain register |

| 0x4C |

OFFSET |

Offset register |

| Offset |

Name |

Description |

| 0x50 |

CTRL |

Control register for memory unit |

| 0x54 |

START |

Start register |

| 0x58 |

END |

End register |

| 0x5C |

CFG |

Configuration register |

| Offset |

Name |

Description |

| 0x60 |

CTRL |

Control register for SPI unit |

| 0x64 |

CFG |

SPI configuration register |

| 0x68 |

CLKCFG |

SPI clock configuration register |

| Offset |

Name |

Description |

| 0x70 |

CTRL |

Control register for pattern unit |

| 0x74 |

CFG |

Pattern configuration register |

| 0x78 |

PATSEL0 |

Low bits of PATSEL |

| 0x7C |

PATSEL1 |

High bits of PATSEL |