This repository is verilog implementation of the computer that I built using bare logic (74xx) ICs before, which was based on SAP computer design of Ben Eater, which is based on a book called Digital Computer Electronics.

| FPGA Implementation | 74xx ICs Implementation |

|---|---|

|

|

I choose to implement the verilog exactly as much as the hardware I built before which had

- 4-bit address bus (ROM only)

- 4-bit ALU which adds and has carry flags

- 4-bit general purpose registers

- 8-bit instructions upper 4-bit for op-code, lower 4-bits for

- programmable PC, which allows for a Turing complete computer

- multiple input/multiple output LUT for control unit implemented using ROMs

| Instruction | Machine Code | Description |

|---|---|---|

| NOP | 00000000 | No operation |

| LD A, aa | 0001aaaa | Load A with data "aa" |

| LD B, aa | 0010aaaa | Load B with data "aa" |

| MOV A, B | 0101xxxx | Move A to B |

| MOV A, C | 0110xxxx | Move A to C |

| MOV A, D | 0111xxxx | Move A to D |

| MOV B, A | 1000xxxx | Move B to A |

| MOV B, C | 1001xxxx | Move B to C |

| MOV B, D | 1010xxxx | Move B to D |

| ADD A | 1011xxxx | Add C and D and store the output in A |

| OUT A | 1100xxxx | Output A to the 7-segment |

| JMP aa | 1101aaaa | Jump to 4-bit address "aa" |

| JMP CN, aa | 1110aaaa | Jump to 4-bit address "aa" if ALU overflows (result was more than 15) |

| JMP NCN, aa | 1111aaaa | Jump to 4-bit address "aa" if ALU doesn't overflow |

This program demonstrates almost all instructions of the computer

- Adding

- Moving data between registers

- Jumping Conditionally (ALU flags) and Unconditionally

start:

LD B, 0

loop:

MOV B, C

LD D, 2

ADD A

OUT A

MOV A, B

MOV A, C

LD D, 8

ADD A

JMP NC, loop

JMP startI synthesized the HDL with the example program, and flashed GW1NR based FPGA Sipeed Tang Nano 9K, and connected the same LED display that shows the same thing.

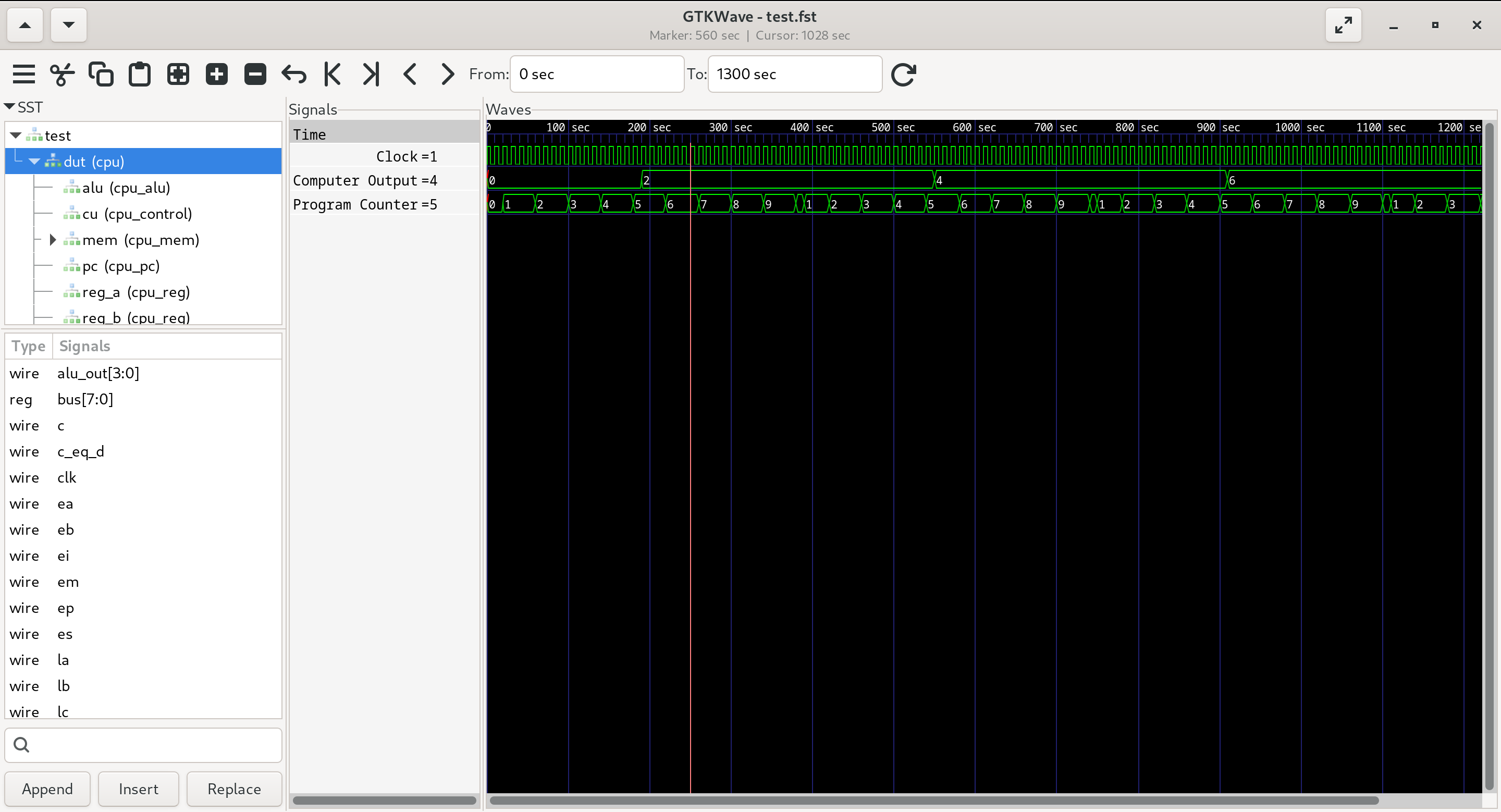

I added a small test bench that runs the computer with the example program to verify HDL.