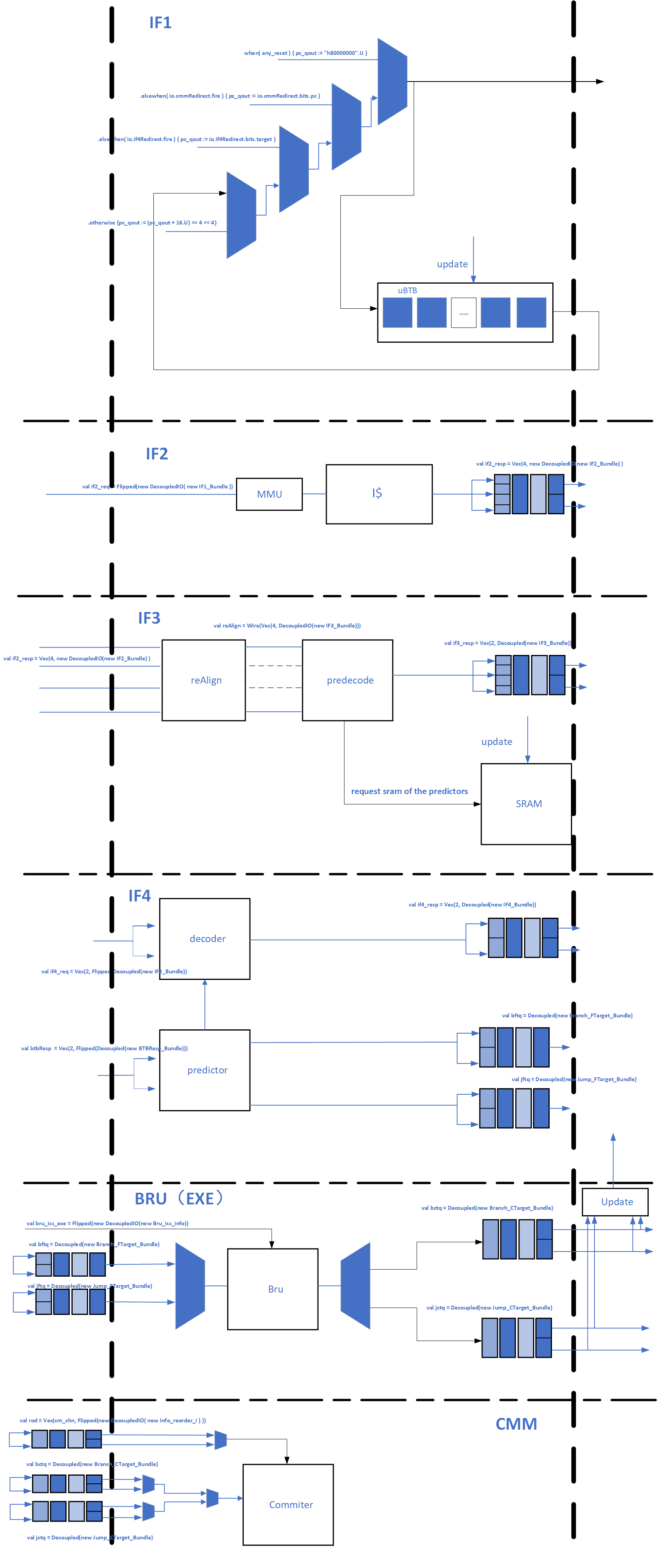

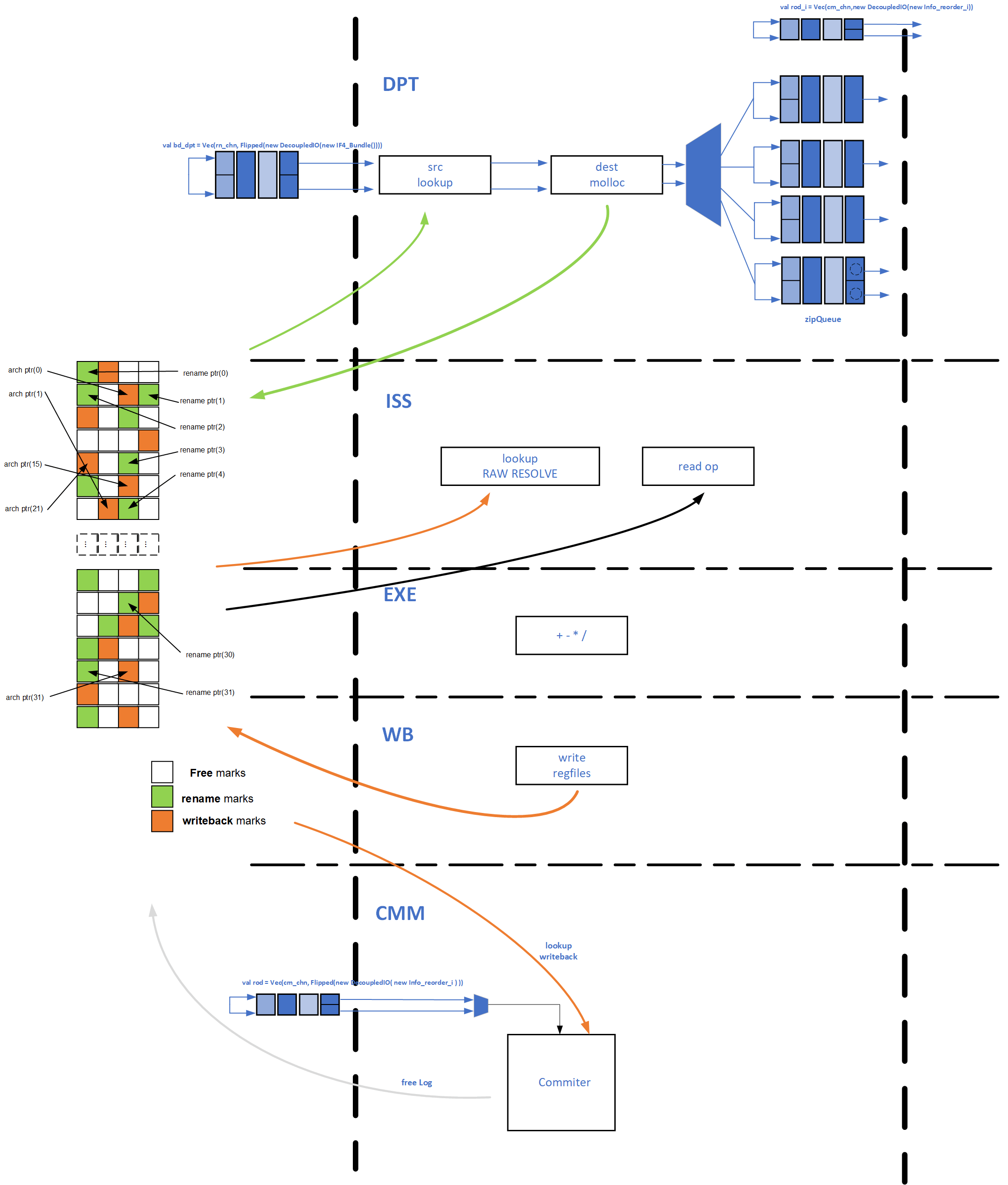

Based on Chisel3, Rift2Core is a 9-stage, N-issue(Configurable), out-of-order, 64-bits RISC-V Core, which supports RV64GC and M, S, U mode.

RiftCore is the previous version of Rift2Core in Verilog.

You can complete the deployment of the compilation and test environment following the steps below:

- Setup Repo

- Setup sbt

- Setup verilator and gtkwave

- Compile chisel3 to verilog

- Compile Model of Rif2Chip

- Test a single ISA with waveform

- Test all ISA without waveform

Also we provide a Docker-Image mainly for CI, which can also be used for compiling and testing.

Download Pre-compile Version Here, the newest status is as follows:

| Version | Test | Dhrystone | CoreMark |

|---|---|---|---|

| Rift-2300 | N/A | N/A | N/A |

| Rift-2310 | N/A | N/A | N/A |

| Rift-2320 | N/A | N/A | N/A |

| Rift-2330 |  |

|

|

| Rift-2340 |  |

|

|

| Rift-2350 |  |

|

|

| Rift-2360 |  |

|

|

| Rift-2370 |  |

|

|

| Rift-2380 |  |

|

|

| Rift-2390 |  |

|

|

Rift2Core is not only a highly configurable RISC-V CPU generator, but also provides configurable generation of submodules.

Search the provided API in the Scala Doc.

Wiki in English(Comming Soon!)