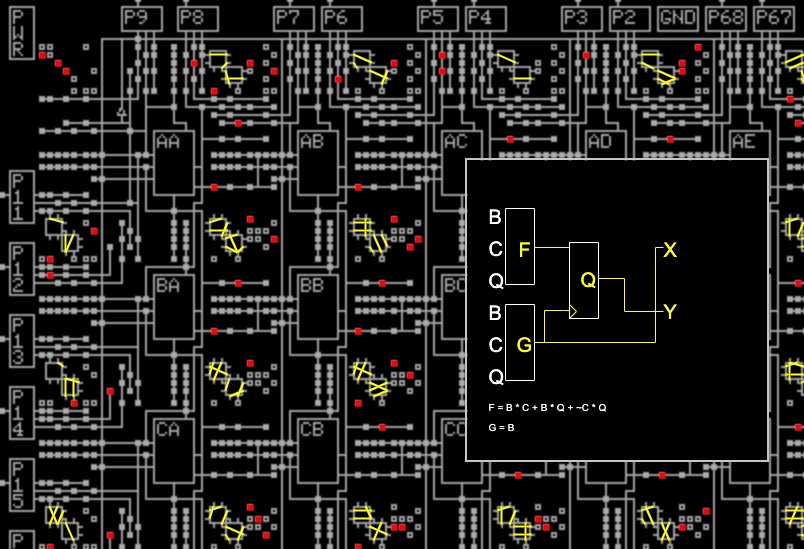

This is an in-progress project to document the internals of the XC2064 FPGA. The XC2064 was the first FPGA, introduced by Xilinx in 1985. This FPGA contained just 64 complex logic blocks (CLBs), in an 8x8 grid. It was soon followed by the XC2018, which was essentially the same chip but with 100 CLBs in a 10x10 grid.

- The files in html implement a tool to decode a raw bitstream file (RBT).

- Try it (under development) at righto.com/xc2064

Main missing features

- Need to link connections into nets

- Need to output LCA and/or Verilog

- Pads support is only partially implemented

- This is a prototype work in progress and lots of things don't work right

- My blog post Reverse-engineering the first FPGA chip, the XC2064.

- Die photos of the XC2064 and XC2018.

- XC2000 family datasheet

- XACT development system manual

- John McMaster's XC2064 project

Thanks to Geoff Body for XC2064-def.txt