This repository aims at design of 1024x32 SRAM cell array (32Kbits or 4KB) with a configuration of 1.8 V operating voltage and access time less than 2.5ns using Google SkyWater SKY130 PDKs and OpenRAM memory complier.

Static Random-Access Memory (SRAM) has become a standard element of any Application Specific Integrated Circuit (ASIC), System-On-Chip (SoC), or other micro-architectures. For this wide variety of applications, SRAMs are configured using parameters like the word-length, bit lines, operating voltage, access time, and most importantly the technology node. The access time of an SRAM cell is the time require for a read or write operation of SRAM.

Manually configuring the SRAM for every change in parameter seems a slightly in-efficient and tedious task. Due to this reason, the memory compiler is used on a large scale, as it facilitates easy configuration and optimization of memory. OpenRAM, an open-source memory compiler is used for characterization and generation of SRAM designs.

- Specifications

- Setting Up Environment

- OpenRAM Configuration For SkyWater SKY130 PDKs

- OpenRAM Compiler Output Layout

- Custom Cells for OpenRAM

- References

- Acknowledgement

- Contact Information

The specifications of a 32Kbits (32 x 1024) SRAM generated using OpenRAM compiler and SKY130 PDKs are mentioned below:

| Type | Value |

|---|---|

| WORD_SIZE | 32 |

| NUM_WORDS | 1024 |

| NUM_BANKS | 1 |

| NUM_RW_PORTS | 1 |

| NUM_R_PORTS | 0 |

| NUM_W_PORTS | 0 |

| Area (µm2) | 534277 |

| Parameter | Min | Typ | Max | Units |

|---|---|---|---|---|

| Power supply (VDD) range | 1.8 | 1.8 | 1.8 | Volts |

| Operating Temperature | 0 | 25 | 100 | Celsius |

| Operating Frequency (F) | 86 | MHz |

| Parameter | Min | Max | Units |

|---|---|---|---|

| din0[31:0] setup rising | 0.009 | 0.009 | ns |

| din0[31:0] setup falling | 0.009 | 0.009 | ns |

| din0[31:0] hold rising | 0.001 | 0.001 | ns |

| din0[31:0] hold falling | 0.001 | 0.001 | ns |

| dout0[31:0] cell rise | -1.968 | 3.437 | ns |

| dout0[31:0] cell fall | 2.922 | 3.125 | ns |

| dout0[31:0] rise transition | 0.007 | 0.027 | ns |

| dout0[31:0] fall transition | 0.007 | 0.027 | ns |

| csb0 setup rising | 0.009 | 0.009 | ns |

| csb0 setup falling | 0.009 | 0.009 | ns |

| csb0 hold rising | 0.001 | 0.001 | ns |

| csb0 hold falling | 0.001 | 0.001 | ns |

| addr0[9:0] setup rising | 0.009 | 0.009 | ns |

| addr0[9:0] setup falling | 0.009 | 0.009 | ns |

| addr0[9:0] hold rising | 0.001 | 0.001 | ns |

| addr0[9:0] hold falling | 0.001 | 0.001 | ns |

| web0 setup rising | 0.009 | 0.009 | ns |

| web0 setup falling | 0.009 | 0.009 | ns |

| web0 hold rising | 0.001 | 0.001 | ns |

| web0 hold falling | 0.001 | 0.001 | ns |

| Pins | Mode | Power | Units |

|---|---|---|---|

| !csb0 & clk0 & !web0 | Read Rising | 5.8939 | mW |

| !csb0 & clk0 & !web0 | Read Falling | 5.8939 | mW |

| !csb0 & !clk0 & web0 | Write Rising | 5.8939 | mW |

| !csb0 & !clk0 & web0 | Write Falling | 5.8939 | mW |

| csb0 | leakage | 0.033462 | mW |

This repository mentioned multiple open-source circuit schematic design, layout design, SPICE simulations tools and memory compiler. The tools used and their installation is explained in details below. All the SkyWater SKY130 PDKs related files are added to the repository, which can be used without installing the complete PDKs. In order to install or get other details of SkyWater PDKs, it can be found here.

- Python 3.5 or higher

- Python numpy (

pip3 install numpy) - Python scipy (

pip3 install scipy)

- Ngspice

- Magic

git clone https://github.com/VLSIDA/OpenRAM.git

export OPENRAM_HOME="$(pwd)/compiler"

export OPENRAM_TECH="$(pwd)/technology"

The detailed OpenRAM configuration, usage and issues for SKY130 pdk is documented in this section.

After the installation is properly done. The directory structure of OpenRAM directory looks similar to that of mentioned.

├── OpenRAM

| ├── compiler

| ├── technologies

| ├── freepdk45 (available with compiler)

| ├── scn4m_subm (available with compiler)

| ├── sky130A

The sky130A directory is not available by default. You need to create it in order to add support for SkyWater PDK Sky130. The detailed contents and their description is explained further in the document. Also, the configure sky130A directory is included in the repository for reference. It can be found at OpenRAM/sky130A/

The OpenRAM compiler is currently available for two technologies, namely - SCMOS and FreePDK45.

For adding a new technology support to OpenRAM, a directory with name of process node should be created in technology directory of OpenRAM.

The technology directory should contains following information.

├── technology

| ├── sky130A

| ├── gds_lib

| ├── sp_lib

| ├── mag_lib (optional)

| ├── models

| ├── layers.map (can be included in another sub-directory)

| ├── tech

| ├── __init__.py

| ├── tech.py

| ├── sky130A.tech

This directory contains all the custom premade library cells in .gds file format. Following files should be listed in the gds_lib directory:

- dff.gds

- sense_amp.gds

- write_driver.gds

- cell_6t.gds

- replica_cell_6t.gds

- dummy_cell_6t.gds

This directory contains all the spice netlsits of custom premade library cells in .sp file format.

This directory contains all the NMOS and PMOS models for temperatures, voltages and process corners as per requirement. This repository contains the nfet and pfet models for all process corners operating at 1.8 V.

This file contains the layer description for gds layers. It needs to be generated from the SKY130 PDK document provided by SkyWater. You can find the document here.

The layers.map should be organized in a specific syntax. Here, each layer is given on a separate line in below mentioned format:

<layer-name> <purpose-of-layer> <GDS-layer> <GDS-purpose>

The layers.map file is added to the repository and can be found here.

This directory should contains two mandatory file listed below. Any other optional scripts can also be included if required.

tech/sky130A.techtech/tech.py

This is the technology file provided by SkyWater in the SKY130 PDKs. It needs to copied to this tech directory.

The sky130A.tech technology file is added to the repository.

This python file contains all the technology related configuration. It contains information about below mentioned paramaters.

- Custom modules

- Custom cell properties

- Layer properties

- GDS file information

- Interconnect stacks : This defines the contacts and preferred directions of the metal, poly and active diffusion layers.

- Power grid

- GDS Layer Map

- Layer names for external PDKs

- DRC/LVS Rules Setup

- Technology parameter

- Spice Simulation Parameters

- Logical Effort relative values for the Handmade cells

- Technology Tool Preferences

The sample OpenRAM configurations are added to the repository. To use it, copy the sky130A directory into the technology directory of OpenRAM.

cp -rf OpenRAM/sky130A $OPENRAM_TECH/

- Sample 2: It modified technology files, mag_lib, sp_lib, gds_lib, tech.py and layers.map files.

A configuration file need to be generated in python which contains all parameters required for the compiler. Every parameter mentioned in the configuration file overrides the default value of the parameter. If a parameter is not mentioned in the file, compiler will take a default value.

A template file named myconfig_sky130.py is added in the repository. The file contains parameters as given below.

# Data word size

word_size = 32

# Number of words in the memory

num_words = 1024

# Technology to use in $OPENRAM_TECH

tech_name = "sky130A"

# You can use the technology nominal corner only

#nominal_corner_only = True

# Or you can specify particular corners

# Process corners to characterize

process_corners = ["TT"]

# Voltage corners to characterize

supply_voltages = [ 1.8 ]

# Temperature corners to characterize

# temperatures = [ 0, 25 100]

# Output directory for the results

output_path = "temp"

# Output file base name

output_name = "sram_{0}_{1}_{2}".format(word_size,num_words,tech_name)

# Disable analytical models for full characterization (WARNING: slow!)

# analytical_delay = False

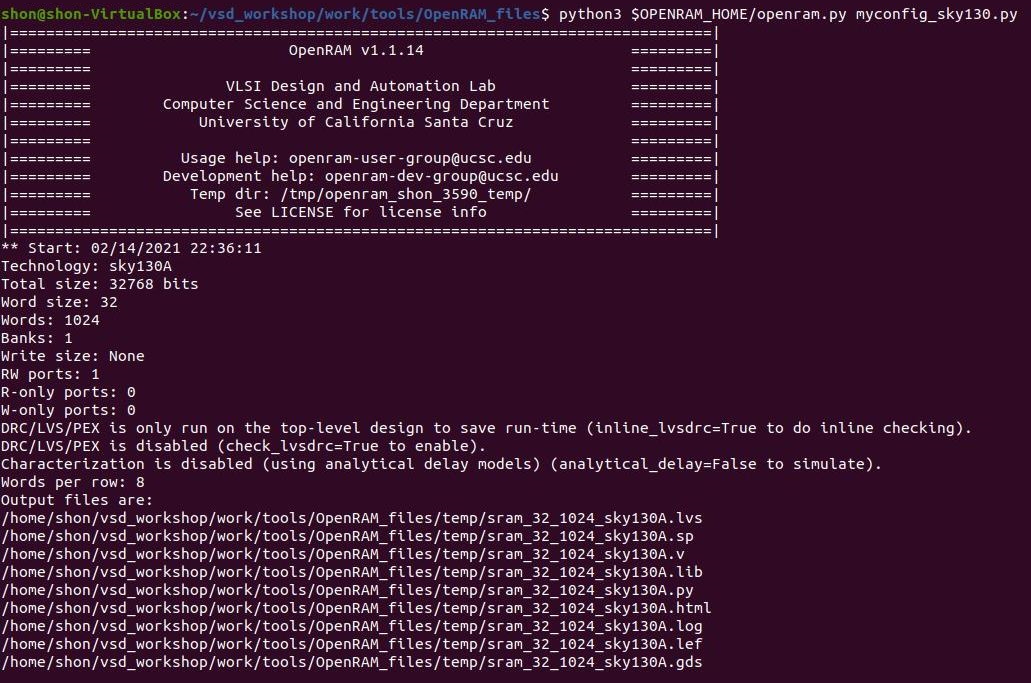

OpenRAM is invoked using the following command

python3 $OPENRAM_HOME/openram.py myconfig_sky130

or

python3 $OPENRAM_HOME/openram.py myconfig_sky130.py

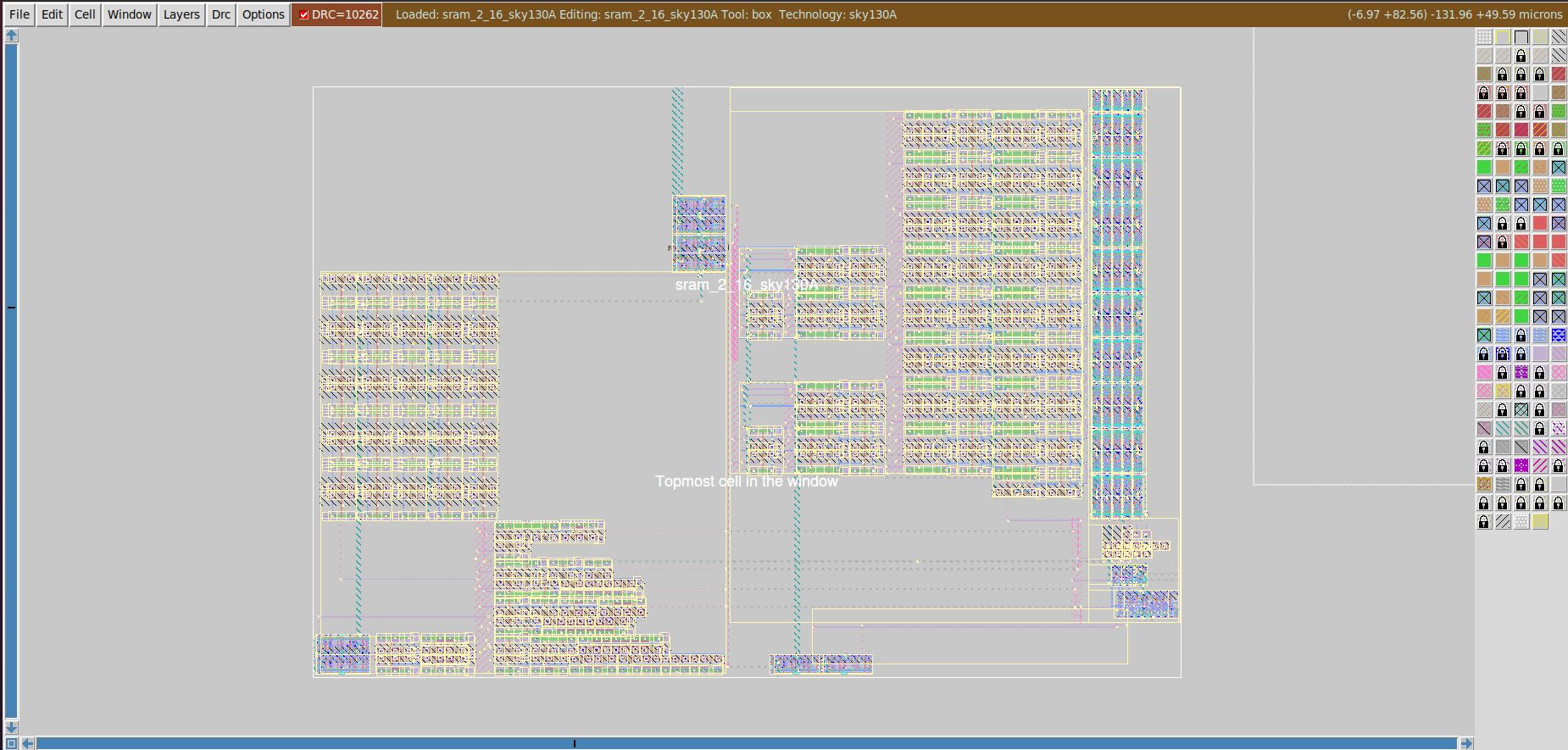

The Layout for 2 X 16 SRAM cell is show below. The detailed report can be found here

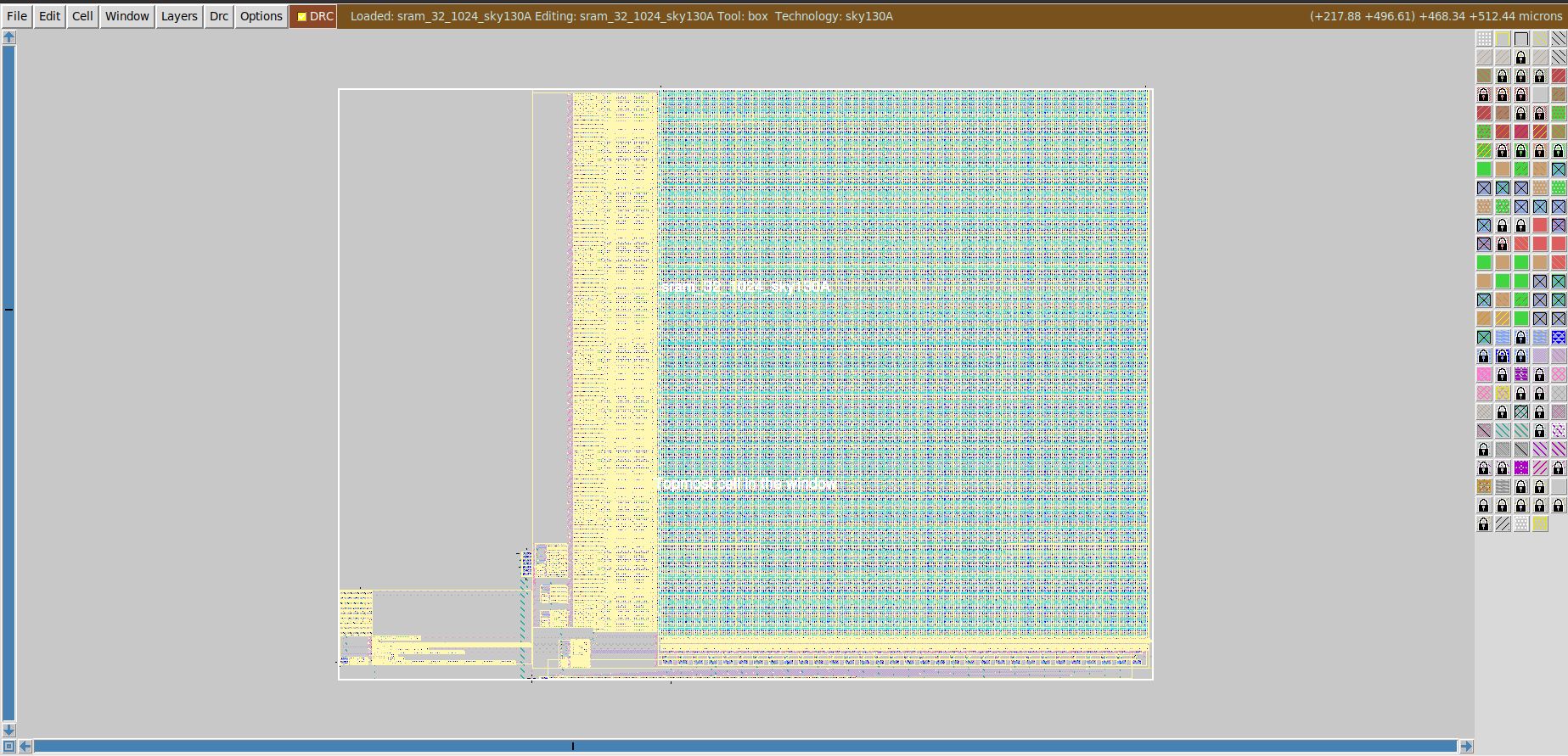

The Layout for 32 X 1024 SRAM cell is show below. The detailed report can be found here

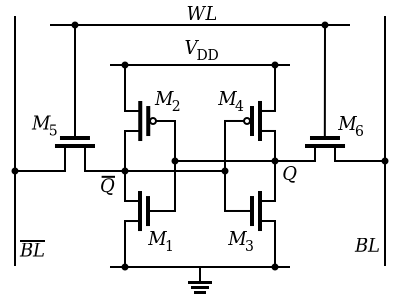

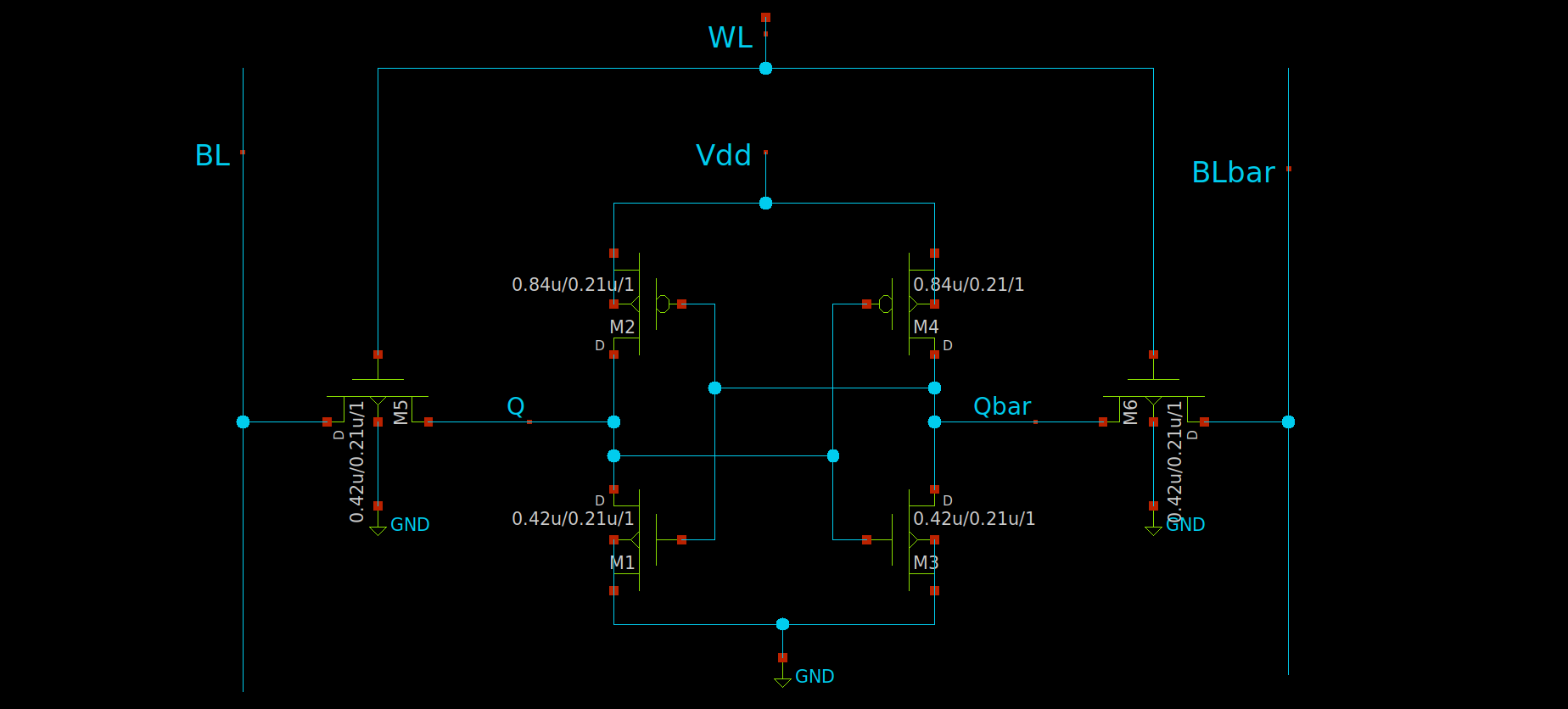

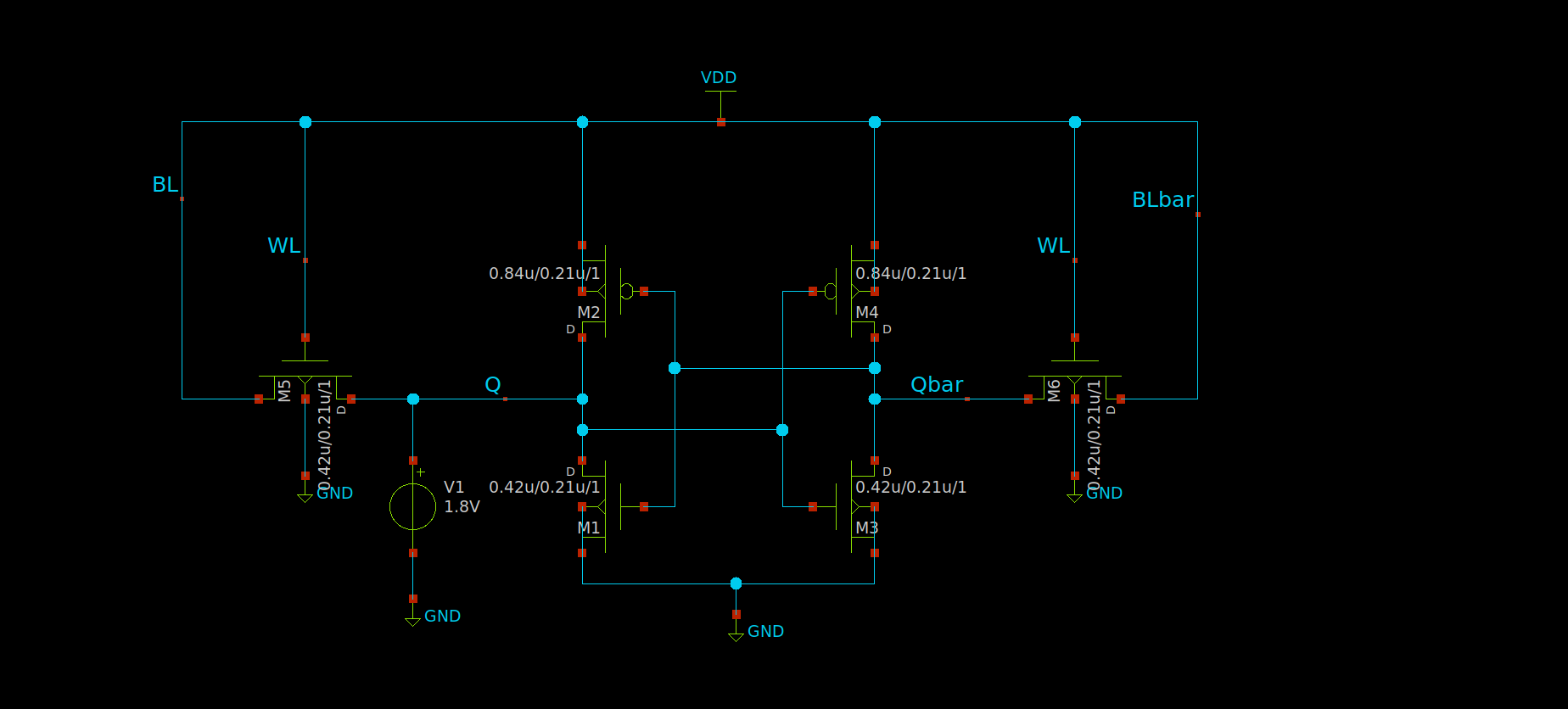

As the name says, 6T SRAM cell consists of 6 MOSFETS - 2 PMOS and 4 NMOS. It is design by cross coupling two CMOS inverters which hold the bit, and two access transistor for enabling the access to the cross coupled inverters.

The figure below shows the schematic of the generic 6T SRAM cell. Here, M1, M2 make the first inverter; M3, M4 make the second inverter and M5, M6 are the access transistors.

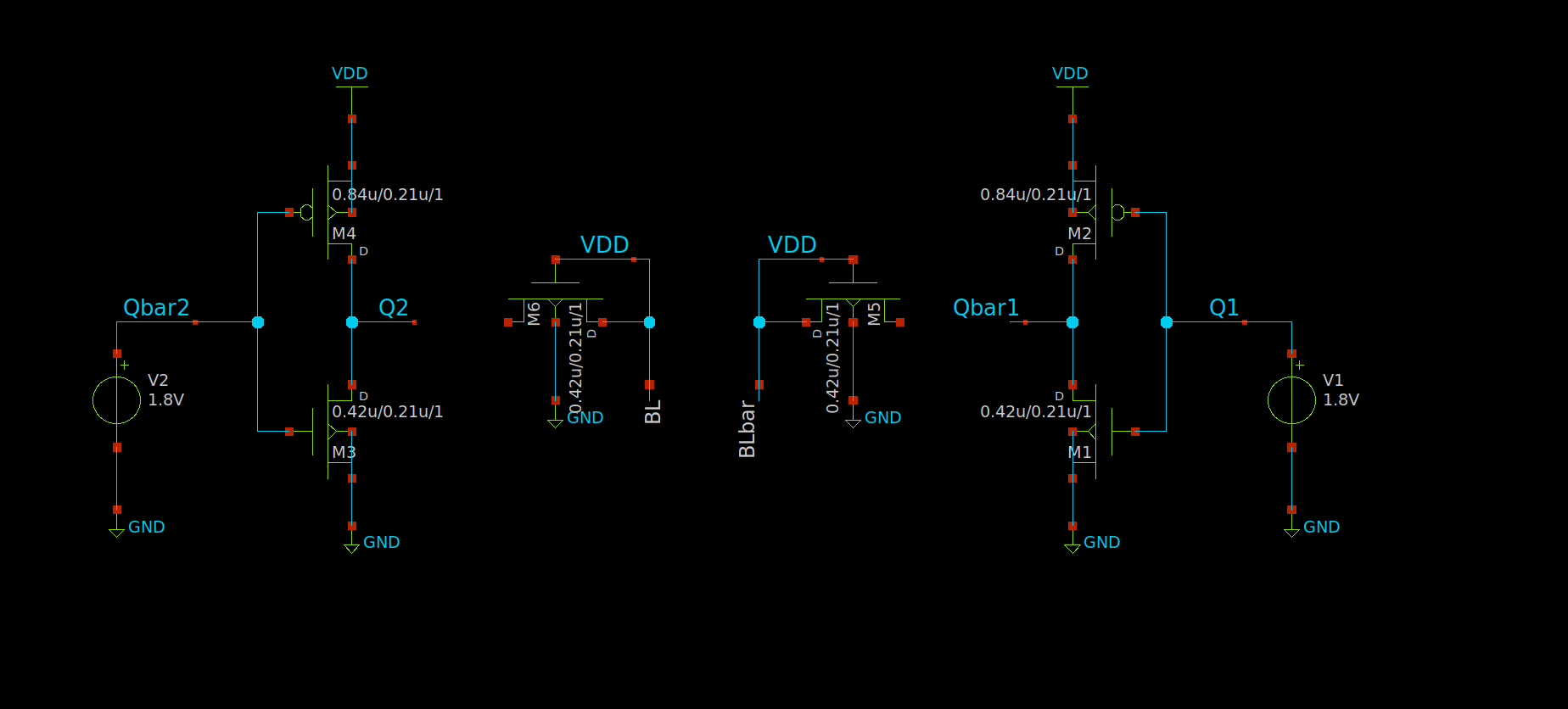

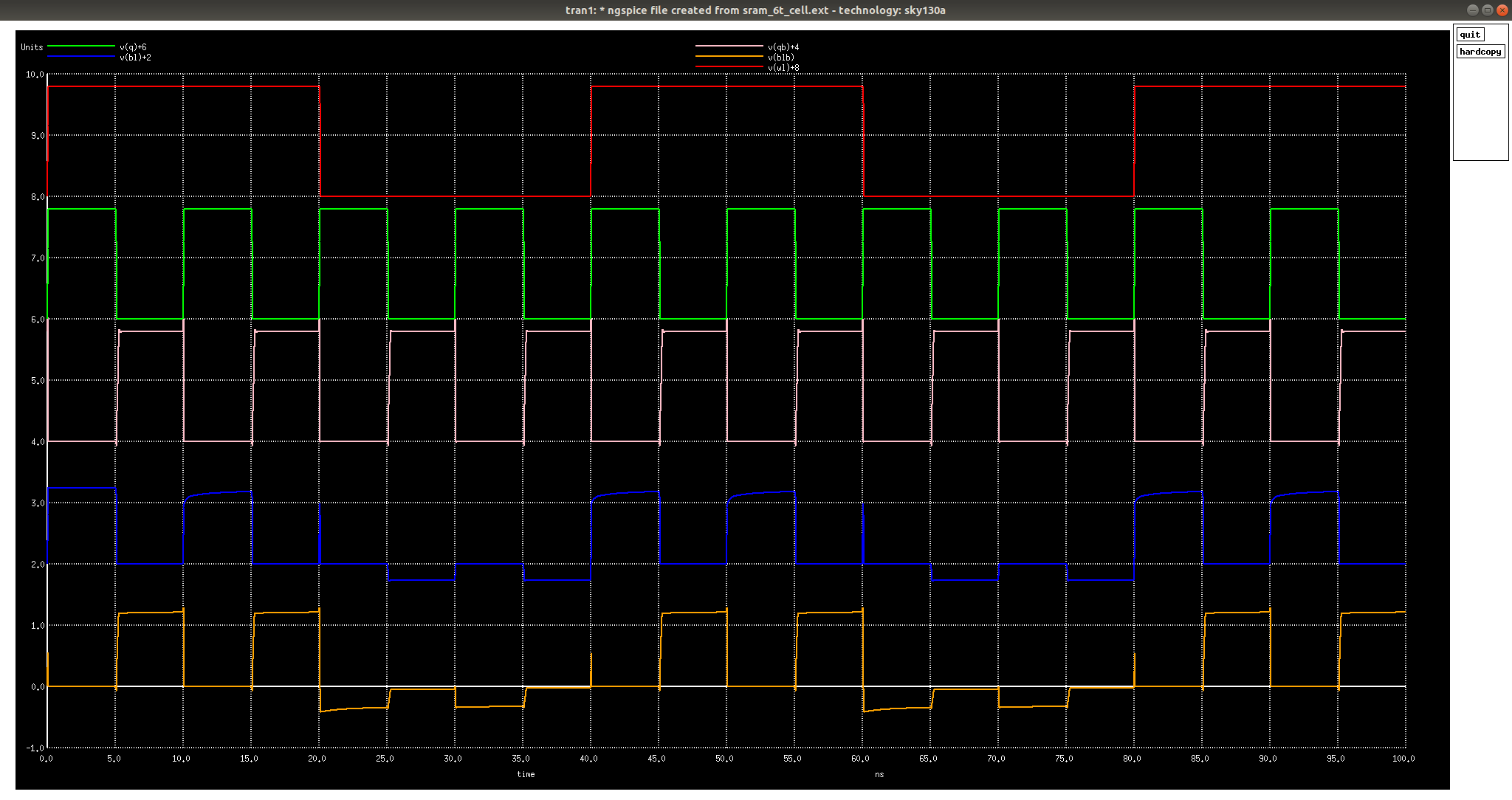

The read operation is a critical one in SRAM cell. This is becuase, before enabling the access transistors, the bit-lines are first pre-charged to high logic. Depending upon the bit store, one of the bit-line is pulled back to logic low when the access transistors are enabled.

$ ngspice Prelayout/Spice_models/SRAM_6T_Cell_read.spice

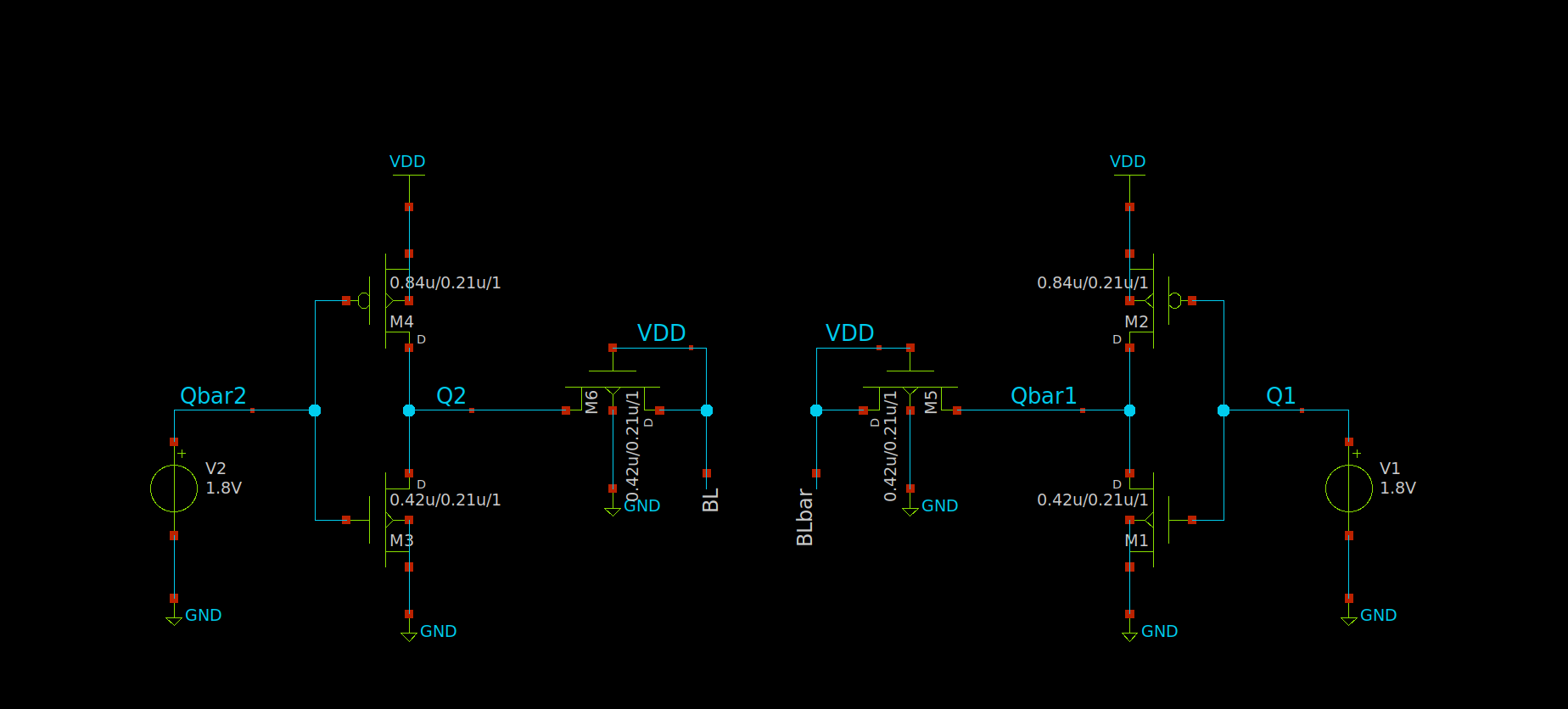

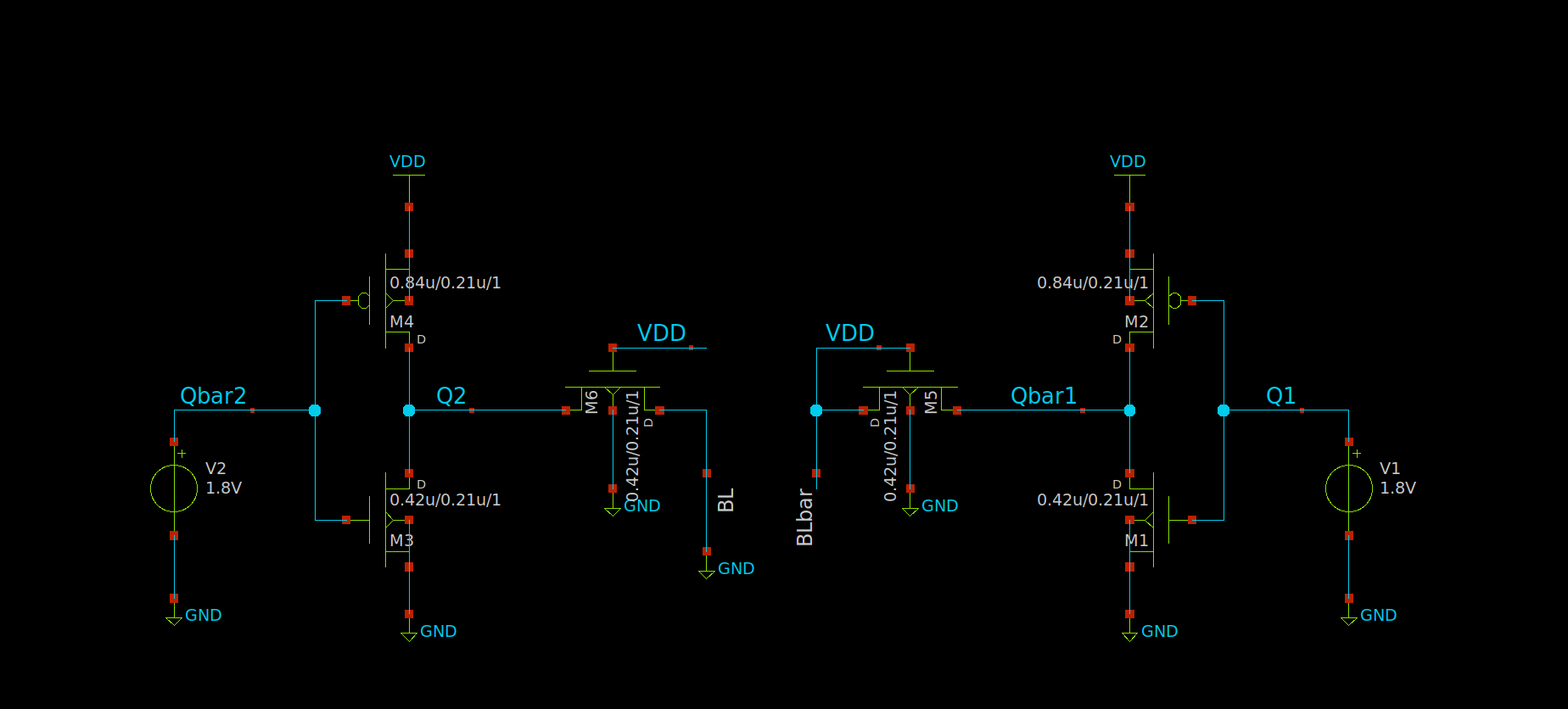

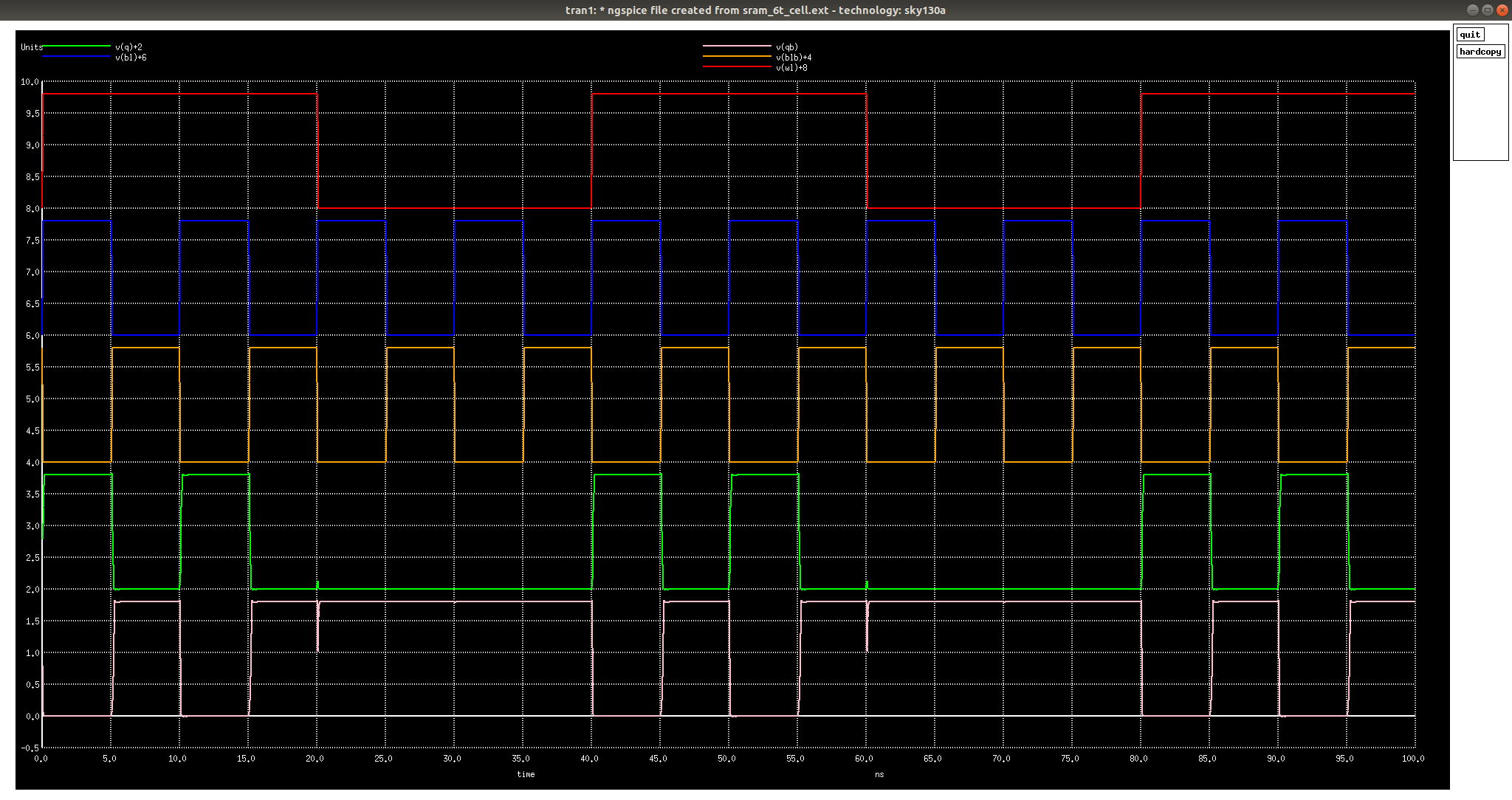

The bit to be written is first loaded to the bit-line and its inverted bit is loaded on the other bit-line. Once the access transistors are enabled the bit values on bit-lines are over-written on the inverter logic.

$ ngspice Prelayout/Spice_models/SRAM_6T_Cell_write.spice

-

Static Noise Margin

Static noise margin (SNM) is a key figure of merit for an SRAM cell. It can be extracted by nesting the largest possible square in the two voltage transfer curves (VTC) of the two CMOS inverters involved. The SNM is defined as the side-length of the square (i.e. diagonal-length), given in volts. When an external DC noise is larger than the SNM, the state of the SRAM cell can change and data is lost.

- Hold SNM

$ ngspice Prelayout/Spice_models/SRAM_Cell_hold_snm.spice

SNMlow = 1.1112 V

Hold SNM = min(SNMhigh, SNMlow) = 1.0879 V

- Read SNM

$ ngspice Prelayout/Spice_models/SRAM_Cell_read_snm.spice

SNMlow = 0.4294 V

Read SNM = min(SNMhigh, SNMlow) = 0.4294 V

- Write SNM

$ ngspice Prelayout/Spice_models/SRAM_Cell_write_snm.spice

-

N-Curve N-curve is a metric used for inline testers. It gives information for both voltage and current, and in addition it has no voltage scaling delimiter as found in SNM approach. It also has the complete information about the SRAM stability and also write ability in a single plot. N-curve can be further extended to power metrics in which both the voltage and current information are taken into consideration to provide better stability analysis of the SRAM cell.

$ ngspice Prelayout/Spice_models/SRAM_Cell_n_curve.spice-

Static Voltage Noise Margin (SVNM): It is the voltage difference between point A and B. It indicates the maximum tolerable DC noise voltage of the cell before its content changes.

SVNM = 0.5644 V -

Static Current Noise Margin (SINM): It is the additional current information provided by the N-curve, namely the peak current located between point A and B. It can also be used to characterize the cell read stability.

SINM = 122.6 uA

Note: For better read stability, SVNM and SINM must be high value.

-

Write-Trip Voltage (WTV): It is the voltage difference between point C and B. It is the voltage drop needed to flip the internal node “1” of the cell with both the bit-lines clamped to VDD.

WTV = 0.9422 V -

Write-Trip Current (WTI): It is the negative current peak between point C and B. It is the amount of current needed to write the cell when both bit-lines are kept at VDD.

WTI = -30.869 uA

-

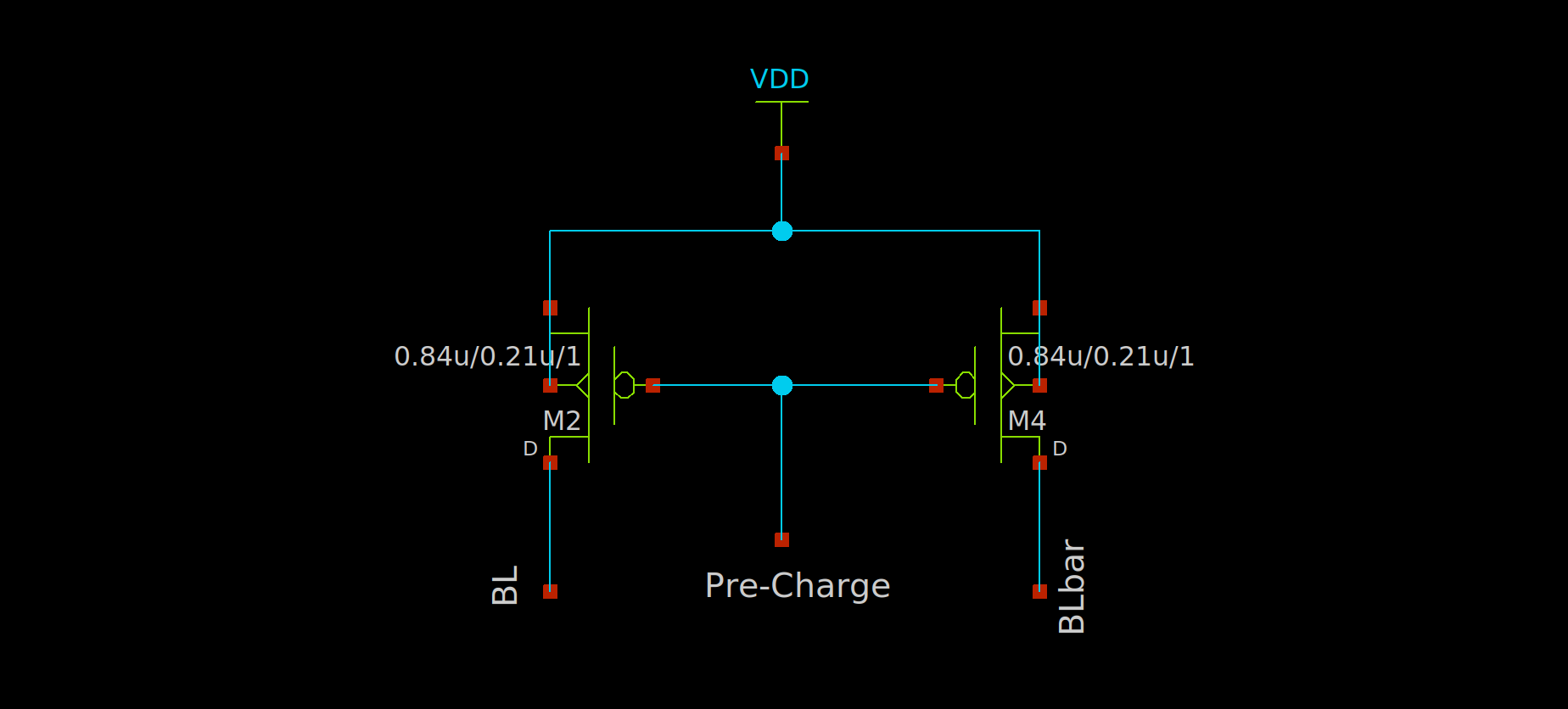

This circuit block is used to pre-charge the bit-lines to Vdd or high logic during a read operation.

Shown below is the schematic and simulation of the Pre-charge circuit.

$ ngspice Prelayout/Spice_models/precharge_circuit.spice

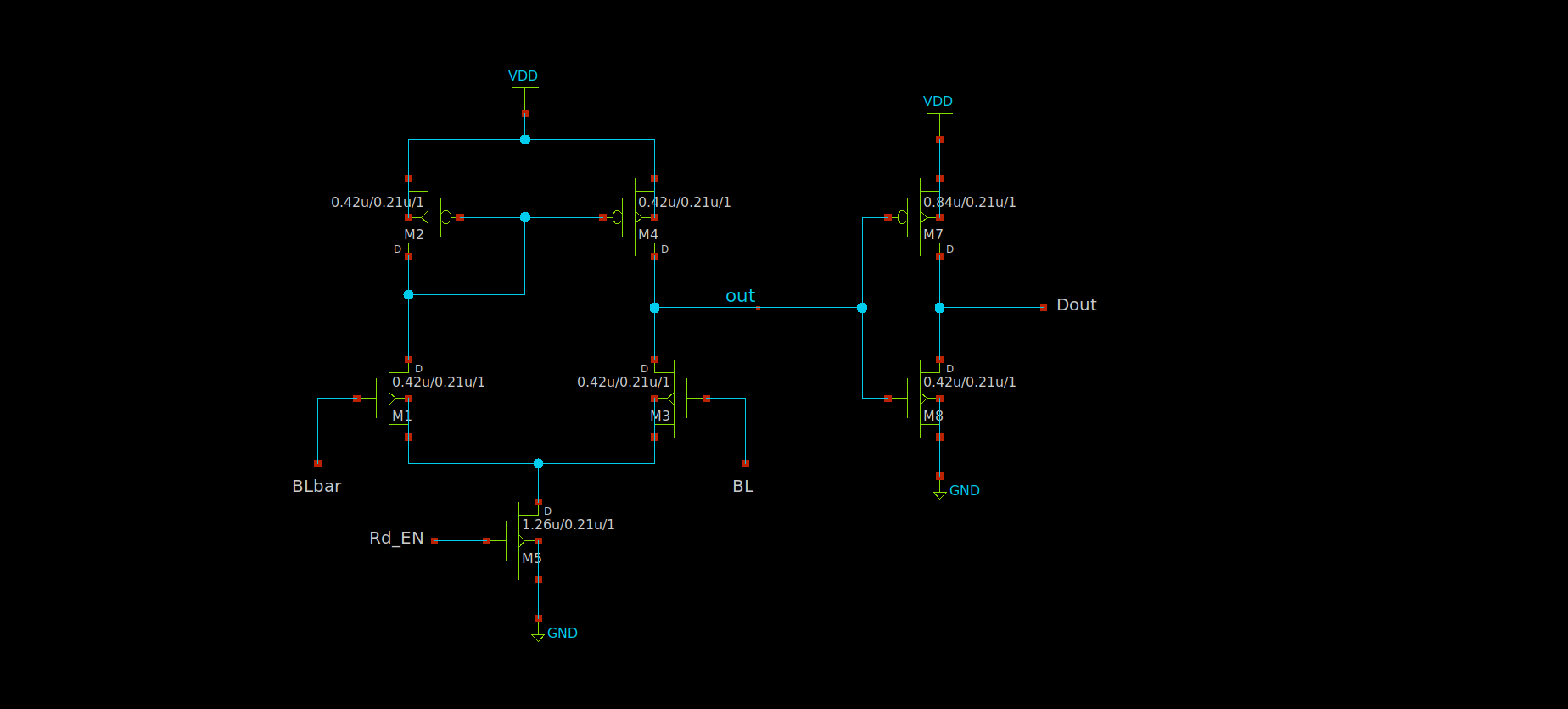

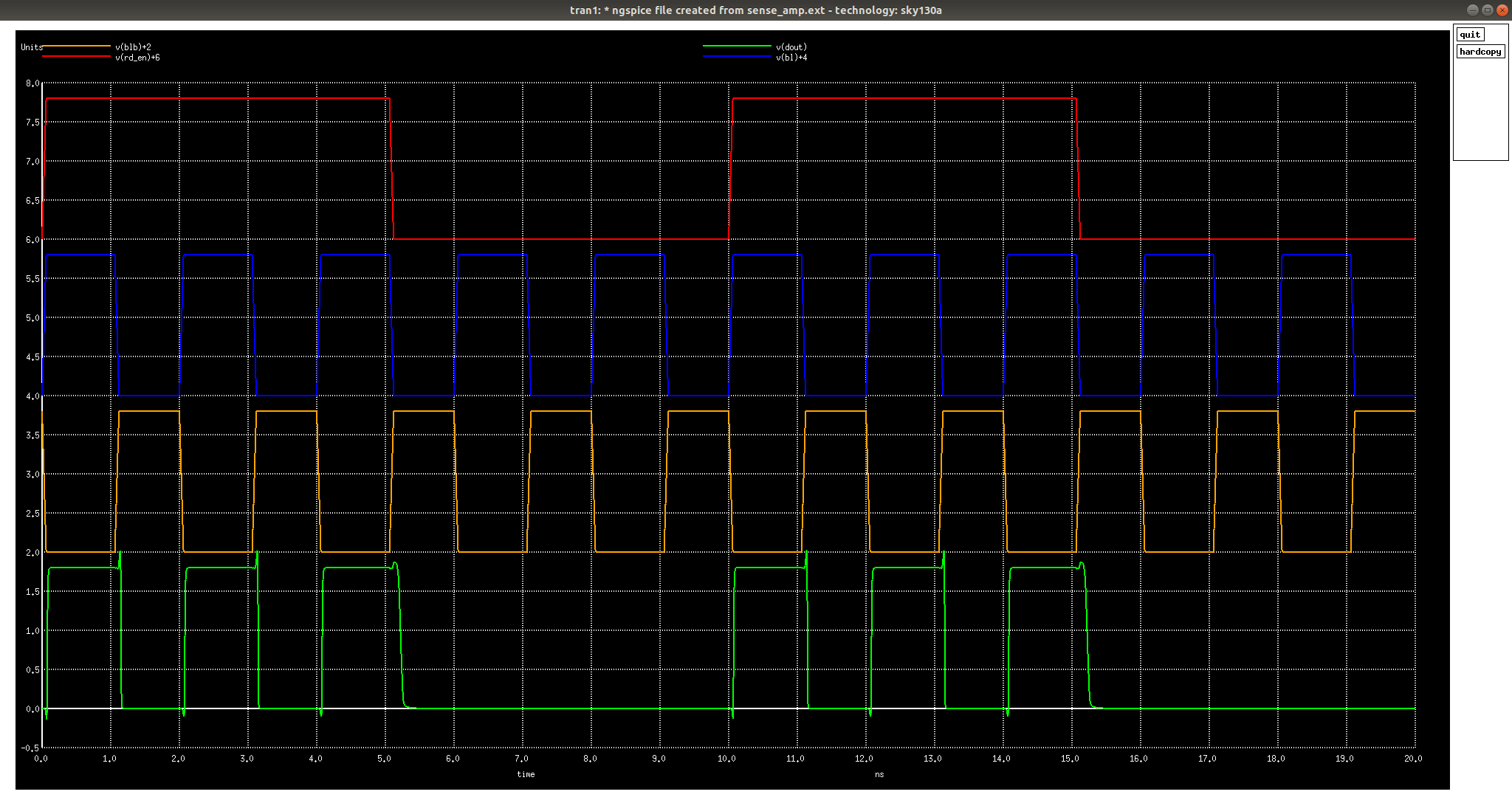

Sense Amplifiers in SRAM generally a Differential Voltage Amplifier. They form a very important part of SRAM memory as these amplifiers define the robustness of the bit-lines sensing. The function of sense amplifier is to amplify the very small analog differential voltage between the bit-lines during a read operation and provide a digital output. This effectively reduces the time required for the read operation, as each individual cell need not fully discharge the bit line.

- if bit > bit_bar, output is 1

- if bit < bit_bar, output is 0

Shown below is the schematic and simulation of a Sense Amplifier.

$ ngspice Prelayout/Spice_models/sense_amplifier.spice

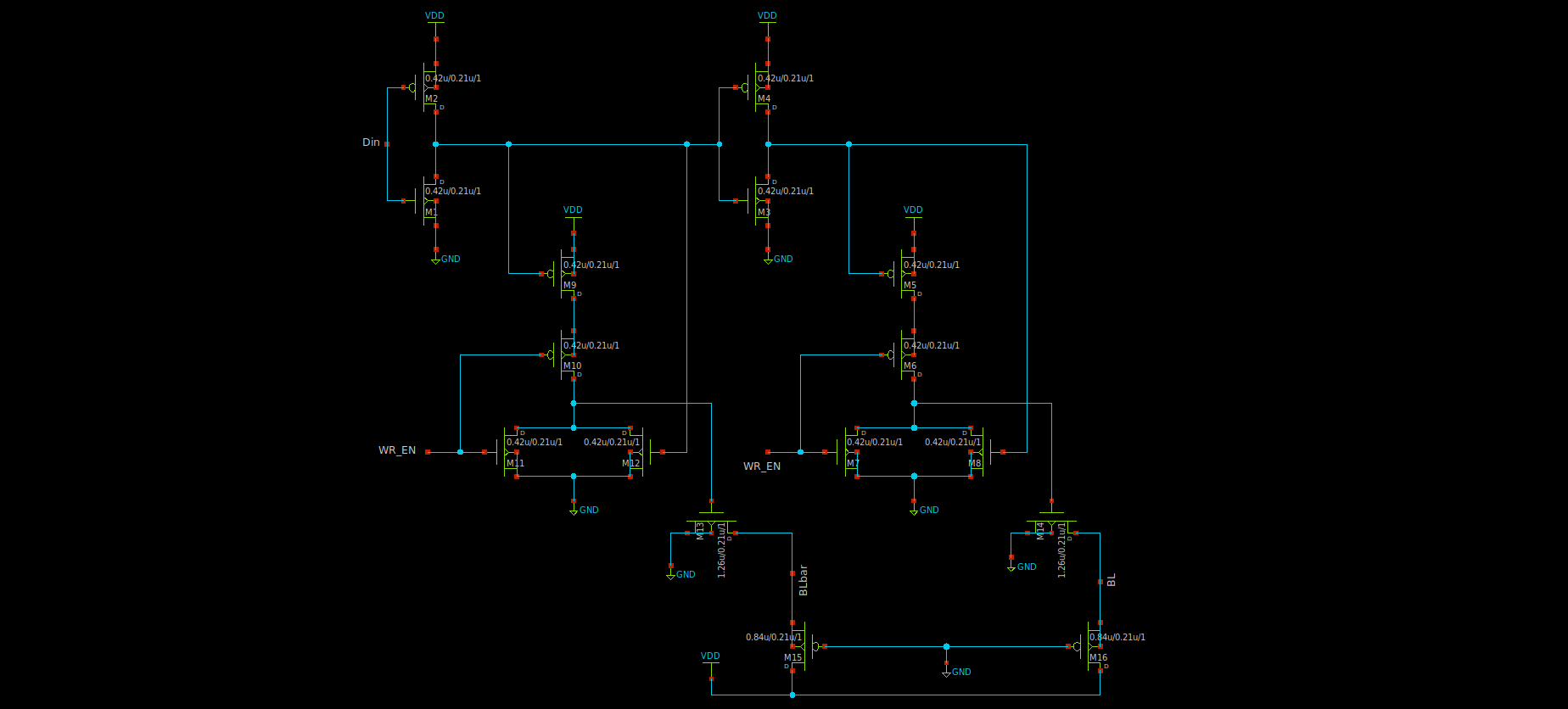

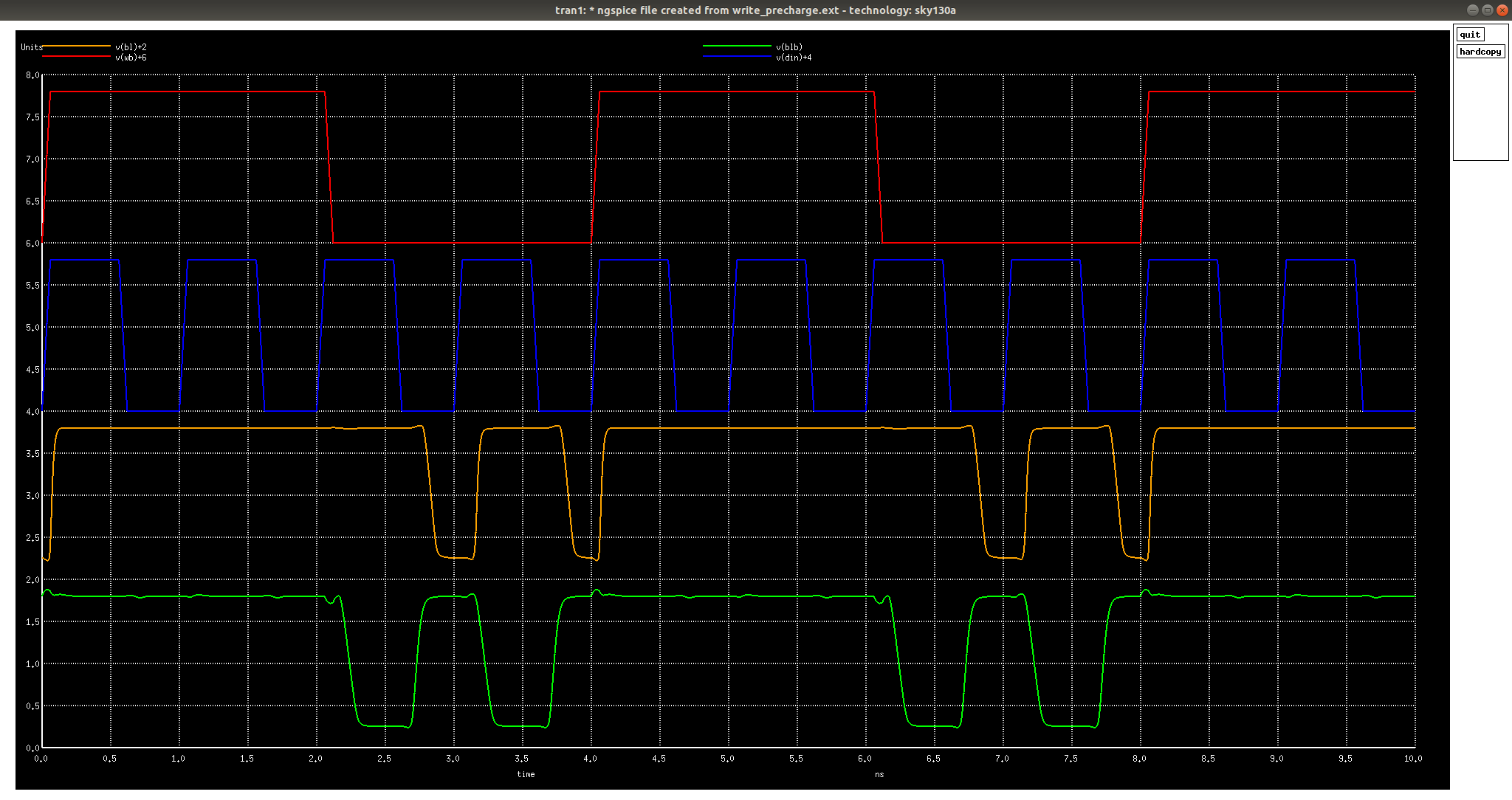

As discussed in read operation, the bit-lines are pre-charged to Vdd during the read operation. If a write operation occurs, one of the bit-lines should driven back to low logic before enabling access transistors. Write drivers are used for this purpose.

Shown below is the schematic and simulation of a Write Driver.

$ ngspice Prelayout/Spice_models/write_driver.spice

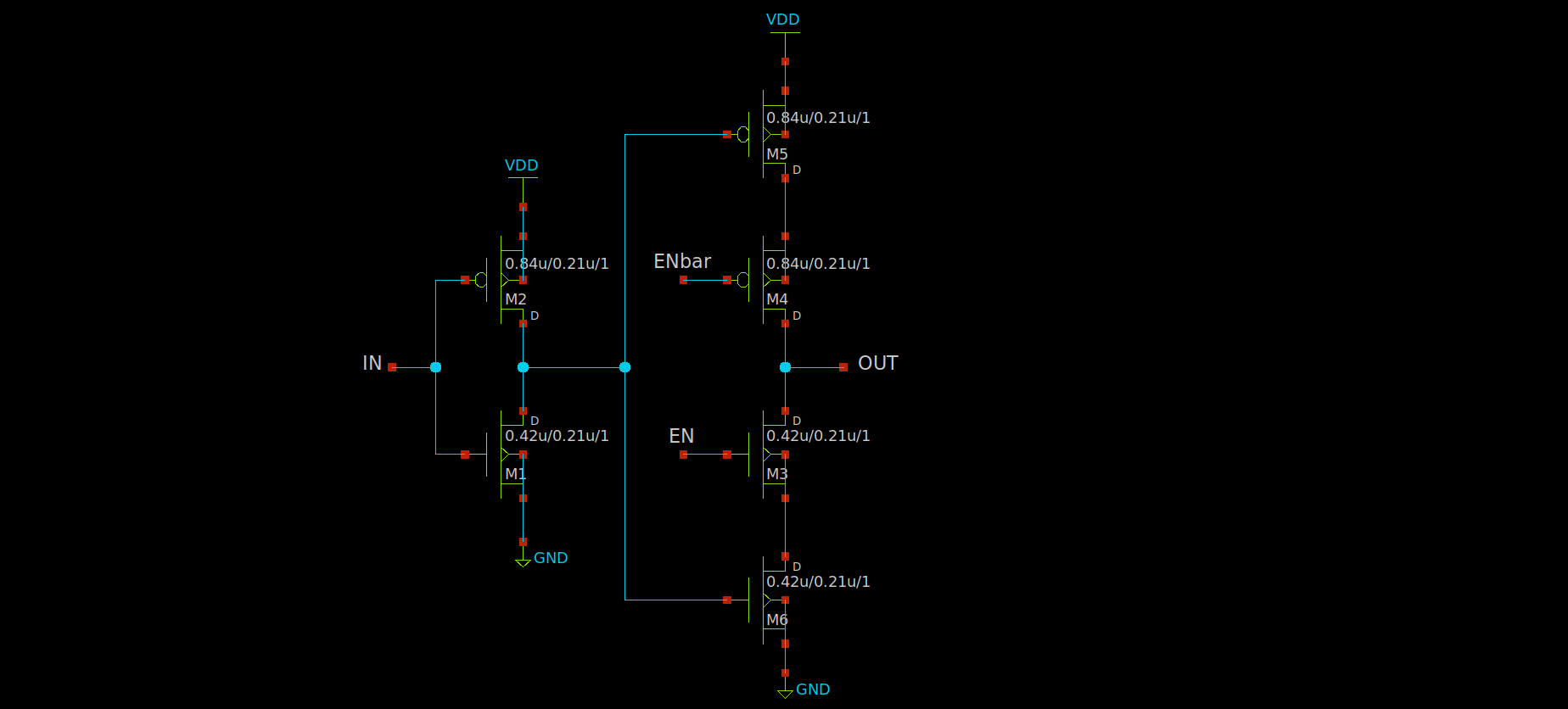

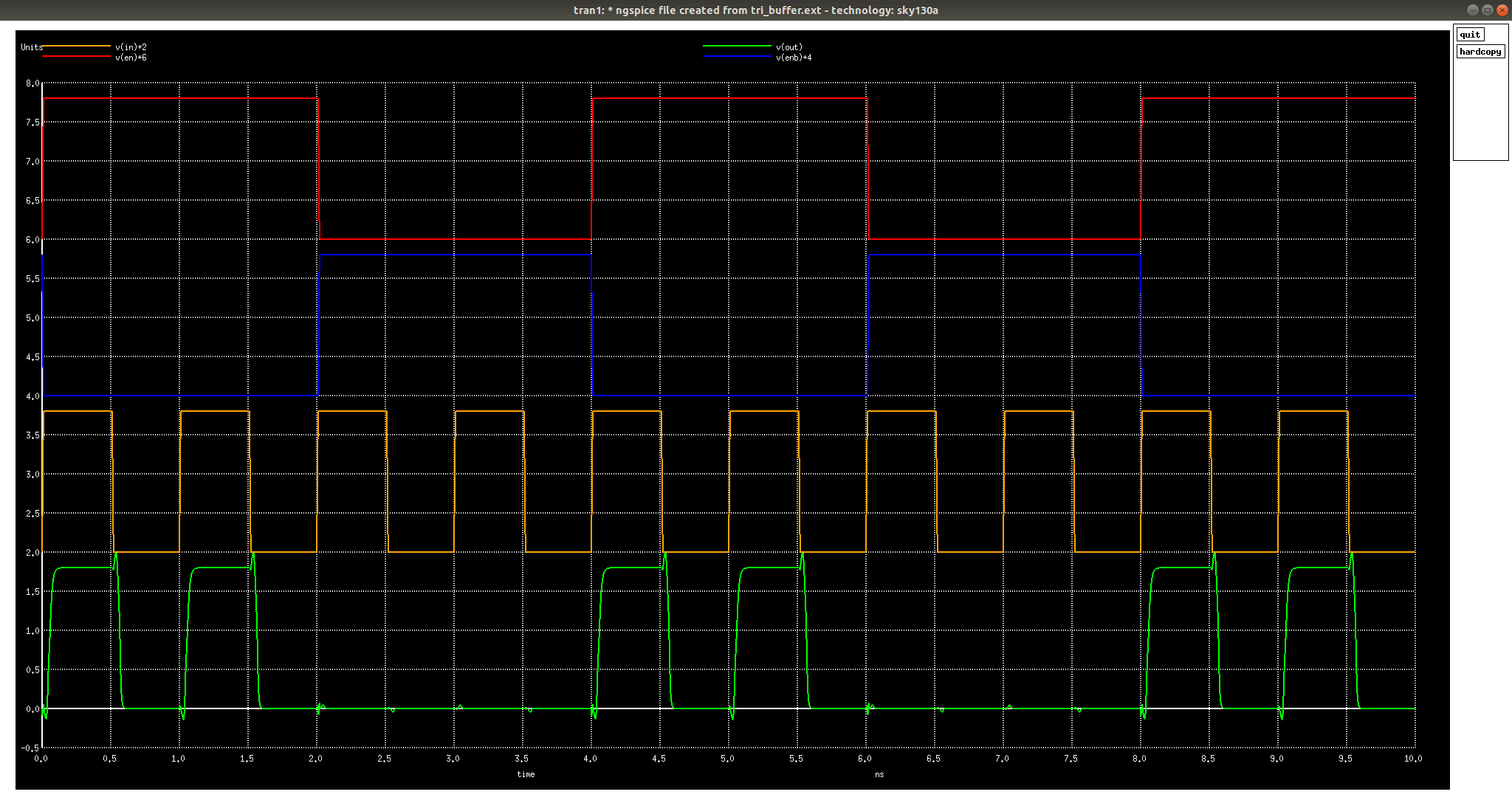

Tri-state buffer is a normal buffer with an extra enable input. Whenever, the enable input is high, tri-state buffer behaves as a normal buffer, otherwise it will either give high impedance or low logic as output.

Shown below is the schematic and simulation of a Tri-State Buffer.

$ ngspice Prelayout/Spice_models/tristate_buffer.spice

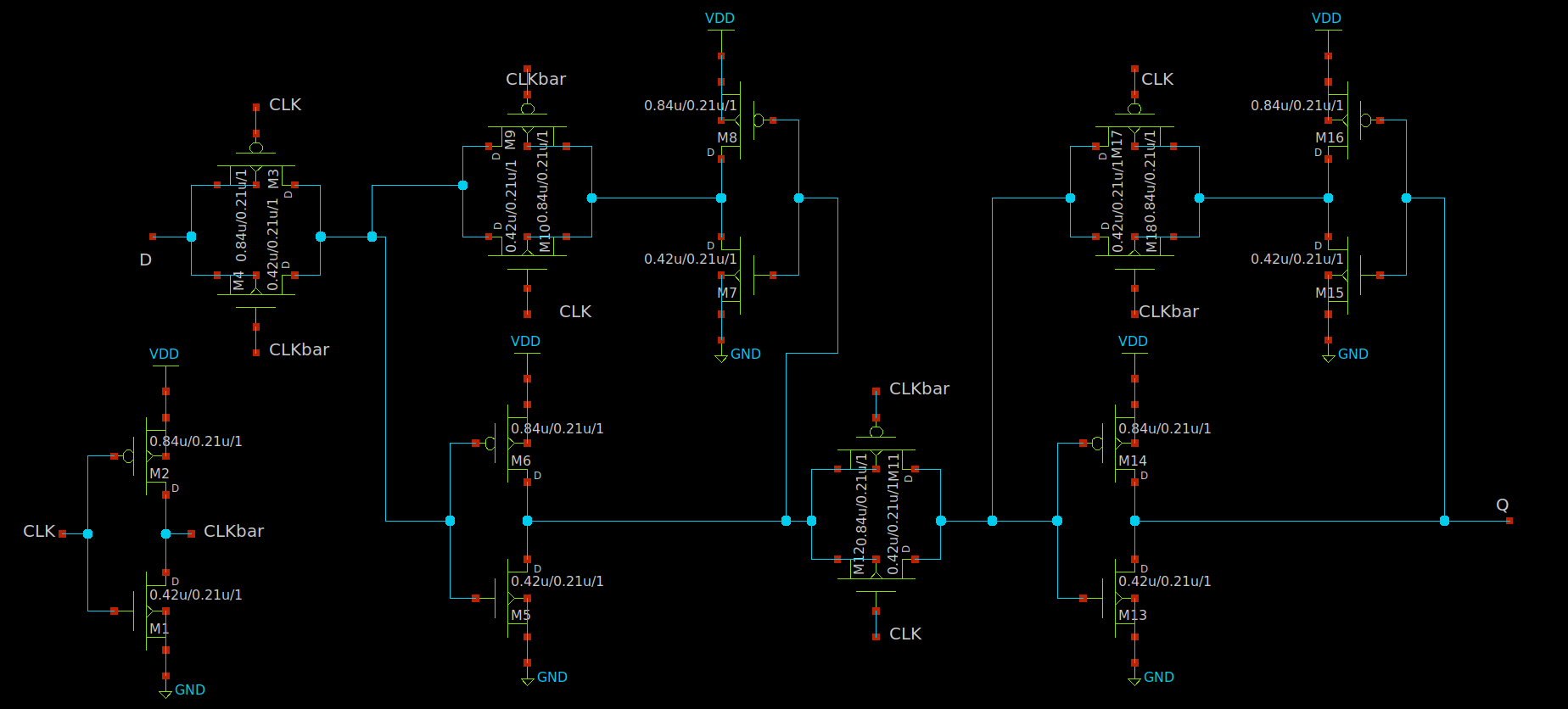

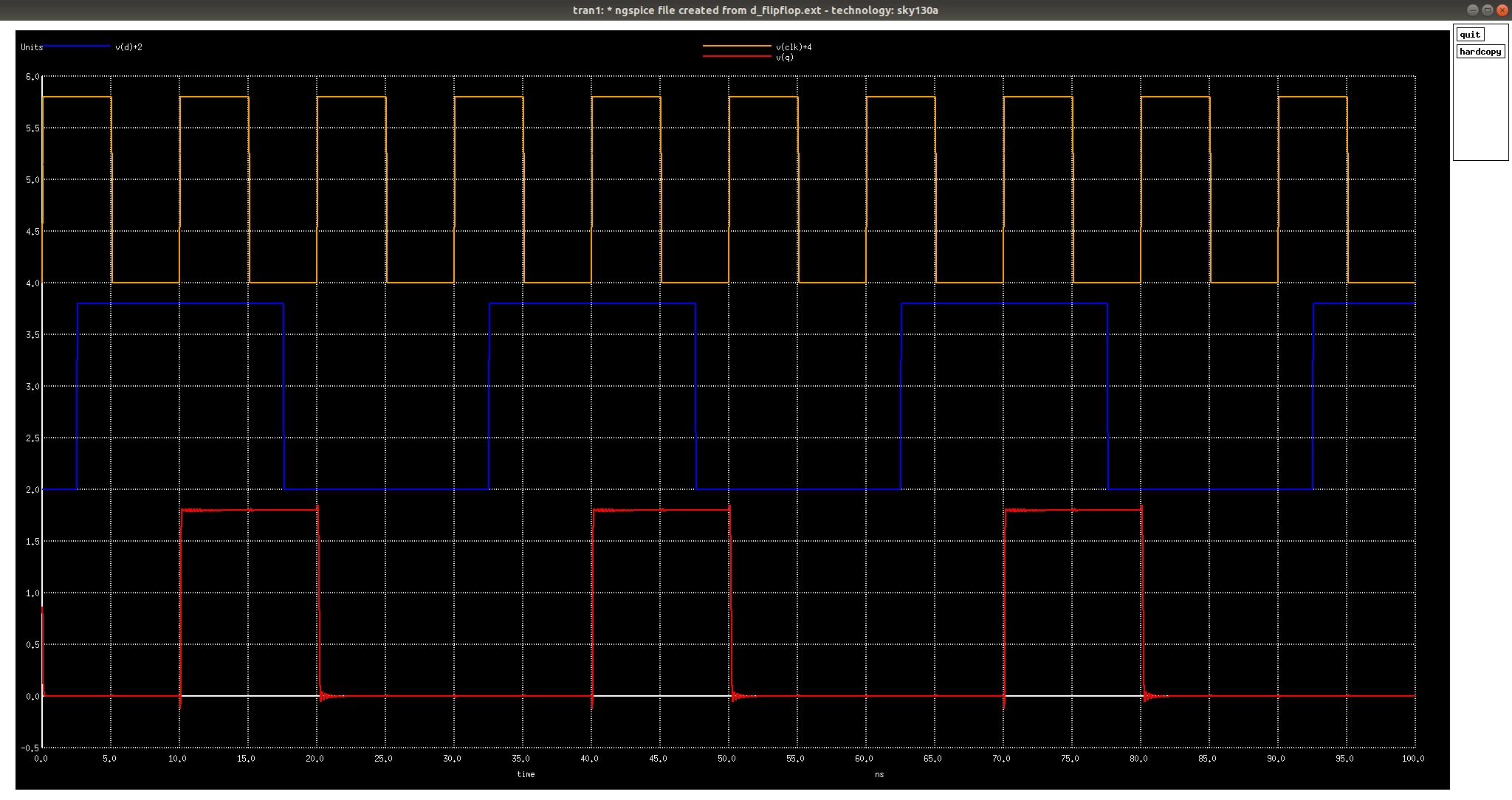

Shown below is the schematic and simulation of a Positive Edge triggered D-Flip-Flop.

$ ngspice Prelayout/Spice_models/d_ff.spice

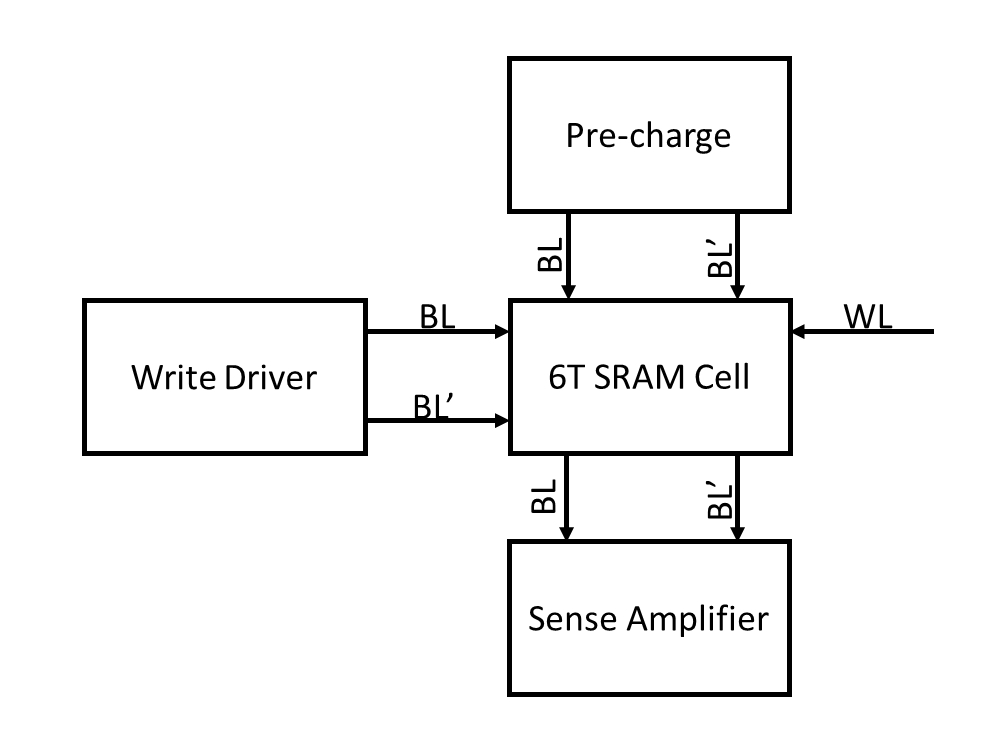

1-bit SRAM comprises of a 6T SRAM cell, a sense amplifier, a write driver and a pre-charge circuit.

-

Read Operation

$ ngspice Prelayout/Spice_models/SRAM_1bit_read.spice

-

Write Operation

$ ngspice Prelayout/Spice_models/SRAM_1bit_write.spice

Layouts are created for all custom cells in Magic EDA with sky130A.tech (Technology file), layouts are checked for DRC violations and RC extracted to a postlayout spice netlist. Extracted postlayout spice netlist is backannotated, simlulated to verify and match the response with prelayout simulations. To perform simulations, enter the following command to change present working directory to "postlayout". Follow later mentioned commands to simulate each netlist.

Layout Area: 29.70 um^2

Layout Area: 30.54 um^2

Layout Area: 84.89 um^2

Layout Area: 23.18 um^2

Layout Area: 60.25 um^2

- VLSI System Design: https://www.vlsisystemdesign.com/

- Efabless OpenLANE: https://github.com/efabless/openlane

- OpenRAM: https://vlsida.github.io/OpenRAM/

- M. Guthaus et al., “OpenRAM: An open-source memory compiler,” 2016 IEEE/ACM International Conference on Computer-Aided Design(ICCAD), Austin, TX, 2016, pp. 1-6.

- Nickson Jose: Standard cell design and characterization using openlane flow

- Kunal Ghosh, Co-founder, VSD Corp. Pvt. Ltd.

- Matthew R. Guthaus, University of California, Santa Cruz.

- Pradeepkumar S K, Assistant Professor, Electronics and Communication Engineering, Kalpataru Institute of Technology, Tiptur, Karnataka.

- Shon Taware, M.Tech. Embedded Systems and VLSI Design

- Kunal Ghosh, Co-founder, VSD Corp. Pvt. Ltd.