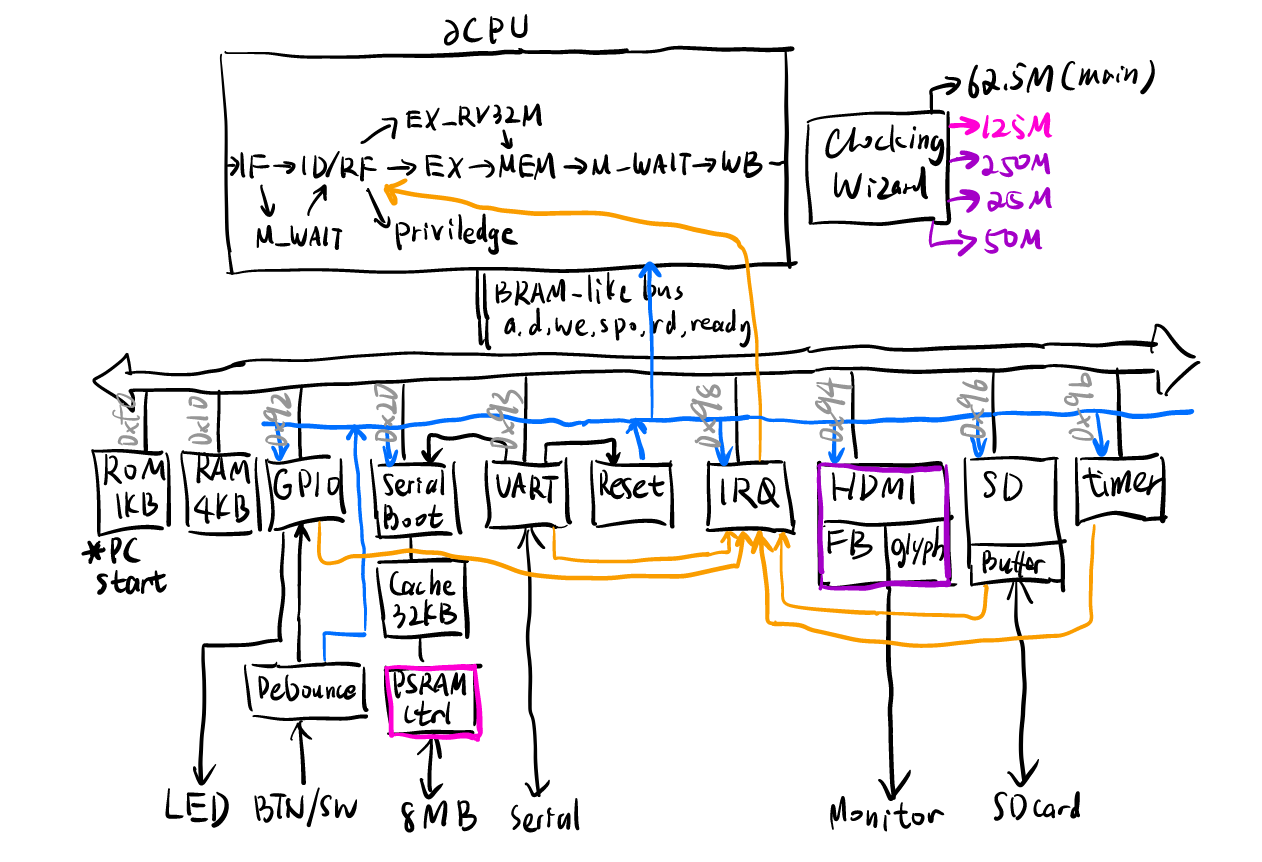

Crappy RISC-V CPU and fancy peripherals designed to be useful. No-MMU Linux capable. Free-software toolchain ready. Prioritize compatibility and easy-to-understand -- if I can write this, you also can.

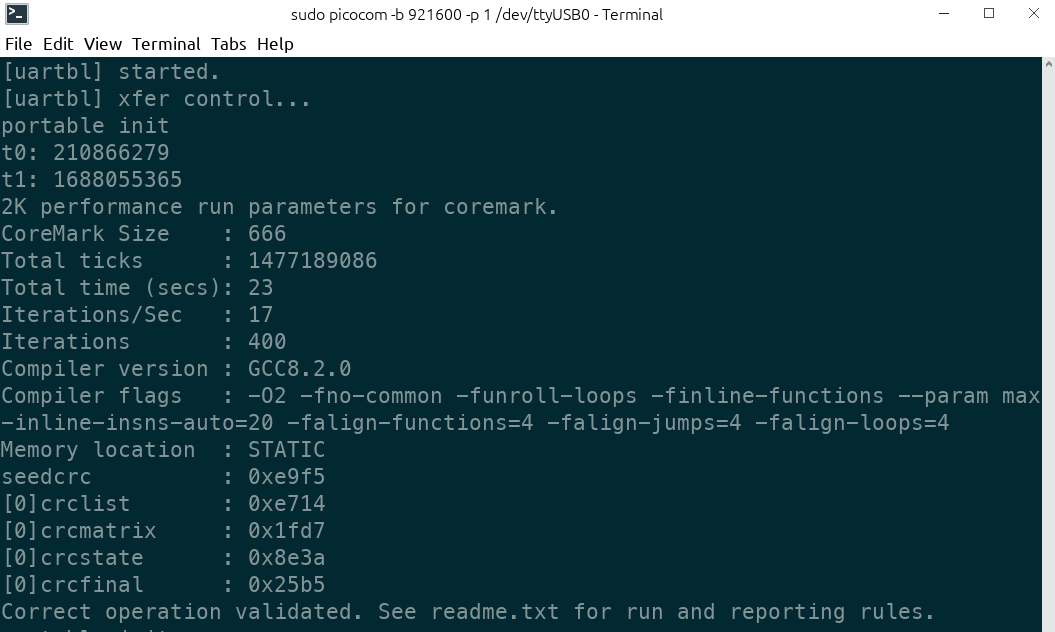

- Multiple-cycle RISC-V RV32IMA* Zicsr* @ 62.5 MHz, ~0.27 CoreMark/MHz

- M-mode, interrupt, exception*

- Core local interrupt controller(CLINT, for mtime and

softwareinterrupt) - Platform-level interrupt controller(PLIC, for external interrupt)

- Core local interrupt controller(CLINT, for mtime and

- U-mode*

- Memory-mapped IO bus

- with arbitration and DMA

- Cache, direct mapping(configurable, 32 KB default)

*: except amo(max|min)u?

*: may not be exactly standard, stuffs like vectored interrupt not supported

*: stuffs like illegal instruction not supported

*: only MPP field in mstatus, which is enough

Future plan

- Illegal instruction/load/store exception

- Bus arbitrationDMA

- DMA

- Optimize memory access cycles

- U-mode memory protection (like PMP?)

- Sv32 MMU

- S-mode

- GDB debug over openocd JTAG

- faster M instructions

- amo(max|min)u? (Linux doesn't use, not planned)

- IO bus w/ burst (hard, not planned)

- PMP (not planned)

- Formal verification (not planned)

- Pipeline (not planned)

- AXI MIG DDR2/DDR3

- ESP-PSRAM64H (8 MB) QPI mode @ 62.5 M, burst R/W

- SDRAM

- GPIO (LEDs, buttons, switches)

- UART (115200/921600/1843200 baud), boot from UART, rest from UART

- SD card (SPI mode, SDHC)

- PS/2 keyboard

- PS/2 mouse

- Graphics

- HDMI, character terminal, frame buffer graphics(320x240 8-bit color, 640x480 2-bit monochrome)

- Quality of life fixes

- Old good VGA

- ILI9486 480x320 LCD

- Refresh rate upgrade

- HDMI, character terminal, frame buffer graphics(320x240 8-bit color, 640x480 2-bit monochrome)

- CH375 USB disk

- W5500 ethernet module

- W5500 as MAC with LwIP stack

- Bus converter: Use AXI peripherals

- Hart transplant: Use other RISC-V cores with my peripherals

- Xeno transplant: Use ARM or x86 cores with my peripherals

Future plan

- Internet connectivity

- LAN8720 module w/ RGMII PHY (need FPGA MAC)

- ESP8266/ESP32 Wifi module (Boring and assaulting)

- ENC28J60

- LwIP stack

- USB capability

- Host controller, like SL811

- USB3300/TUSB1210 ULPI PHY (need FPGA host)

- Driver for classes(HID, HUB, Mass Storage)

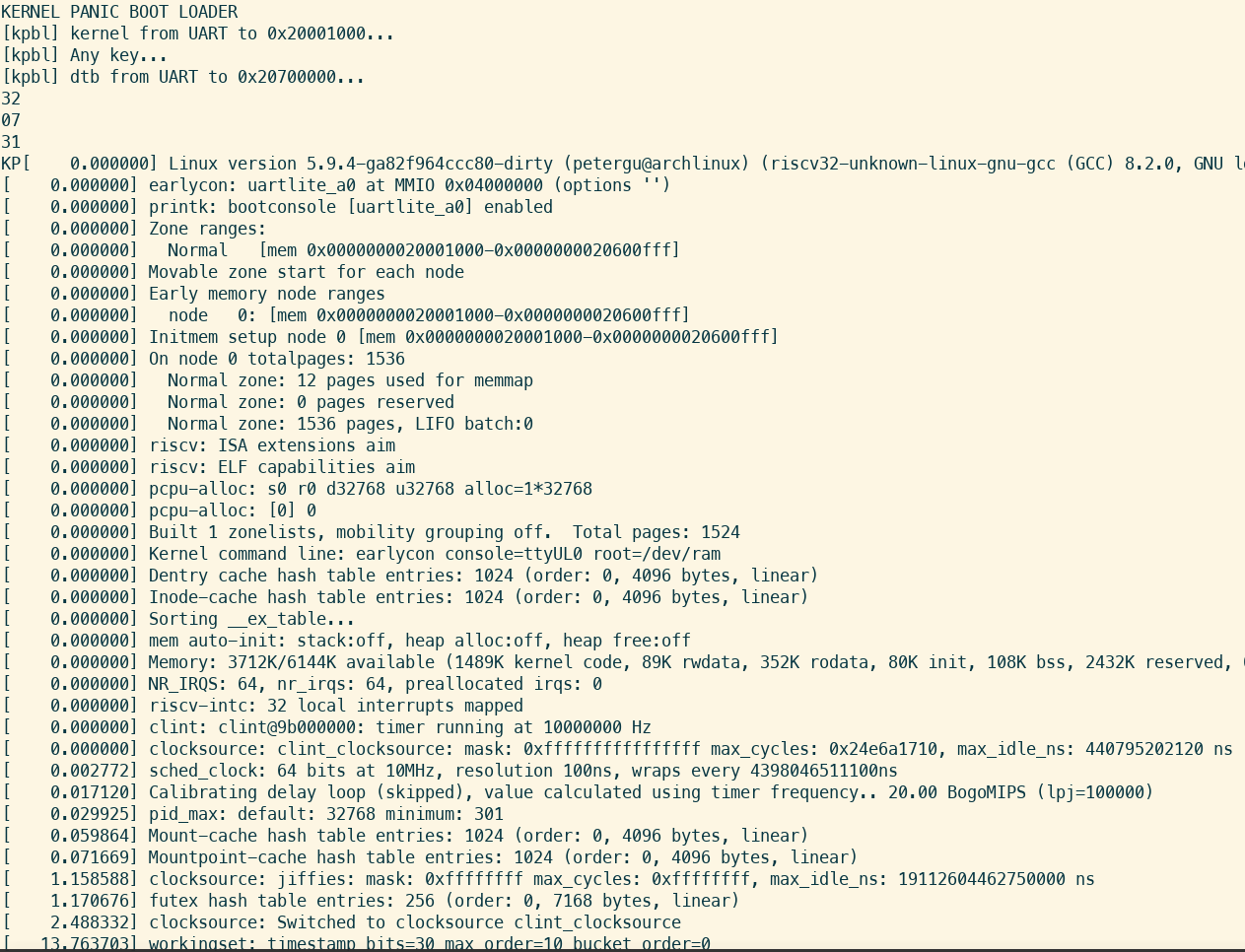

- Linux kernel 32-bit No-MMU uClibc

- busybox userspace

- driver for my UART

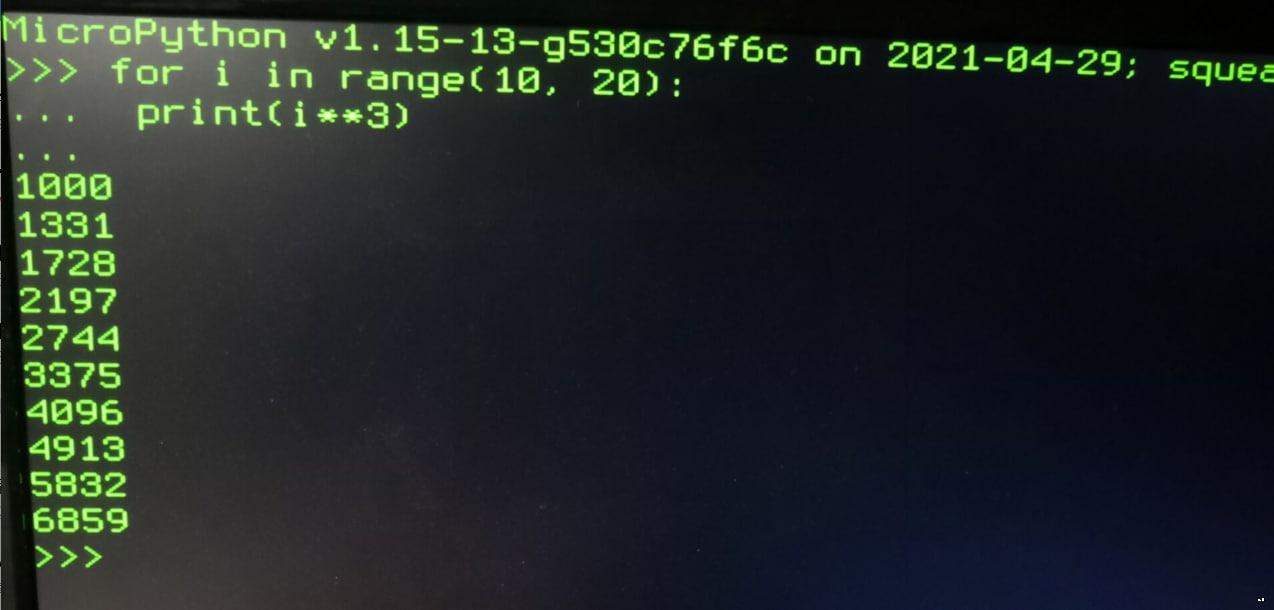

- MicroPython port

Misc

- Standard RISC-V toolchain and ASM/C programming for RV32IM Newlib

- Basic RISC-V tests

- CoreMark performance approx. 0.27 CoreMark/MHz

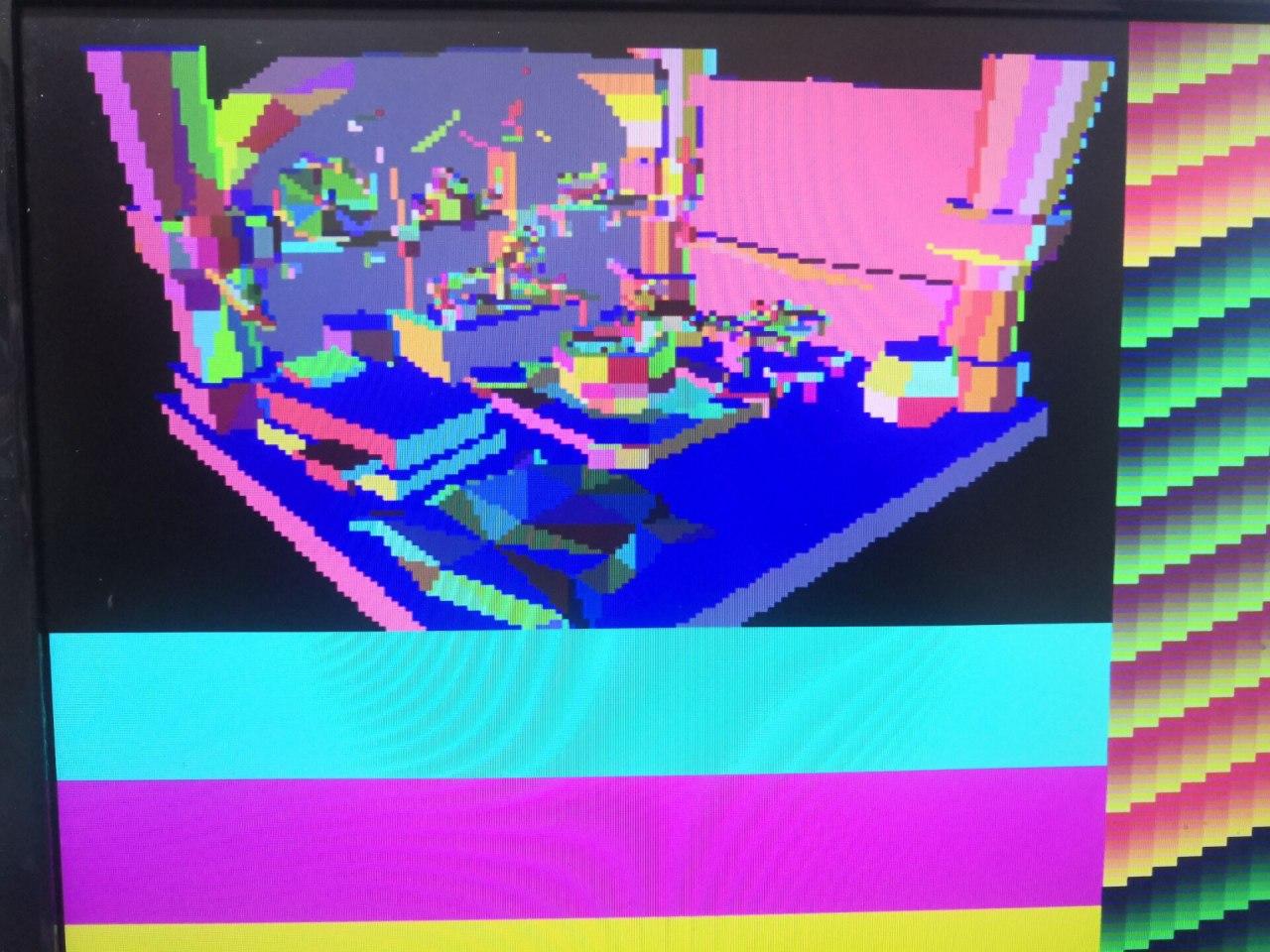

- Fancy but very slow soft renderer

- Bad Apple!! on LCD(low quality)

- Bad Apple!! on HDMI

Xilinx 7 series

- xc7a200t @ Nexys Video, main dev platform ref

- xc7z010 PL @ SqueakyBoard, previous main dev platform ref

- xc7z020 PL @ PYNQ-Z1 w/ extension PMOD module ref

- xc7k325t @ Memblaze PBlaze 3 w/ extension board ref

- xc7a100t @ Nexys A7 on USTC FPGAOL, SW/LED/UART/UARTBOOT Instructions

- Xilinx 7-series w/ Symbiflow (partial)

Xilinx Spartan 6

- xc6slx16 @ Nameless LED controller module

Others

Quick start

Build & run instructions

Free-as-in-freedom

Free software toolchain -- SymbiFlow(Vivado-free!)

At least you saw a fancy kernel panic.

It's hacky and dirty(TODO)

Use other RISC-V cores with Quasi SoC peripherals. Currently supports PicoRV32.

Hart Transplant

Linux kernel and busybox, 8 MB RAM is enough for everything.

Pingo soft renderer of Viking room, with testing color strips, on HDMI monitor.

Ported MicroPython, on HDMI monitor.

CoreMark benchmarking, serial port.

Many peripherals' code are based on other's work. If I miss something please point out.

HDMI module, modified

UART module, heavily modified

Computer Organization and Design, where everything started

GPL-V3