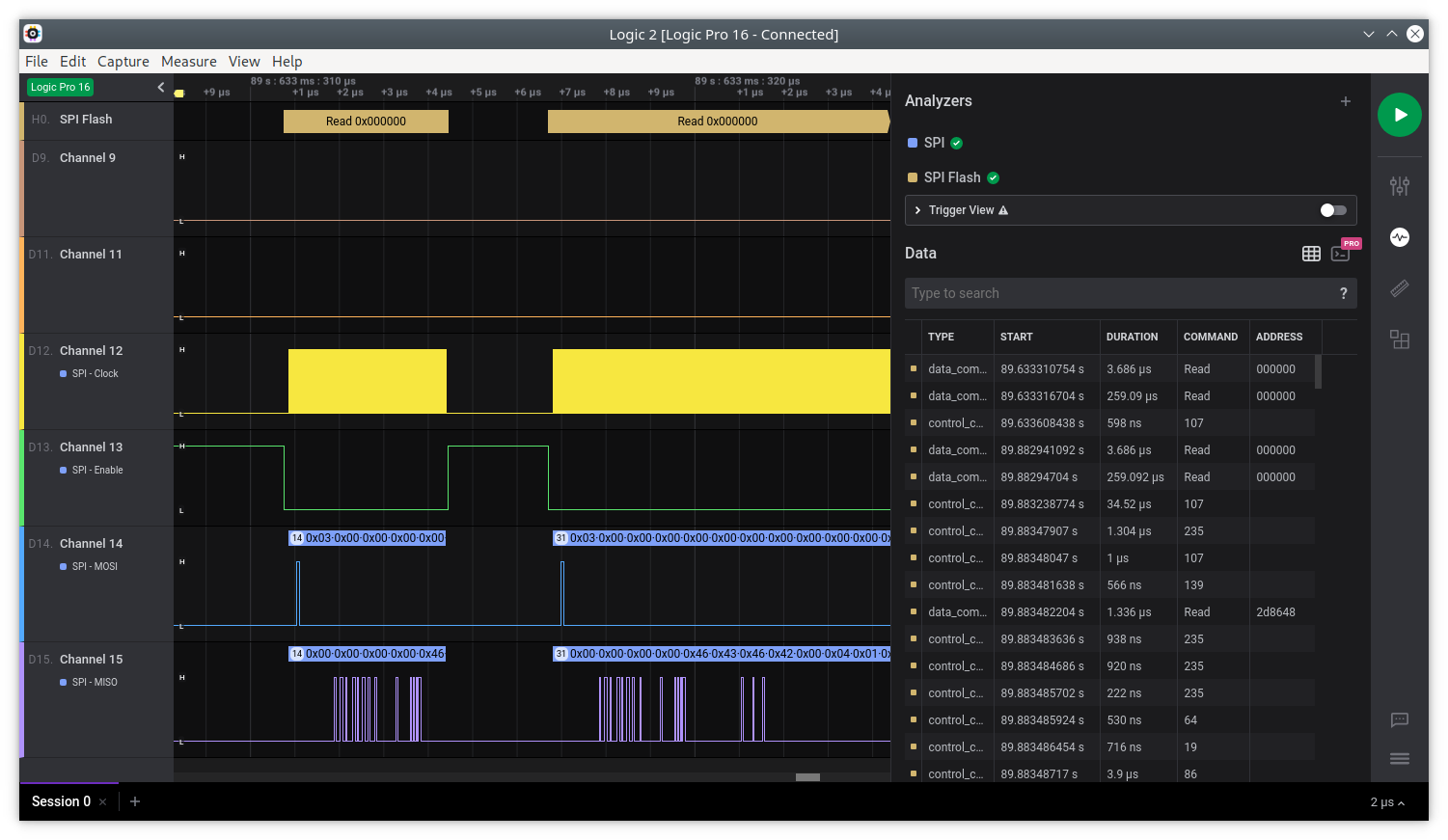

This is a basic high level analyzer for Saleae Logic 2 that interprets semi-standard SPI flash commands. The output can be limited by command type and data commands can also be limited by address. One can add the analyzer multiple times to get separate analysis tracks for different types of commands.

In Logic 2, click extensions on the right hand side.

Under the three dot, more menu, click Check for Updates then install the SPI Flash extension.

- Clone this repo locally.

- Under the three dot, more menu, click

Load Existing Extension...and then select the local repo location.

- Click the analyzers tab.

- Add a

SPIanalyzer and configure it for your capture. - Add a

SPI Flashanalyzer. - Set the

SPIanalyzer as the Input Analyzer. Min Address,Max AddressandDecode Levelare optional.- Change

Address Bytesto match

- Click the analyzers tab.

- Add a

Simple Parallelanalyzer. (You may need to search for it.) - Configure it for your capture.

- Set D0 to MOSI.

- Set D1 to MISO.

- Set D2 to IO2 (WP on 8 pin flashes usually.)

- Set D3 to IO3 (HOLD on 8 pin flashes usually.)

- Set D15 to CS (used to ignore extra clocks.)

- Set the clock to the clock pin with the correct edge set.

- Add a

SPI Flashanalyzer. - Set the

Simple Parallelanalyzer as the Input Analyzer. Min Address,Max AddressandDecode Levelare optional.- Change

Address Bytesto match

Note: When using Simple Parallel input, it is assumed the CS line goes high between parallel captures that are greater than 4 times the time separation of the closest clocks seen thus far. So, beware of spurious clocks and SPI transmissions that pause between bytes but leave CS low. This analyzer may incorrectly partition the transactions.